Устройство для сопряжения электронных вычислительных машин

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭЛЕКТРОННЫХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН, содержащее в каждом канале регистр сдвига, коммутатор, два элемента И и триггер контроля, «дединенный прямым и инверсным выходами соответственно с первыми входами первого и второго элементов И, причем вход регистра сдвига, первый информационный вход коммутатора , второй вход первого элемента И, и вход триггера являются соответствующими информационными выходом и входом устройства, управляющим входом и входом готовности устройства, второй информационный вход коммутатора канала соединен с выходом регистра сдвига того же канала, а выход - с входом регистра сдвига последующего канала, вход регистра сдвига первого канала соединен с выходом коммутатора последнего канала, отличающееся тем, что, с целью повыщения быстродействия устройства, в каждый его канал введен реверсивный счетчик, в каждый канал , кроме последнего, - триггер управления и третий элемент И, а в каждый канал , кроме первого и второго, - два элемента ИЛИ, причем вход установки реверсивного счетчика и первый вход установки в .единицу триггера управления каждого канала образуют соответствующий вход начальной установки устройства, выход реверсивного счетчика каждого канала является соответствующим адресным выходом устройства, в каждом канале прямой выход и вход установки в нуль триггера управления соединены соответственно с вторым входом и выходом второго элемента И, а инверсный выход и второй вход установки в единицу - соответственно с первым € входом и выходом третьего элемента И, (Л второй вход которого подключен к инверсному выходу триггера контроля, выходы первого и второго элементов ИЛИ подключены соответственно к суммирующему и вычитающему входам реверсивного счетчика , группы входов первого и второго элементов ИЛИ каналов подключены соответственно к выходам третьих и вторых элементов И всех предществующих каналов , суммирующий и вычитающий входы 05 реверсивного счетчика второго канала соединены соответственно с выходами третьего и второго элементов И первого канала. tC СО

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

Э(д1) G 06 F 3/04; G 06 F 15/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ;

К АВТОРСКОМУ(СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3486355/18-24 (22) 18.08.82 (46) 15.12.83. Бюл. № 46 (72) А. М. Заяц и С. А. Матвеев (53) 681. 14 (088.8) (56) 1. Авторское свидетельство СССР № 602950, кл. G 06 F 15/16, 1976.

2. Авторское свидетельство СССР № 903851, кл. G 06 F 3/04, 1980 (прототип). (54) (57) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭЛЕКТРОННЫХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН, содержащее в каждом канале регистр сдвига, коммутатор, два элемента И и триггер контроля, соединенный прямым и инверсным выходами соответственно с первыми входами первого и второго элементов И, причем вход регистра сдвига, первый информационный вход коммутатора, второй вход первого элемента И, и вход триггера являются соответствуюшими информационными выходом и входом устройства, управляющим входом и входом готовности устройства, второй информационный вход коммутатора канала соединен с выходом регистра сдвига того же канала, а выход — с входом регистра сдвига последующего канала, вход регистра сдвига первого канала соединен с выходом коммутатора последнего канала, отличающееся тем, что, с целью повышения быстроÄÄSUÄÄ 1061129 A действия устройства, в каждый его канал введен реверсивный счетчик, в каждый канал, кроме последнего, — триггер управления и третий элемент И, а в каждый канал, кроме первого и второго, — два элемента ИЛИ, причем вход установки реверсивного счетчика и первый вход установки в,единицу триггера управления каждого канала образуют соответствующий вход начальной установки устройства, выход реверсивного счетчика каждого канала является соответствующим адресным выходом устройства, в каждом канале прямой выход и вход установки в нуль триггера управления соединены соответственно с вторым входом и выходом второго элемента И, а инверсный выход и второй вход установки в единицу — соответственно с первым входом и выходом третьего элемента И, второй вход которого подключен к инверсному выходу триггера контроля, выходы первого и второго элементов ИЛИ подключены соответственно к суммирующему и вычитаюшему входам реверсивного счетчика, группы входов первого и второго элементов ИЛИ каналов подключены соответственно к выходам третьих и вторых элементов И всех предшествующих каналов, суммирующий и вычитающий входы реверсивного счетчика второго канала соединены соответственно с выходами третьего и второго элементов И первого канала.

1061129

Изобретение относится к вычислительíîil технике и может быть использовано, например, для организации высоконадежных однородных вычислительных систем обработки данных в реальном масштабе времени.

Известны устройства для сопряжения

ЭВМ в вычислительных системах, содержащие группу вычислительных машин (ВМ), группу коммутаторов и регистры сдвига (1).

Недостатками этих устройств являются ограниченные функциональные возможности, так как они не позволяют присвоить адреса отказавших BM резервным, в результате этого снижаются быстродействие и надежность вычислительной системы.

Наиболее близким к предлагаемому по технической сущности является устройство для сопряжения ЭВМ, соДержащее блок реконфигурации, включающий регистр состояний, соединенный входом с выходом генератора импульсов и первыми входами первого и второго счетчиков, а группой входов — с группой выходов группы элементов И, дешифратор, группу коммутаторов и группу каналов, каждый из которых состоит из регистра сдвига, блока коммутации, регистра номера ВМ, триггера контроля и элемента И, выходом соединенного с управляющим входом блока коммутации, а входами — с выходом триггера контроля и соответствующим управляющим входом устройства, первый информационный вход блока коммутации, выход регистра сдвига, вход триггера контроля и выход регистра номера ВМ каждого канала являются соответствующими информационными входом и выходом, входом готовности и адресным выходом устройства, входы регистров номера ВМ каналов соединены с выходом соответствующего коммутатора группы блока конфигурации, первые входы элементов И группы которого соединены с выходами триггера контроля соответствующих каналов, выход регистра сдвига каждого канала соединен с вторым информационным входом блока коммутации своего канала, а вход — с выходом блока коммутации предыдущего канала, выход блока коммутации последнего канала соединен с входом регистра сдвига первого канала.

В этом устройстве при отсутствии неисправных ВМ все триггеры контроля установлены в единичное положение, последовательно с частотой генератора импульсов подтверждаются адреса ВМ в регистрах адреса. Если какая-либо ВМ вышла из строя, соответствующий триггер контроля будет переведен в «нуль» и подтверждение адреса в соответствующем регистре адреса блокируется, а в следующие регистры адреса последовательно запишутся новые адреса на единицу меньше прежних адресов. Переключение BM из состава резервных в ра5

55 бочее состояние происходит за и тактов работы генератора импульсов, и время переключения будет тем больше, чем меньше адрес ВМ (2).

Недостаток известного устройства состоит в низком быстродействии переназначения адресов резервных ВМ при отказах рабочих ВМ.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство, содержащее в каждом канале регистр сдвига, коммутатор, два элемМта И и триггер контроля, соединенный прямым и инверсным выходами соответственно с первыми входами первого и второго элементов И, причем выход регистра сдвига, первый информационный вход комМуТатора, второй вход первого элемента И и вход триггера контроля являются соотвеТствующими информационными выходом и входом устройства, управляющим входом и входом готовности устройства, второй информационный вход коммутатора канйла соединен с выходом регистра сдвига того же канала, а выход — с входом регистра сдвига последующего канала, вход регистра сдвига первого канала соединен с выходом коммутатора последнего канала, в каждый его канал введен реверсивный счетчик, в каждый канал, кроме последне1o — триггер управления и третий элемент И, а в каждый канал, кроме первого и второго, — два элемента ИЛИ, причем вход установки реверсивного счетчика и новый вход установки в единицу триггера уПравления каждого канала образуют соответствующий вход начальной установки усТройства, выход реверсивного счетчика каждого канала является соответствующим адресным выходом устройства, в каждом канале прямой выход и вход установки в нуль триггера управления соединены соответственно с вторым входом и выходом второго элемента И, а инверсный выход и второй вход установки в единицу — соответственно с первым входом и выходом третьего элемента И,второй вход которого подключен к инверсному выходу триггера контроля, выходы первого и второго элемента ИЛИ подключены соответственно к суммирующему и вычитающему входам реверсивного счетчика, группы входов первого и второго элементов ИЛИ каналов подключены соответственно к выходам третьих и вторых элементов И всех предшествующих каналов, суммирующий и вычйтающий входы реверсивного счетчика второго канала соединены соответственно с выходами третьего и второго элементов И первого канала.

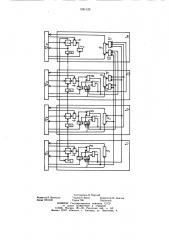

На чертеже представлена блок-схема устройства.

1 з

Блок-схема содержит каналы 1, включающие коммутаторы 2, регистры 3 сдвига, первый элемент И 4, триггер 5 контроля, триггер 6 управления, второй и третий элементы И 7 и 8, реверсивный счетчик 9, элементы ИЛИ 10 и 11 и ВМ 12.

Устройство работает следующим образом.

В исходном состоянии все ВМ 12 ис правны, часть из них являются рабочи а остальные — резервными.

В случае исправных ВМ 12 триггеры 5 находятся в нулевом состоянии и разрешают прохождение управляющего сигнала через элементы И 4 на коммутаторы 2. При необходимости передать сигнал ВМ 12 выдает на управляющий вход коммутатора 2 единичный сигнал и по его первому информационному входу выдает данные в цепь, образованную регистрами 3, и коммутаторами 2. Таким образом, по кольцу регистров 3 сдвига и коммутаторов 2 циркулирует информация, введенная "из ВМ 12 на соответствующие регистры 3. Каждой ВМ 12 присвоен адрес, опознаваемый ею в информационном сообщении, находящемся в регистре 3. При опоздании своего адреса

ВМ 12 читает и обрабатывает сообщение из соответствующего ей регистра 3 по заданной программе.

Резервные ВМ 12 в указанном процессе не участвуют. пока их адреса, записанные в счетчиках 9, не соответствуют адресам рабочих ВМ. 12. Как только в счетчик 9 какой-либо резервной ВМ 12 будет записан адрес какой-либо отказавшей рабочей машины, то резервная ВМ 12 включает программу обработки и участвует далее в работе системы так, как это делала отказавшая ВМ 12.

Если все ВМ 12 исправны, то на прямых выходах триггеров 6 установлены логические единицы, поэтому на выходах элементов И 7 и 8 находятся «нули», соответственно на выходах элементов ИЛИ 10 и 11 также «нули» и, следовательно, никаких изменений в счетчиках 9 не происходит, Предложим, что отказала одна из ВМ 12.

Тогда на инверсном выходе триггера 5 одновременного канала формируется нулевой

061129

4 сигнал (по команде системы контроля отказавшей ВМ 12), который блокирует элемент И 4, и возможность выдачи данных из отказавшей ВМ 12.На выходе элемента

И 7 оказывается «единица»,которая поступает на входы элементов ИЛИ 11 всех последующих каналов, и «единица» оказывается на вычитаюших входах соответствующих счетчиков 9, содержимое которых одновременно уменьшается на единицу. В то же время «единица» с выхода элемента И 7 поступает на нулевой вход триггера 6 и устанавливает его в «нуль». Следовательно, «нуль» оказывается на выходе элемента И 7 и на входах и выходах соответствующих элементов ИЛИ 11. Таким образом, адрес последней рабочей ВМ 12 оказывается в счетчике 9, соответствующем первой резервной ВМ 12. Так как необходимо, чтобы резервные ВМ 12 всегда по возможности оставались в составе резервных, то после устранения неисправности в ВМ она вновь будет включена в состав рабочих.

При этом триггер 5 установится в «нуль» и на выходе элемента И 8 появится «единица», которая поступит на входы элементов ИЛИ 10 всех последующих каналов и на единичный вход триггера 6. С выходов элемента ИЛИ 10 «единица» поступит на суммирующие входы соответствующих счетчиков 9, и их содержимое увеличится на единицу. «Единица», поступившая на единичный вход триггера 6, установит его в «единицу». Тогда на выходе элемента И 8 и элемента ИЛИ 10 окажутся «нули», Те

ВМ 12, у которых сменился адрес, осуществляют соответствующие операции по переходу на работу по новым, если этого требует процесс, программ, определенным новыми адресами, и работа системы продолжается.

Таким образом, в устройстве за счет одновременного переназначения адресов входов при выходе из строя одной из вычислительных машин повышается быстродействие и сокращаются непроизводительные простои вычислительной системы по сравнению с прототипом, в котором время переназначения зависит от количества рабочих и номера вышедшей из строя ВМ.

1061129

Редактор К. Волощук

Заказ 10041/51

Составитель В. Вертлиб

Техред И. Верес Корректор М. Демчик

Тираж 706 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4