Устройство для исправления одиночных и обнаружения многократных ошибок

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОДИНОЧНЫХ И ОБНАРУЖЕНИЯ МНОГОКРАТНЫХ ОШИБОК, содержащее последовательно соединенные входной накопитель и первый ключ, выход которого подсоединен к дополнительному входу входного накопителя, сумматор по модулю два, первый вход которого подключен к выходу накопителя, последовательно соединенные второй ключ, блок обнаружения ошибок и третий ключ, последовательно соеди-; ненные триггер и четвертый ключ, и пятый ключ, отличающееся тем, что, с целью уменьшения времени исправления и обнаружения ошибок, введены последовательно соединенные динамический триггер, счетиг/ чик и дешифратор, элемент ИЛИ, шестой ключ и дешифратор базового остатка, входы которого подключены к соответствуюш ,им выходам блока обнаружения ошибок, а выход подсоединен ко второму входу сумматора по модулю два, выход которого через шестой ключ подсоединен к дополнительному входу входного накопителя , ко второму входу шестого ключа подключен первый выход дешифратора, второй выход которого подсоединен ко. второму входу первого ключа и первому входу второго ключа, второй вход которого объединен со вторым входом четвертого ключа и подсоединен к выходу накопителя, третий выход дешифратора через третий ключ подсоединен к первому входу триггера , второй вход которого объединен со вторым входом счетчика, первым входом динамического триггера и является входом начальной установки, четвертый выход дешифратора через последовательно соединенные пятый ключ и элемент ИЛИ подсоединен ко второму входу динамического триггера , при этом первый, выход триггера подсоединен ко второму входу элемента ИЛИ, а второй выход - ко второму входу пятого ключа.

„„SU„„1061275 A

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТ ИЧЕСНИХ

РЕСПУБЛИК

З бу Н 04 L 1/10

-" .,"; .щу

ОПИСАНИЕ ИЗОБРЕТЕНИЯ """: !

"" ЭВИЗа

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ, ГОСУДАРСТВЕННЫЙ НбМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3425425/18-09 (22) 21.01.82 (46) 15.12.83. Бюл. № 46 !

72) Б. Г. Бондарев, М. М. Голубчик, С. А. Скотарь и А. В. Федотов (53) 621.374.32 (088.8) (56), 1. Авторское свидетельство СССР

¹ 566375, кл. Н 04 L 1/10, 1976.

2, Авторское свидетельство СССР № 196441, кл. Н 04 L 1/10, 1966 (прототип) .

Вых/// (54) (57) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОДИНОЧНЫХ И ОБНАРУЖЕНИЯ

МНОГОКРАТНЫХ ОШИБОК, содержащее последовательно соединенные входной накопитель и первый ключ, выход которого подсоединен к дополнительному входу входного накопителя, сумматор по модулю два, первый вход которого подключен к выходу накопителя, последовательно соединенные второй ключ, блок обнаружения ошибок и третий ключ, последовательно соединенные триггер и четвертый ключ, и пятый ключ, отличающееся тем, что, с целью уменьшения времени исправления и обнаружения ошибок, введены последовательно соединенные динамический триггер, счет&I

Sx ii чик и дешифратор, элемент ИЛИ, шестой ключ и дешифратор базового остатка, входы которого подключены к соответствующим выходам блока обнаружения ошибок, а выход подсоединен ко второму входу сумматора по модулю два, выход которого через шестой ключ подсоединен к дополнительному входу входного накопителя, ко второму входу шестого ключа подключен первый выход дешифратора, второй выход которого подсоединен ко. второму входу первого ключа и первому входу второго ключа, второй вход которого объединен со вторым входом четвертого ключа и подсоединен к выходу накопителя, третий выход дешифратора через третий ключ подсоединен к первому входу триггера, второй вход которого объединен со Я вторым входом счетчика, первым входом динамического триггера и является входом начальной установки, четвертый выход дешифратора через последовательно соединенные пятый ключ и элемент ИЛИ подсоединен ко второму входу динамического триг- Я гера, при этом первый. выход триггера подсоединен ко второму входу элемента ИЛИ, ф а второй выход — ко второму входу пятого ключа.

С5Вь

°

1061275

Изобретение относится к технике передачи данных и может использоваться в устройствах повышения достоверности информации.

Известно устройство для исправления одиночных и обнаружения многократных ошибок, содержащее последовательно соединенные элемент ИЛИ, накопитель, сумматор по модулю два и блок обнаружения ошибок, выход которого подсоединен ко второму входу накопителя, первому входу ключа и первому входу датчика одиночных

О ошибок, выход которого подсоединен ко второму входу сумматора по модулю два, выход которого подсоединен ко второму входу ключа, выход которого подсоединен к первому входу элемента ИЛИ, второй вход которого является входом устройства (1).

Недостатком данного устройства для исправления одиночных и обнаружения многократных ошибок является большое количество циклов для исправления одиночной ошибки.

Наиболее близким к предлагаемому является устройство для исправления одиночных и обнаружения многократных ошибок, содержащее последовательно соединенные входной накопитель и первый ключ, выход 25 которого подсоединен к дополнительному входу входного накопителя, сумматор по модулю два, первый вход которого подключен к выходу накопителя, последовательно соединенные второй ключ, блок обнаружения ошибок и третий ключ, после- 30 довательно соединенные триггер и четвертый ключ, и пятый ключ, вход которого подсоединен ко входу элемента запрета, а выход подключен ко входу триггера и выходу элемента памяти, ко входу которого подключен выход третьего ключа, делитель, З5 выход которого подсоединен ко второму входу сумматора по модулю два, выход которого подсоединен ко второму входу блока обнаружения ошибок и входу п-разрядного регистра, выход которого подсоединен д0 ко второму входу четвертого ключа (2).

Однако это устройство для исправления одиночных и обнаружения многократных ошибок характеризуется большим количеством циклов, равным п + 1, для исправления одиночной ошибки. 45

Цель изобретения — уменьшение времени исправления и обнаружения ошибок.

Поставленная цель достигается тем, что в устройство для исправления одиночных н обнаружения многократных ошибок, содержащее последовательно соединенные 50 входнои накопитель и первыи ключ, выход которого подсоединен к дополнительному входу входного накопителя, сумматор по модулю два, первый вход которого подключен к выходу накопителя, последовательно соединенные второй ключ, блок обнаружения ошибок и третий ключ, последовательно соединенные триггер и четвертый ключ, и пятый ключ, введены последова2 тельно соединенные динамический триггер, счетчик и дешифратор, элемент ИЛИ, шестой ключ и дешифратор базового остатка, входы которого подключены к соответствующим выходам блока обнаружения ошибок, а выход подсоединен ко второму входу сумматора по модулю два, выход которого через шестой ключ подсоединен к дополнительному входу входного накопителя, ко второму входу шестого ключа подключен первый выход дешифратора, второй выход которого подсоединен ко второму входу первого ключа и первому входу второго ключа, второй вход которого объединен со вторым входом четвертого ключа и подсоединен к выходу накопителя, третий выход дешифратора через третий ключ подсоединен к первому входу триггера, второй вход которого объединен со вторым входом счетчика, первым входом динамического триггера и является вторым входом начальной установки, четвертый выход дешифратора через последовательно соединенные пятый ключ и элемент ИЛИ подсоединен ко второму входу динамического триггера, при этом первый выход триггера подсоединен ко второму входу элемента ИЛИ, а второй выход — ко второму входу пятого ключа.

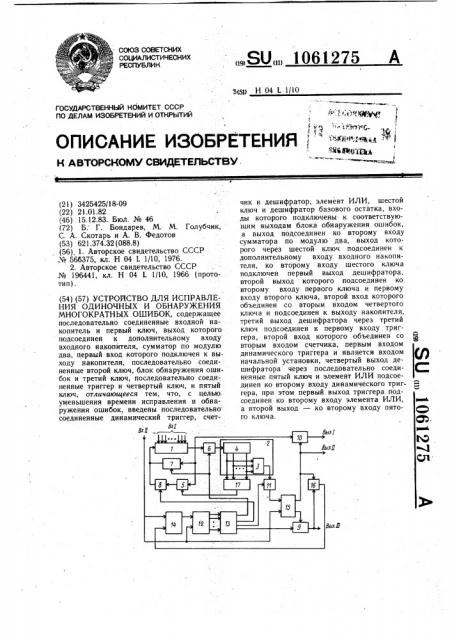

На чертеже представлена структурная электрическая схема устройства для исправления одиночных и обнаружения многократных ошибок.

Устройство для исправления одиночных и обнаружения многократных ошибок содержит входной накопитель 1, блок 2 обнаружения ошибок, содержащий элемент

ИЛИ-НЕ 3 и делитель 4, сумматор 5 по модулю два, ключи 6 — 11, счетчик 12, дешифратор 13, динамический триггер 14, триггер 15, элемент ИЛИ 16, дешифратор

17 базового остатка.

Устройство для исправления одиночных и обнаружения многократных ошибок работает следующим образом.

Со входа 1 принятая комбинация параллельным кодом записывается в накопитель 1.

Одновременно на вход II поступает сигнал, по которому в исходное состояние устанавливается счетчик 12 и триггер 15 и запускается динамический триггер 14, вырабатывающий на своем выходе последовательность импульсов с частотой выше скорости телеграфирования в четыре раза. Счетчик

12 осуществляет подсчет импульсов, поступающих на его вход, а дешифратор 13 выделяет четыре состояния счетчика 12, соответствующие четырем циклам работы устройства и выдает управляющие сигналы на ключи 8, 6, 11, 9, 7.

Процесс исправления одиночных и обнаружения ошибок большей кратности происходит на четыре цикла. В первом цикле сигналом от дешифратора 13 открыты ключи 6 и 7. Поэтому кодовая комбинация из накопителя 1 последовательным кодом

1061275

Составитель Т. Поддубняк

Редактор Н. Кнштулинец . Техред И. Верес Корректор А. Дзятко

Заказ 10060 58 Тираж 677 Подписное

ВНИИПИ Государственного комитета СССР по делам Изобретений и открытий

1 1 3035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

3 поступает в блок 2 обнаружения ошибок, где осуществляется деление этой комбинации на образующий полином и одновременно вновь записывается через ключ 7 в накопитель 1.

Если в первом цикле деления ошибка 5 яе обнаружена, то на выходе блока 2 обнаружения ошибки будет нулевой остаток, а на выходе элемента ИЛИ-НЕ 3 будет «1»

При этом во втором цикле открывается ключ 11 и «1» с его выхода устанавливает 10 триггер 15 в единичное состояние, при котором открывается ключ 10. Кодовая комбинация из накопителя через открытый ключ 10 поступает на выход 1 устройства.

Сигнал с выхода II может использоваться как команда «Разрешение ввода» для счи- 15 тывания на входы очередной кодовой ийформации.

Если в первом цикле обнаружена ошибка, то на выходе элемента ИЛИ-НЕ 3 будет «О», при этом ключ 10 будет закрыт, а во втором цикле осуществляется 20 исправление одиночной ошибки.

Известно, что вид остатка от деления (синдрома) кодовой комбинации на образующий полином соответствует номеру ис- 25 кажен ного разряда кодовой комбинации, одновременно после цикла деления происходят сдвиги синдрома. Это обстоятельство используется для исправления ошибки. Во втором цикле ключи 6 и 7 закрыты, а ключ

8 открыт. Перезапись в накопитель 1 осу-30 ществляется через сумматор 5 по модулю два. На второй вход сумматора 5 по модулю два подан выход дешифратора 17 базового остатка. Если одиночная ошибка произошла в i-ом разряде кодовой комбинации, то íà i-ом такте, во втором цикле, 35 на выходе дешифратора 17 базового остат. ка появится единица, которая инвертирует искаженный символ кодовой комбинации, 4 в результате чего в накопитель 1 будет переписана исправленная комбинация.

В третьем цикле ключи 6 и 7 открыты, а остальные закрыты. Здесь происходит проверка наличия ошибки кратности более едйницы в исправленной кодовой комбинации и одновременная ее перезапись в накопитель 1. Если ошибка не обнаружена, то на выходах блока 2 обнаружения ошибок будет нулевой остаток, а на выходе ИЛИ-НЕ 3 появится «1», которая, как и в предыдущем случае, через открытый ключ 11 устанавливает в единичное состояние триггер 15, в результате чего ключ 10 открывается, и в четвертом цикле кодовая комбинация выводится на выход 1 устройства.

В-том случае, если имеет место ошибка кратности более единицы, то к началу четвертого цикла блок 2 обнаружения ошибок выдает не нулевой остаток. Следовательно, ключ 10 оказывается закрыт и запрещает вывод комбинации на выход I.

Ключ 9 открыт, а так как на его вход поступает «1» с выхода триггера 15 (триггер находится в исходном состоянии), то на выходе 111 появляется сигнал «1», используемый как сигнал «Ошибка». Так как единичное состояние триггера 15 или

«1» на выходе ключа 9 соответствует окончательному решению (наличие или отсутствие ошибки), то сигнал с выхода элеменна ИЛИ 16, поступающий на установочный вход динамического триггера 14, останавливает последний до поступления следующей кодовой комбинации.

Технико-экономическая эффективность устройства для исправления одиночных и обнаружения многократных ошибок заключается в том, что оно позволяет в случае использования циклических кодов в - раз уменьшить время анализа принятой кодовой комбинации.