Устройство для сопряжения эвм с дискретными датчиками

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С. ДИСКРЕТНЫМИ ДАТЧИКАМИ, содержащее коммутатор, входы первой группы которого являются входами группы устройства, а выход соедине с первым входом первого триггера, выход которого соединен с первым входом первого блока памяти, входы группы которого соединены с соответ-гствующими входами второй группы коммутатора, входами группы блока согласования и выходами счетчика, вход которого соединен с первым выходом блока синхронизации, второй выход которого соединен с вторым входом первого триггера, а третий выход - с вторым входом первого блока памяти и первым входом второго триггера, второй вход которого соединен с выходом блока согласова- . ния, а выход - с первым входом блока синхронизации и входом блока согласования, выходы группы которого являются выходами устройства, второй вход блока синхронизации является первым входом устройства, отличающеес я тем, что, с целью расширения области применения устройства путем обеспечения различных режимов работы, в него введены второй блок памяти, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ- Н и элемент И, выход которого соединен с третьим входом второго i триггера, а первый и второй входы соединены с соответствующими выхо (Л С дами первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, первые входы которых соединены с выходом первого триггера, а вторые входы являются вторым входом устройства, третий вход элемента И соединен с пе)вым выходом второго блока памяти, второй выход которого соединен с треть-: им входом второго элемента ИСКЛЮЧАЮ ЩЕЕ ИЛИ-НЕ, входы второго блока N5 памяти соединены с соответствующими выходами счетчика, выход первого эо блока памяти соединен с третьим входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-ЦЕ, : ю

(19) (И), СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

3(51) 0 06 Р 3/04

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3492772/18-24 (22) 1;7; 09 ° 82 (4 6 ) 2;3, 1,2 ° 8,3 ° Бщл, 9 4 7 . (7 2 ) В,Д, Глущенко, ф,;П., Жабеев, ;В И . Корольхевич, 3, h . Кротевич н,В, (Моро зов (7 1 ) Киевское проектно- конструкторское бюро автоматизированных систем, управления (5 3 ) 6 8 1, 3 2 7, 1 (0 8 8, 8 ) (5 6 ) ;1 о Авторское свидетельство СССР

9 8 4 2 7 7 5, кд, G 0 6 F 3 / 0 4, 1 9 7;9 о

;2 . Авторское свидетельство СССР

)) 8 3 0 3 6 7, кп С 0 6 F 3 / 0 4, 1 9 7 9 (прототип) . (5 4 ) (57 ) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ

ЭВМ. С ДИСКРЕТНЫМИ ДАТЧИКАМИ, содержащее коммутатор, входы первой группы которого являются входами группы устройства, а выход соединен с первым входом первого триггера, выход которого соединен с первым входом первого блока памяти, входы группы которого соединены с соответ-. ствующими входами второй группы коммутатора, входами группы блока согласования и выходами счетчика, вход которого соединен с первым выходом блока синхронизации, второй выход которого соединен с вторым входом первого триггера, а третий выход — с вторым входом первого блока памяти и первым входом второго триггера, второй вход которого соединен с выходом блока согласова- - ния, а выход - с первым входом блока синхронизации и входом блока согласования, выходы группы которого являются выходами устройства, второй вход блока синхронизации является первым входом устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения устройства путем обеспечения различных режимов работы, в него введены второй блок памяти, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ. НУ и элемент И, выход которого соединен с третьим входом второго триггера, а первый и второй входы соединены с соответствующими выходами первого и второго элементов

ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, первые входы которых соединены .с выходом первого триггера, а вторые входы являются вторым входом устройства, третий вход элемента И соединен с пе1)вым выходом второго блока памяти, второй выход которого соединен с третьим входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, входы второго блока памяти соединены с соответствующими выходами счетчика, выход первого блока памяти соединен с третьим входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, 1062682

Изобретение относится к вычислительной технике и может быть применено в автоматизированных системах управления для приема информации от дискретных датчиков.

Известно устройство для сопряжения, содержащее коммутатор, дешифратор адреса, счетчик адреса, блок синхронизации, схему. сравнения, первый и второй регистры, первый и второй шифраторы flj

Нецостатком устройства является его сложносту

Наиболее близким по технической сущности к изобретению является устройство для сопряжения электронной вычислительной машины с дискретными датчиками, содержащее коммутатор, счетчик, блок памяти, схему сравненил, первый и второй триггеры, блок синхронизации и блок согласования с ЭВМ (2)

Педостаткогл известного устройства является отсутствие режима маскировали r, позволяющего прерывать программу по предварительно заданным входам, и режимов, обеспечивающих прорывание программ при заданных условиях состояния входных сигналов,,т.,е. по заданному переходу логиreñrrîãî уровня на соответствующем вход(-:., Полью изобретения является расширение области применения устройcòàà путем обеспечения различных режимов рабстЬ|.

Поставленная цель достигается тем, что в устройство для сопряжения

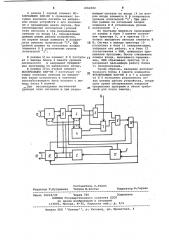

ЭВМ с дискретными датчиками, содержащее коммутатор, входы первой группы которого являются входами группы устройства, а выход соединен с первым входом первого триггера, выход которого соединен с первым входом первого блока памяти, входы группы которого соединены с соответствующими входами второй группы коммутатора, входами группы блока согласования и выходами счет-1ика, вход которого соединен с первым выходом блока синхронизации, второй выход которого соединен с вторым входом первого триггера, а третий выход — с вторым входом первого блока памяти и первым входом в "îðîãî триггера, второй вход которого соединен с выходом блока согласования, а выход — с первым входом блока синхронизации и входом блока согласования, выходы группы которого являются выходами устройства, второй вход блока синхронизации является первым входом устройства, введены второй блок памяти, первый и второй элегггенты ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ и элемент И, выход которого соединен с третьим входом второго триггера, а первый и второй входы соединены с соответствующими выходами первого и второго элеменов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, первые вхокоторых соединены с выходом первого триггера, а вторые входы яв5 ляются вторым входом устройства, третий вход элемента И соединен с первым выходом второго блока памяти, второй выход которого соединен с третьим входом второго элегО мента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, входы второго блока памяти соединены с соответствующими входами счетчика, выход первого блока памяти соединен с третьим входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, На чертеже представлена функциональная схема устройства для сопряжения ЭВМ с дискретными датчикаЖ о

Устройство содержит коммутатор 1, счетчик 2, первый блок 3 памяти, второй блок 4 памяти, первый вход

5, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ б. и 7, элемент И 8, первый и второй триггеры 9 и 10, блок ll синхронизации, блок 12 согласования, входы 13 группы, второй вход 14, выходы 1;5.

Устройство работает следующим обр.аз ом.

Установку устройства в исходное состояние производят путем загрузки блоков 3 и,4, В блок 3 памяти загружается информация об исходном состоянии каждого входа, в блок 4

З5 памяти — информация о состоянии бита маски и бита условий по каждому входу.

Блок 1.1 синхронизации тактируется от ЭВМ по входу 5 и по каждому

4Q входному тактовому импульсу формиРует три последовательных выходных импульса.

По первому импульсу, поступающему на вход счетчика 2, устанавли45 вается код, по которому в коммутаторе 1 производится выбор соответствующего входа, а на выходах блоков 3 и 4 устанавливаются соответственно код состояния выбранного канала, записанный в предыдущем цикле опроса и коды состояний бита маски и бита условиЯ, По второму импульсу производится запись входного сигнала в триггер

9, после чего элементами ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ б и 7 и элементом И 8 производится сравнение уровня этого сигнала с его уровнем в предыдущем цикле опроса (режим 1 ), анализ состояний бита маски (режимИ )

6О и бита условий (режим Щ). Возможно использование сочетаний режима 1 и режима П1, при котором входной сигнал сравнивается с битом условий и его состоянием в преды65 дущем цикле опроса.

1062

Составитель С. Гапич

Техред N.Êoñòèê

Корректор В.Гирняк

Редактор,Т,Кугрышева ч

Заказ 10218/49 Тираж 706 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Филиал ППП Патент, у Ужгород, ул, Проектная, 4

B режиме I первый элемент ИСКЛ ОЧАЮЩЕЕ ИЛИ-НЕ 6 сравнивает текущее значение сигнала на выбранном входе устройств с его значением в предыдущем цикле опросао При несовпадении логических уровней этих сигналов и при разрешающем сигнале по входу 14, опрецеляющем данный режим работы устройства, на первом входе элемента И появля ется уровень логической "1;, При данном режиме на остальных входах элемента И 8 установлены уровни логической 1 .

В режиме Р на элемент И 8 поступа- g ет с выхода блока 4 памяти уровень логического и запрещает прерывание программы по выбранному входу

В режиме Ш на второй элемент

ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 7 поступает текущее значение сигнала на выбранном входе устройства и значение соответствующего бита условия с выхода блока 4 памяти

При несовпадении логических уровней этих сигналов и при разре682 4

Ю шающем сигнале по входу 14 на вто- ром входе элемента И 8 появляется уровень логической 1; . При данном режиме на остальных входах элемента И 8 установлены уровни логической 1;

По третьему импульсу производится запись в блок 3 памяти состояния триггера 9, а. в триггер 10 запись выходного сигнала элемента И

;8, Сигнал с выхода триггера 10 поступает в блок 11 синхронизации, запрещая его работу, и в блок 12 согласования с ЭВМ, инициируя прерывание програмМ. После считывания номера входа, вызвавшего прерывание, ЭВМ сбрасывает триггер 10 и разрешает дальнейшую работу блока 11 синхронизацни.

Таким образом, введение дополнительного блока 4 памяти элементов

ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 6 и 7 и элемента И 8 позволяет. реализовать новые режимы работы устройства, сокра. щает время обслуживания запросов прерывания программ и объем требуемой для этого памяти