Устройство для деления двоичных чисел на три

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО Д31Я ДЕЛЕНИЯ ДВОИЧНЫХ ЧИСЕЛ НА ТРИ, содержащее регистр делимого и (п - 2) блоков формированиа разрядов частного, причем каждый блок формирования разряда частного содержит первый элемент И и первый элемент ИЛИ, первый вход которого соединен с выходом первого элемента И данного блока формирования разряда частного, отличающееся тем, что, с целью повышения быстродействия, оно содержит дешифратор, а каждый блок формирования разряда частного содержит три элемента НЕ, второй, третий, четвертый и пятый элементы И,второй и третий элементы ИЛИ, причем выход каждого разряда с первого по ((п-2) -и регистра делимого соединен с входом первого элемента НЕ и первыми входами первого, второго и третьего элементов И соответствующего блока формирования разряда частного, в котором выход первого элемента НЕ соединен с первыми входами четвертого и пятого элементов И, выход второго элемента НЕ соединен с вторыми входами первого, второго и пятого элементов И, вход второго элемента НЕ подключен к вторым входам. третьего и четвертого элементов И, выход третьего элемента НЕ соединен с третьими входами второго, третьего и четвертого элементов И, вход третьего элемента НЕ соединен с третьими входами первого и пятого элементов И, второй и третий входы первого элемента ИЛИ соединены с выходами третьего и четвертого элементов И, входы второгоэлемента . ИЛИ соединены с выходами третьего и пятого элементов И, входы третьего элемента ИЛИ соединены с выходами второго и четвертого элементов И, выход первого элемента ИЛИ каждого (Л блока формирования разряда частного соединен с соответствующей выходной шиной частного, выходы (и- 1)-го и П-го разрядов регистра делимого подключены к входам дешифратора, первый выход которого соединен с : (п- 1) -и выходной шиной частного, а второй и третий выходы подключены к входам соответственно второго и третьего элементов НЕ (ti - 2) -го блока формирования разряда частного., входы второго и третьего элементов НЕ каждого блока формирования разряда частного подключены к выходам соответственно второго и третьего элементов ИЛИ последугацего блока формирования разряда частного, выходы второго и третьего элементов ИЛИ первого блока формирования частного соединены с выходными шинами остатка.

(19) (11) СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

3(59 G 06 F 7 52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ. ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К ABTOPCHOMY .СВИДЕТЕЛЬСТВУ (21) 3393225/18-24 (22) 11.02.82 (46 ) 23.12.83. Вюл. Р 47 (72) В.A.Ãðà÷åâ, В.В.Королев, В.II.Ñåìåíîâ и A.B.Ãðå÷óõèí (53) 681.325(088.8) (56) 1. Авторское свидетЕльство СССР

9 5 06853, кл.- G F 7/52, 1974.

2. Авторское свидетельство СССР

М 758153, кл. G 06 F 7/52, 1978 (прототип). (54)(57) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ

ДВОИЧНЫХ ЧИСЕЛ HA ТРИ, содержащее регистр делимого и (n — 2) блоков формирования разрядов частного, причем каждый блок формирования разряда частного содержит первый элемент

И и первый элемент ИЛИ, первый вход которого соединен с выходом первого элемента И данного блока формирования разряда частного, о т л и ч а— ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит дешифратор, а каждый блок формирования разряда частного содержит три элемента НЕ, второй, третий, четвертый и пятый элементы И, второй и третий элементы ИЛИ, причем выход каждого разряда с первого по (и -2) -й регистра делимого соединен с входом первого элемента НЕ и первыми входами первого, второго и третьего элементов И соответствующего блока формирования разряда частного, в котором выход первого элемента НЕ соединен с первыми входами четверто го и пятого элементов И, выход вто-;рого элемента НЕ соединен с вторыми входами первого, второго и пятого элементов И, вход второго элемента НЕ подключен к вторым входам. третьего и четвертого элементов И, выход третьего элемента НЕ соединен с третьими входами второго, третьего и четвертого элементов Й, вход третьего элемента HE соединен с третьими входами первого и пятого элементов И, второй и третий входы первого элемента ИЛИ соединены с выходами третьего и четвертого элементов И, входы второго элемента

ИЛИ соединены с выходами третьего и пятого элементов И, входы третьего элемента ИЛИ соединены с выходами второго и четвертого элементов И, со выход первого элемента ИЛИ каждого блока формирования разряда частного соединен с соответствующей выходной шиной частного, выходы (n — 1) -го и tl-го разрядов регистра делимого подключены к входам дешифратора, первый выход которого соединен с (n- 1) -й выходной шиной частного, а второй и третий выходы подключены к входам соответственно второго и третьего элементов НЕ (5 — 2) -го блока формирования разряда частного„ входы второго и третьего элементов

НЕ каждого блока формирования разря- да частного подключены к выходам соответственно второго и третьего элементов ИЛИ последующего блока формирования разряда частного, выхо- ды второго и третьего элементов ИЛИ первого блока формирования разряда частного соединены с выходными шина- ф», ми остатка.

1062690

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах.

Известиo устройство для деления двоичных чисел на три, содержащее

q/2 однотипных логических схем, каждая из KoTopblx содержит двухразрядный регистр делимого, двувходовый дешифратор, логический блок, реализующий логические выражения определения значений двух разрядов и двух функций переноса f1) .

Это устройство имеет большие аппаратурные затраты, .связанные с применением й/2 дешифраторов.

Наиболее близким по технической сущности к предлагаемому является устройство для деления двоичных чисел í" три (2), содержащее регистр да итого и (q — 1) блоков формирова- 20 ния частного одноразрядных вычитателей (l1 — число разрядов делимого)1 связанных последовательно, каждый из которых состоит из полусумматора, элемента сложения по модулю два, 25 элемента И и элемента ИЛИ, причем выходы разрядов регистра делимого соединены с входами соответствующих одноразрядных вычитателей, выходы которых подключены к выходным шинам QQ устройства. Это устройство имеет сравнительно невысокое быстродействие

Целью изобретения является повышение быстродействия устройства.

Указанная цель достигается тем, что н устройство для деления двоичных чисел на три, содержащее регистр делимого и (n — 2) блоков формирования частного, причем каждый блок формирования разряда частного соцержит первый элемент И и первый элемент ИЛИ, первый вход которого соединен с выходом первого элемента

H да:-i.ного блока формирования разряда частного, внсдены дешифратор, 45 а каждый блок формирования разряда частнрго — три элемента HE второй, третий, четвертый и пятый элементы

И, второй и третий элементы ИЛИ, причем выход каждого разряда с пер- 50 ного по (и- 2) -й регистра делимого соединен с входом первого элемента

HE и первыми входами первого, второго и третьего элементов И соответствующего блока формирования разряда 55 частного, в котором выход первого элемента НЕ соединен с первыми входами четвертого и пятого элементов

И, выход второго элемента НЕ соединен с вторыми входами первого, вто- 60 рого и пятого элементов И, вход второго элемента НЕ подключен к вторым входам третьего и четвертого элементов И, выход третьего элемента

HE соединен с третьими входами второго, третьего и четвертого элементов

И, вход третьего элемента НЕ соединен с третьими входами первого и пятого элементов И, второй и третий входы первого элемента ИЛИ соединены с выходами третьего и четвертого элементов И, входы второго элемента

ИЛИ соединены с выходами третьего и пятого элементов И, входы третьего элемента ИЛИ соединены с выходами второго и четвертого элементов И, выход первого элемента ИЛИ каждого блока формирования разряда частного соединен с соответствующей выходной шиной частного, выходы (п -1) -го и р-го разрядов регистра делимого подключены к входам дешифратора, первый выход которого соединен с (и — 1) -й выходной шиной частного, а второй и третий выходы подключены к входам соответственно второго и третьего элементов HE (h -2) -го блока формирования разряда частного, входы второго и третьего элементов

НЕ каждого блока формирования разряда частного подключены к выходам соответственно второго и третьего элементов ИЛИ последующего блока формирования разряда частного, выходы второго и третьего элементов

ИЛИ первого блока формирований разряда частного соединены с выходными шинами остатка.

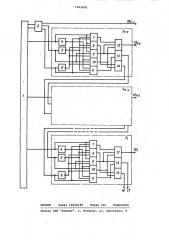

На чертеже представлена схема устройства для деления двоичных чисел на три.

Устройство содержит регистр 1 делимого, дешифратор 2, (h — 2) блоков 3 формирования разряда частного, каждый из которых содержит элементы

НЕ 4 — 6, элементы И 7 — 11, элементы ИЛИ. 12 - 14. Выходами устройства являются выходные шины 15 и шины

16 и 17 остатка.

Устройство работает следующим образом.

Делимое записывается в регистр 1

Два,старших разряда регистра 1 анализируются дешифратором 2, на первом выходе которого формируется единица при наличии единицы на выходах обоих старших разрядов регистра 1.

На втором выходе формируется единица при наличии единицы только на выходе И -ro разряда регистра 1.

На третьем выходе формируется единица при наличии единицы на выходе (Yl - 1) -го разряда регистра. Первый выход,цешифратора 2 является (И вЂ” 1) -ым разрядом частного, второй и третий выходы дешифратора 2 являются выходами, на которых форми; руются остатки "10" и "01" соответственно, полученные при делении информации, поступающей с выходов двух старших разрядов регистра 1.

1062690

Номера блоков формирования разрядов частного

Г б 5 4

3 2 1

Номера выходов

Дешифратор

1 (частное) 2 (остаток

2/3) 3 (остаток

1/3) (при больших значениях И) В блоке З„формирования (п.-2) -го разряда частного анализируется информация, поступающая с (й -2) -го разряда регистра 1 и остатки от деления двух старших разрядов .регист. ра 1, поступающие с второго и третьего выходов дешифратора 2. На первом выходе этого блока формируется единица при наличии единицы на следующих его входах: на перном и втором, или на первом и третьем, или только на втором. На втором выходе этого блока формируется единица при наличии единицы на. следующих его входах: первом и втором или на треть ем. На третьем выходе этого блока 15 формируется единица при наличии единицы на первом входе или на втором.

Первый выход этого блока является (n -2).-ым разрядом частного, второй и третий выходы являются выходами остатков "10" и "01" соответственно, полученные при делении трехразрядБыстродействие данного устройства по сравнению с известным увеличено, так как суммарное время задержки составляет

Т = 1 + .(-.n — 2 j 3 Ф

45 где 1 ц — время эадержкК дешифратора; Я вЂ” время задержки одного логи-. в то время как в известном устройного двоичного числа, поступающего на его Входы.

В блоке, 3 формирования(И-3)разряда частйого анализируется ин формация, поступающая с (n -3) -го разряда регистра 1 и остатки от деления трех старших разрядов регистра 1, Работа этого блока формирования â-3) -го разряда частного и всех последующих блоков формирования разрядов частного аналогична рассмотренному выше.

В таблице приведен пример деления числа 167,(в двоичной системе счисления 10100111): на число 3 (в двоичной системе счисления 11) .

Частное от деления числа 167 на число 3 равно 552/3, что соответствует целей части двоичного числа, записанного в первой строке таблицы, и дробной части "10" на выходах блока 3. стве суммарное время задержки составляло

Т = (h- 1) ° 4 с.

Таким образом, увеличение быстродействия можно оценить как

К =—

T 3

16 17

ВНИИПИ Закаэ 10218/49 Тираж 706 Подписное й»

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4