Устройство для вычисления функции @ = @

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ у г содержащее генератор тактовых импульсов и п блоков вычисления итерации, каждый из которых содержит первый и второй регистры, первый и второй cy Dv aтopы и коммутатор , причем в каждом блоке вычисления итерации разрядные выходы первого регистра соединены с первой группой входов первого сумматора, разрядные выходы второго регистра подключены к первой группе входов второго сумматора и к информационным входам первой группы коммутатора, разрядные выходы первого сумматора-кс1ждого блока вычисления итерации соединены с соответствующими разрядными входами первого регистра и последующего блока вычисления итерации, выход генератора тактовых импульсов подключен к управляющим входам всех регистров устройства, отличающееся тем, что, с целью сокращения оборудования, в каждый блок вычисления итерации введены триггер и группа элементов И, первые входы которых соединены с соответствующими разрядными выходами первого регистра, выход триггера подключен к вторым входам элементов И группы, выходы которых соединены с второй группой входов первого сумматора, вторая группа входов второго сумматора подключена к входам константы п ( ) устройства, где . 1, ..., и , разрядные выходы второго сумматора соединены с информационными входами второй группы коммутатора, первый и второй управляющие входы которого подключены соответственно к инверс (Л ному и прямому выходам знакового разряда второго сумматора, выход генератора тактовых импульсов соединен с управляющими входами всех триггеров устройства, прямой выход знакового разряда второго сумматора каждого блока вычисления итерации подключен к информационному входу триггера последующего блока вычисления итерации, выходы коммутатора каждого блока вычисления итерации подключены к разрядным входам второго регистра последующего блока вычисления итерации.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) 3(51) G 06 F 7/556 с

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ASTOPCHQMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ! (21) 3506893/18-24 (22) 28, 10, 82 (46) 23,12,83, Бюл. Р 47 (72) A.A.Ìåëüíèê (53) 681.325(088.8) (56) 1. Авторское свидетельство СССР

Р 631924, кл. G 06 F 7/544, 1978.

2. Авторское свидетельство СССР

Р 962927, кл. G 06 F 7/556, 1981. (54)(57) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ

ФУНКЦИИ у = Е", содержащее генератор тактовых импульсов и tl блоков вычисления итерации, каждый из которых содержит первый и второй регистры, первый и второй сумматоры и коммутатор, причем в каждом блоке вычисления итерации разрядные выходы первого регистра соединены с первой группой входов первого сумматора, разрядные выходы второго регистра подключены к первой группе входов второго сумматора и к информационным входам первой группы коммутатора, разрядные выходы первого сумматора. каждого блока вычисления итерации соединены с соответствующими разрядными входами первого регистра и последующего блока вычисления итерации, выход гене" ратора тактовых импульсов подключен к управляющим входам всех регистров устройства, отличающееся тем, что, с целью сокращения o6opy- i дования, в каждый блок вычисления итерации введены триггер и группа элементов И, первые в ходы которых соединены с соответствующими раэр ядными выходами первого регистра, выход триггера подключен к вторым входам элементов И группы, выходы которых соединены с второй группой входов первого сумматора, вторая группа входов второго сумматора подключена к входам константы )и .(1+2 - + ) устройства, где (= 1, ..., и, разрядные выходы второго сумматора соединены с информационными входами второй группы коммутатора, первый и второй управляющие входы которого Ж подключены соответственно к инверсному и прямому выходам знакового разряда второго сумматора, выход re нератора тактовых импульсов соединен с управляющими входами всех триггеров устройства, прямой выход знаково-Я го разряда второго сумматора каждого блока вычисления итерации подключен к информационному входу триггера последующего блока вычисления итерации, выходы коммутатора каждого блока вычисления итерации подключены к разрядным входам второго регистра последующего блока вычисления итерации.

1062б93

Изобретение относится к вычислительной технике и предназначено для использования в специализированных цифровых вычислительных машинах высокой производительности.

Известно устройство для вычисления функции вида 11 =Е", содержащее регистр аргумента, блок маскирования. аргумента, блок r.îñòîÿííîé памяти, блок оперативной памяти, блок выделения младшей зоны аргумента, блок 10 управления, блок определения нулевых значений аргумента, блок умножениями.

Недостатками устройства являются низкое быстродействие, поскольку экспоненциальная функция здесь вы- 15 числяется по интегральной формуле, причем в каждой итерации используется времяемкая операция умножения, и большие затраты оборудования.

Наиболее близким по технической р0 сущности к изобретению является конвейерное устройство для вычисления функциЯ 11 = Е" . содержащее (2ц-1) блоков вычисления итерации, регистр, триггер, выходной регистр, сумматор, коммутатор, блок управления, каждый блок вычисления итерации которого содержит два регистра, дна коммутатора, два сумматора.

Данное устройство производит вычисления функции 11 " 6" на основе алгоритма Волдера со знакопеременными приращениями, н соответствии с которым для вычисления функции = 6" необходимо выполнять 2И итераций, где

11 — разрядность обрабатываемых чисел.

Устройстно построено по конвейерному принципу и каждая ступень конвейе. ра реализует одну итерацию алгоритма

Волдера, что позволило достичь очень высокого быстродействия, определяе- 40 мого задержкой в многоразрядном сумматоре (2) .

Однако наличие в устройстве 2Ь ступеней требует для его построения больших затрат оборудонания, опреде" 45 ляемых выражением

2п

%,=(Л11-(2n(< + 11- К()Н -—

1 Р(Кс9 1(LM 4 Кк „

50 микросхем, где коэффициенты К,, Кс,„, К„ц учитывают количество обрабатываемых разрядов в одном корпусе микросхемы, на которой строится соответственно регистр, сумматор, коммутатор, и — разрядность обрабатываемых чисел, — номер. итерации, К (< ) число, равное i/1 +1 при четном и равное (< + 1)/":2 при нечетном, Целью изобретения является сокра- ь0

/ щение оборудования.

11оставленная цель достигается тем, ч1о н устройство для вычисления функции 11 = 8 содержащее генератор тактовых импульсов и tl блокон вычис- 65 ления итерации, каждый из которых содержит первый и второй регистры, первый и второй сумматоры и коммутатор, причем в каждом блоке вычисления итерации разрядные выходы первого регистра соединены с первой группой входов первого сумматора, разрядные выходы второго регистра подключены к первой группе входов второго сумматора и к информационным входам перной группы коммутатора, разрядные выходы первого сумматора каждого блока вычисяения итерации соединены с соответствующими разряд ными входами первого регистра последующего блока вычисления итерации, ныход генератора тактовых импульсов подключен к управляющим входам всех регистров устройства, введены в каждый блок вычисления итерации триггер и группа элементов И, первые входы которых соединены с соответствующими разрядными выходами первого регистра, выход триггера подключен к вторым входам элементов И группы, выходы которых соединены с второй группой входов первого сумматора, вторая группа входов второго сумматора подключена к нходам константы

3н (1+2 + ) устройства, где i = 1,, tl, разрядные выходы второго сум. матора соединены с информационными входами второй группы коммутатора, первый и второй управляющие нходы которого подключены соответственно к инверсному и прямому ныходам знакового разряда второго сумматора, выход генератора тактовых импульсов соединен с управляющими входами всех триггеров устройства, прямой выход знакового разряда второго сумматора каждого блока вычисления итерации подключен к информационному входу триггера последующего блока вычисления итерации, выходы коммутатОра каждого блока вычисления итерации подключены к разрядным; входам второго регистра последующего блока вычисления итерации.

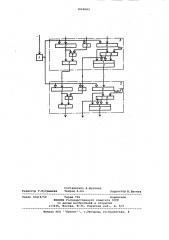

На чертеже представлена блок-схема устройства для вычисления функции

g =е .

Устройство содержит генератор 1 тактовых импульсов и блоков 2 вычисления итерации, каждый иэ которых содержит первый и второй регистры 3 и 4, триггер 5, группа элементов

И 6, первый и второй сумматоры 7 и 8, коммутатор 9, Коммутаторы 9 каждого блока 2 вычисления итерации содержат две группы по И днухвходовых элементов И,. объединенных элементом ИЛИ. Группа элементов И каждого блока 2 вычисления итерации содержит (и — ) двухвходовых элементов И,где — номеР блока.

1062693

5 Г;„= ;-« «q "1;

<р; =(р -g; п(4 2- ) 0, если, > О, Sign g i= S

Здесь 1 — номер итерации (< = О

1у 2, ° ° ° р h -1) °

При начальных условиях ХО=1, о =Ог

=.Х данные формулы дают X> „8"". 15

Устройство работает следующим образом.

По сигналу пуска, поступающему на вход генератора 1 тактовых импульсов, генератор .начинает вырабатывать тактовые импульсы, которые поступают на регистры и триггеры устройства.

В первом такте во второй регистр

4 первого блока 2 вычисления итерации поступает значение операнда Х 75 в обратном или дополнительном коде в форме с фиксированной запятой.

B триггер 5 поступает О, а в первый регистр 3 поступает 1 .

На первом сумматоре 7 формируется значение Хl ХО, поскольку группа эле. ментов И б закрыта. На втором сумматоре 8 производится сложение содержимого второго регистра 4 и константы п 2, сформированной на его входе 35 монтажным способом путем подачи в соответствующий разряд сумматора значения О или 1 в зависимости от того, какое значение имеет в данном разряде константа, представлен ная в обратном или дополнительном 4О коде. Таким образом, на сумматоре образуется значение Ц и, в зависимости от его знака, на выход коммутатора 9 приходит или содержимое второго регистра 4, если знак поло- 45 жительный, или содержимое сумматора 8, если знак отрицательный, т.е. на выходе коммутатора 9 образуется значение Ц»

Во втором такте результаты, полу- 50 ченные в первом блоке 2 вычисления итерации записываются во второй блок 2 вычисления итерации: значение иэ первого сумматора 7 записывается в первый регистр 3, знак второго сум 55 матора 8 - в триггер 5, а значение из коммутатора 9 — во второй регистр

4. Одновременно во второй регистр 4, первого блока 2 вычисления итерации поступает второй операнд. 60

B первом блоке 2 вычисления итерации производится выполнение первой итерации над вторым операндом, аналогично выполненной в первом такте

10 т (смФtкм 7 где коэффициент К< учитыв ает количество разрядов в одном корпусе микросхемы. Как видно, затраты оборудования на данное устройство меньше по сравнению с известным, более чем в два раза.

Высокая однородность структуры устройства позволяет его реализовать в виде больших интегральных схем.

Вычисление функции у = e" в устройстве производится на основе метода цифра эа цифрой со знакопостоянными приращениями, который описывается итерационными формулами над первым операндом. Во втором бло-, ке 2 вычисления итерации выполняется вторая итерация над первым -операндом и на выходе первого сумматора 7 появляется значение Хд, а на выходе коммутатора 9 — значение.cg . Сдвиг значения Х на один разряд вправо осуществляется путем соединения выхода ) -го разряда группы элементов И б с входом () Ф 1) -ro разряда первого сумматора 7 (1 = 1, 2, ..., и ) . На выходе второго сумматора 8 монтажным способом формируется константа

Еп (1 2 " ) .

B дальнейшем в каждом такте результаты предыдущих блоков поступают в последующие блоки, а во второй регистр 4 первого блока вычисления итерации поступает новый операнд, и т,д,, причем в каждом последующем блоке промежуточные результаты из группы элементов И б поступают на второй вход первого сумматора 7 со сдвигом на один разряд вправо, большим,чем в предыдущем блоке, а в.выра. жениях логарифмов, формируемых монтажным способом на втором входе второго сумматора 8, степень двойки ,возрастает на единицу.

В и — м такте на выходе первого сумматора 7 последнего блока 2 вычисления итерации получается первый результат, а в дальнейшем в каждом такте на выходе устройства будет появляться новый результат.

Предлагаемое устройство работает по конвейерному принципу. Его быстродействие определяется длительностью одного такта, которая равна задержке в одной ступени устройства и определяется выражением где м — время суммирования на сумматоре; задержка информации коммутатором.

Затраты оборудования на данное устройство определяются выражением н

W=2n i, s — iФ вЂ” — < Е („-„ («

"рг "см "км кр

1062693

Тираж 706 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретенйй и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 102,19/50

Филиал ППП Патент, г.ужгород, ул.Проектная, 4

Составитель А,Шулянов

Редактор Т,Кугрыыева Техред A.A÷ Корректор В.Бутяга