Анализатор спектра

Иллюстрации

Показать всеРеферат

АНАЛИЗАТОР СПЕКТРА, содержащий арифметический блок, первый и второй блоки памяти,, блок постояннрй памяти, первую группу элементов И, первый и второй сумматоры, синхронизатор, первый ,и второй компараторы , первый и второй счетчики, дешифратор,- причем первый выход .синхронизатора подключен к первым входам элементов И первой группы, выходы которых соединены с адресными входами первого и второго блоков памяти, информационные выходы которых подключены соответственно к входам первого и второго операндов арифметического блока, выходу первого и второго операндов которого соединены с информационнь га входами соответственно первого и второго блоков памяти, причем информационные входы первого и второго блоков памяти являются соответственно первым и вторым информационными входами анализатора, выход первого компаратора соединен с тактовым входом первого счетчика, информационный выход которого соединен с первьм входом второго компаратора, выход которого подключен к входу Сброс первого счетчика и тактовому входу второго счетчика, информационный выход кото ,рого соединен с входом дешифратора , а информационный выход блока постоянной Псшяти подключен к входу задания коэффициента арифмети , ческогр блока,.отличаювди йс я тем, что, с целью упрощения анализатора, он содержит вторую группу эл@4ентов И и третий счетчик , инфо нлационный выход которого подключен к первому входу первого компаратора, первому входу первого сумматора, первс у входу второго сумматора и вторв входам элементов И первой группы, третьи входе кото (Л рых подключены к выходу второго сукматора, второй вход которого объединен о вторым входом второго компаратора и подключен к. первому выходу дешифратора, второй выход которого соединен с,вторые входом первого сумматора, выход которого соединен с информащюнным входом третьего счетчика, установочный СП) вход которого соединен с выходами tsD эл «ентов И второй группы, первые входы которых соединены с выходом sj первого компаратора, второй вход которого является входом задания сь величины . N(N - размер преобразования ) , выход первого счетчика соединен с адресным входом блока постоянной памяти и вторыми входами элементов И второй группы, вто- . рой выход синхронизатора соединен с тактовым входом третьего счетчика , вход Сброс которого подключен к выходу второго компаратора,

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

3(511 6 06 F 157332

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3493223/18-24 (22) 24,09. 82 (46) 23.12,.83 Бщл 9 47 (72) Б.A,Nàêñèìîâ, В.В.Сумароков, В.Ф..Черепов и С. Ф., Свиньин (53) 681. 32 (088. 8) (56) 1, Авторское свидетельство СССР

9 470808, кл. Я 06 F 15/332, 1977

2. Патент CL»A В 3920978, кл.1 06 F 15/332, 1976.

3 Авторское свидетельство СССР

В 815664, кл Gi 06 15/332, 1981 (прототип ) (54)(57) АНАЛИЗАТОР СПЕКТРА, содержащий арифметический блок, первый и второй блоки памяти„ блок постоянной памяти, первую группу элементов И, первый и второй сумматоры, синхронизатор, первый,и второй компараторы, первый и второй счетчики, .дешифратор; причем первый выход синхронизатора подключен к первьва входам элементов И первой группы, выходы которых соединены с адресными входами первого и второго блоков памяти, информационные выходы которых подключены соответственно к входам первого и второго операндов арифметического блока, выходы первого и второго операндов которого соединены с информационньвги входами соответственно первого и второго блоков памяти, причем информационные входы первого и второго блоков памяти являются соответственно первым и вторьм информационными входами анализатора, выход первого компаратора соединен с тактовым входом первого счетчика, информационный выход которого соединен с первык входом второго

„.SU„„1QQ2716 А компаратора, выход которого подключен к входу "Сброс" первого счетчика н тактовому входу второго счетчика, информационный выход кото„рого соединен с входом дещифратора, а информационный выход блока постоянной памяти подключен к входу задания коэффициента арифмети.ческого блока,.о т л и ч а ю щ и йс я тем, что, с целью упрощения анализатора, он содержит вторую группу элементов И и третий счетчик, информационный выход которого подключен к первому входу первого компаратора, первому входу первого сумматора, первому входу второго сумматора и вторык входам элементов

Ф

H первой группы, третьи входы которых подключены к выходу второго сумматора, второй вход которого объединен о вторым входом второго С компаратора и подключен к.первому выходу дешифратора, второй выход Я которого соединен с вторьве входом первого суюеатора, выход которого соер лнен с информационным входом третьего счетчика, установочный вход которого соединен с выходами элементов И второй группы, первые входы которьк соединены с выходом . первого компаратора, второй вход которого является входом задания величины . Я (N - размер преобразования), выход первого счетчика соединен с адресным входом блока постоянной памяти и вторыми входами элементов И второй группы, вто- рой выход синхронизатора соединен с тактовым входом третьего счетчика, вход Сброс которого подключен к выходу второго компаратора.

1062716

Изобретение относится к вычислительной технике, а именно к анализаторам спектра, работающим íà основе обработки временного. сигнала с помощью алгоритма, быстрЬго преобразования Фурье (БПФ)

Йзвестно устройство для вычисления коэффициентов Фурье, содержащее итеративный сдвиговый регистр, основной и дополнительный счетчик адресов оперативного запоминающего устройства (ОЗУ), блок логического .управления и адресный переключатель

Г1 .

Недостатком этого устройства является то, что генерирование адресов ОЗУ занимает в этом устройстве, как минимум, два такта, не считая времени, необходимого для занесения начального адреса на ЭВИ

Известен .также анализатор спектра, содержащий первый и второй входные регистры, первый, .второй, третий и четвертый перемножители, блок вентилей, первое и второе ОЗУ, постоянное запоминающее устройство, синхронизатор, счетчик числа итераций и счетчик адреса f2 ).

Недостатком этого анализатора является необходимость сдвига кодов, адресов и ПЗУ на разное число разрядов в зависимости от номера итерации, что приводит к низкому быстродействию анализатора.

Наиболее близким но технической сущности к данному устройству является анализатор спектра, содержащий первый и второй входные регистры, первый, второй, третий и четвертый перемножители, блок элементов И, первое и второе ОЗУ, НЗУ, синхрони затор, первый, второй и третий счетчик, первый и второй компаратор, первый и второй дешифратор, первый и второй мультиплексор, блок вычитания, первый и второй сумматор и группу элементов И (3 3.

Недостатками анализатора являются сложность схемы устройства и большое количество оборудования.

Целью изобретения является упрощение устройства.

Поставленная цель достигается тем, что анализатор спектра, содержащий арифметический блок, первый и второй блоки памяти, блок постоянной памяти, первую группу элементов

И, первый и второй сумматоры, синхронизатор, первый и второй компараторы, первый и второй счетчики, дешифратор, причем первый выход синхронизатора подключен к первик входам элементов И первой группы, выходы которых соединены а адресными входами первого и второго блоков памяти, информационные выходы кото1 рых подключены соответственно к входам первого и второго операндов арифметического блока, выходы первого и второго операндов которого соединены с информационными входами соответственно первого и второго . блоков памяти, причем информационные входы первого и второго блоков памяти являются соответственно-первым и вторым информационными входащ ми анализатора, выход первого ком паратора соединен с тактовым входом первого счетчика, информационный выход которого соединен с пер.вым входом второго компаратора, 5,.выход которого подключен к входу "Сброс первого счетчика и тактовому входу второго счетчика, информационный выход которого соединен с входом дешифратора, а.информационный выход блока постояйной па ® мяти подключен к входу задания коэффициента арифметического блока, содержит вторую группу элементов И и третий счетчик, информационный выход которого подключен к первому входу первого сумматора, первому входу первого компаратора, первому входу второго сумматора. и вторым входам элементов И второй группы, задаваемого двоично30 инверсным адресом.с выхода счет- чика 14 (т.е адресом ., в котором старщим двоичным разрядом является высод младшего разряда счетчика, а младшим двоична разрядом—

35 выход старшего разряда счетчика)

По окончании операции Бабочка результаты записываются в блоки 8 и 9, импульс с синхронизатора приводит к изменению. адресов операндов операции Бабочка, снова производится операция Бабочка" и результаты записываются в блоки 8 и 9 до тех пор, пока не будет обработаны все отсчетов, В той части ана45 лизатора, которая обеспечивает адресацию операндов в процессе БПФ происходят следующие процессы. Начиная с начального состояния (код на выходе счетчика 13 равен О, код в счетчике 14 (счетчик е) — 0, код в счетчике 12 (счетчик i ) -О, по каждому импульсу синхронизатора число, находящееся в накапливающем регистре 13, увеличивается на величину 2 +" (:т.:.е. на нулевой итерации увеличивается на два, на первой на четыре и .т, д,.), адрес второго операнда формируется на выходе сумматора 20 суммированием кода с выхода счетчика 13 и величины 2 .

i.+ i

6() Как величина 2, так и величина

2" образуются на выходе дешифратора 17, но для образования числа

2 выходной код дешифратора 17 прямо подается на вход сумматора 20, а на вход сумматора 19 этот же код

1062716 поступает со сдвигом на один разряд в сторону старших разрядов,.

,т.:,е. вход нулевого разряда суммато-. ра 19 навсегда устанавливается в ноль, вход первого разряда сумматора 19 соединяется с выходом первого разряда дешифратора 17 и т д;

В некоторый момент времени импульс с синхронизатора 11 вызывает изменение числа в счетчике 13 настолько, 0 что оно превысит 2 :,, В этот момент срабатывает компаратор 15 и происходит следукщеег появившийся перепад напряжения на выходе компаратора 15 увеличивает на единицу код счетчика 14 (счетчик е) и, в то же самое время разрешает передачу на установочные входы счетчика. 13 через третьи входы которых подключены к выходу второго сумматора, второй вход которого объединен с вторьм входом второго компаратора.,и подключен к первому выходу дешифратора, второй выхдд которого соединен с вторым входом первого сумматора, выход кото рого соединен с информационным входом третьего счетчика, установочный вход которого соединен с выходами элементов И второй группы, первые входы которых соединены с выходом первого компаратора, ° второй З0 вход которого является входом задания величины М (М вЂ” размер преобразования), выход первого счетчика соединен с адресным входом блока постоянной памяти и вторыми 35 входами .элементов И второй группы, второй выход синхронизатора соединен с тактовым входом третьего счетчика, вход Сброс" которого подключен к выходу второго компара- 40 тора

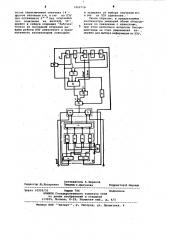

На чертеже приведена функциональная схема устройстаа.

Анализатор состоит иэ двух входных регистров 1 и 2., четырех пе- 45 ремножителей 3 †. 6 и группы элементов И арифметического блока 7, двух блоков 8 и 9 памяти(ОЗУ), блока 10 постоянной памяти (ПЗУ), синхронизатора 11, первого счетчика 12, третьего счетчика 13, второго 5. счетчика 14, двух компараторов 15 и 16, дешифратора 17, первой группы

18 элементов И, двух сумматоров

19 и 20, второй группы 21 элементов И, элементы 1-7 образуют арифметический блок 22.

Анализатор работает .следукщимобразом .

На входе компаратора 15 фиксиру-. ется код, соответствующий величине 60

2 -N равной числу временных отсчетов в обрабатываемой анализатором выборке. Выборка из N комплексных отсчетов загружается в блоки 8 и 9

По окончании загрузки третий счетчик 13 и счетчики 12 и 14 обнуляются. Далее производится операция

" Бабочка" над отсчетами с номерами, которые указнвают выходной код счетчика 13 и сумматора 20, с использованием вектора поворота, элементы И 18 информации с выхода счетчика 14, в счетчике 13 устанавливается код, соответствующий новому значению счетчика 14, и условия для срабатывания компаратора 15 пропадают, выключение компаратора 15 эаI прещает прохождение информации со счетчика 14 на установочные входы счетчика 13 Лосле этого процесс увеличения кода в счетчике 13 по импульсам синхронизатора 11 начинается уже с нового значения, соответствующего новому состоянию счетчика 14, В некоторый момент перепад напряжения.с выхода компаратора 15 вызывает такое увеличение кода в счетчике 14, что он становится равным величине r тогда на выходе компаратора 16 появляется ° перепад напряжения, который вызывает увеличение на единицу кода в счетчике 12 (счетчик 1) и сброс в ноль счетчика 14 и счетчика 13, Последукщие импульсы синхронизатора вызывают описанные процессы до тех пор, пока на г+1 выходе дешифратора 17 не .появится перепад напряжения, который. служит сигналом для окончания обработки временной реализации из 2" отсчетсВ,, По окончании описанного процесса.в блоках 8 и 9 находятся отсчеты комплексного мгновенного спектра. входного сигнала, Предлагаемый анализатор и известный генерируют в процессе обработки входного сигнала одинаковые для каждой итерации пары адресов операндов, но в предлагаемом анализаторе адреса пар изменяются не монотонно, как в схеме известного, что и дало возможность исключитв из схемы два мультиплексора, дешифратор и блок вычитания. Кроме того, предлагаемый анализатор дает и эффект .. увеличения быстродействия, что связано со способом формирования адреса ПЭ, Так на нулевой итера-, ции известный и предлагаемый анализаторы работают одинаково, но уже на первой итерации s известном для каждой новой пары операндов выбирается новое значение sin u соз из

ПЗУ Но ПЗУ обладает конечным быстродействием и каждая операция

Бабочка таким образом удлиняется во времени, В предлагаемом анализаторе на первой итерации для первых

2" аллар операндов выбрано одно значение s n и cos из ПЗУ, а затем

1062716

Составитель A Баранов

Редактор Я.Лазаренко Техред С.Мигунова

КорректорМ Шар<хаи

Заказ 10220/51 Тираж 706 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская ндб., д 4/5 б

Филиал ППП Патент, <г ужгород, Ул. Проектная, 4 после переключения, счетчика 14 другое значение з1п и cos из ПЗУ для оставшихся 2 " + пар операндов это поэв оляет не вносит за- держку в кайсдую операцию "Бабочка .

Только на последней итерации режимы работы ПЗУ известного и предлагаемого анализаторов совпадают и задержка от выбора значений si и Cos из ПЗУ одинакова.

Таким образом, в предлагаемом анализаторе уменьшей объем оборудо5 вания по сравнению с известным

У при этом несколько возросло быстродействие эа счет уменыпения за/ держек для выбора информации из ПЗУ, г