Ассоциативное запоминающее устройство

Иллюстрации

Показать всеРеферат

1. АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее регистр опроса, информационные регистры, цифро-аналоговые преобразователи и последовательно соединенные индикаторы и блоки сравнения, одни из входов которых подключены к выходу селектора, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены арифметические блоки, входы которых подключены к выходам регистра опроса и информационных регистров, а выходы соединены с входами цифроаналоговых преобразователей, выходы которых соединены с другими входами блоков сравнения и входами селектора 2. Устройство по п. 1, о т л ич .ающееся тем, что каждый арифметическийблок ;содержит элементы Ни ИЛИ и сумматоры, выходы которых подключены к входам элементов И, выходы которых соединены с входами элементов ИЛИ, выходы котосл рых являются выходами устройства, входами которого являются входы сумматоров. Фиг1

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (11) 1(5И G 11 С 15/00 .

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3504160/18-24 (22) 25.10.82 (46) 23.12. 83. Бюл. Р 47 (72) В.Б. Матвеев. (71) Казанский ордена Трудового

Красного Знамени и ордена Дружбы народов авиационный институт им. A.Н. Туполева (53) 681.327.6(088.8) (56) 1. Авторское свидетельство СССР

)) 277857, кл. G 11 С 15/00, 1969.

2. Авторское свидетельство СССР по заявке )) 3418356/18-24, кл. G 11 С 15/00, 06.04.82 (прототип). (54)(57) 1. АССОЦИАТИВНОЕ ЗАПОМИНА10ЩЕЕ УСТРОЙСТВО, содержащее регистр опроса, информационные регистры, цифро-аналоговые преобразователи и, последовательно соединенные индикаторы и блоки сравнения, одни из входов которых подключены к выходу селектора, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены арифметические блоки, входы которых подключены к выходам регистра опроса и информационных регистров, а выходы соединены с входами цифроаналоговых преобразователей, выходы которых соединены с другими входами блоков сравнения и входами селектора.

2. Устройство по п. 1, о т л ич .а ю щ е е с я тем, что каждый арифметический блок содержит элементы И -и ИЛИ и сумматоры, выходы которых подключены к входам элементов И, выходы которых соединены с ж входами элементов ИЛИ, выходы которых являются выходами- устройства, входами которого являются входы сумматоров.

1062790. Изобретение относится к вычислительной технике в частности к области запоминающих устройств.

Известны ассоциативные запоминающие устройства содержащие регистры хранимых признаков, детекторы по числу хранимых признаков и регистр опроса fl) .

В этом устройстве поиск по близости к признаку опроса может быть осуществлен только алгоритмически, т.е. с пониженным быстродействием.

Наиболее близким техническим решением к изобретению является ассоциативное запоминающее устройство, содержащее регистр опроса, последовательно соединенные информационные регистры, цифровые блоки сравнения, цифро-аналоговые преобразователи, селекторы, аналоговые блоки сравнения и индикаторы (2j .

Недостатком известного устройства является пониженное быстродействие.

Целью изобретения является повышение быстродействия устройства. 25

Поставленная цель достигается, тем, что в ассоциативное запоминающее устройство, содержащее регистр опроса, информационные регистры, цифроаналоговые преобразователи и после- 30 довательно соединенные индикаторы и блоки сравнения, одни из входов которых подключены к выходу селек-. тора, введены арифметические блоки, входы которых подключены к выходам 35 регистра опроса и информационных регистров, а выходы соединены со входами цифро-аналоговых преобразователей, выходы которых соединены с другими входами блоков сравнения и входами селектора.

Каждый арифметический блок содержит элементы И и ИЛИ и сумматоры, выходы которых подключены ко входам элементов И, выходы которых соединены со входами элементов ИЛИ, выходы которых являются выходами устройства, входами которого являются входы сумматоров.

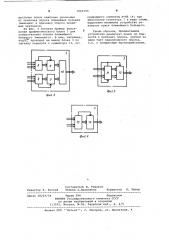

На фиг. 1 показана структурная схема устройства; на фиг. 2-4 — примеры выполнения арифметического блока.

Устройство содержит (фиг. 1) информационные регистры 1, регистр 2 опроса, арифметические блоки 3, цифро-аналоговые преобразователи 4, блоки 5 сравнения, индикаторы 6 и селектор 7, служащий для выделения экстремального значения сигнала.

Арифметический блок (фиг. 2) со- 60 держит сумматоры 8, элементы И 9 и элементы ИЛИ 10.

Вариант арифметического блока (фиг. 3) содержит сумматор 11 и коммутатор 12. 65

Еще один вариант арифметического блока (фиг. 4) содержит сумматор 13 и элементы И вЂ” НЕ 14.

Устройство работает следующим образом.

На входы одного из сумматоров 8 каждого арифметического блока 3 с выходов регистров 1 и 2 поступают прямой код соответствующего хранимого признака Х " («= 1<п ) и инверсный

< код признака опроса У ". На входы другого сумматора 8 — инверсный код соответствующего хранимого признака X,„ и прямой код признака опро<«р са ур.

На выходах сумматоров 8 образуются коды суммы 5 < и 5<2 следующим образом

5 -x у

« )

UH П -«< = Х < (ф 1

При этом на одном из сумматоров

8 образуется сигнал переноса (переполнения), который открывает соответствующие элементы И 9 и на выход арифметического блока проходит код 5< такой, что

5,, если Х; >У

5„=-/Х; -У/= «< если Х, Y

« где Х; и У вЂ” значения соответствующего хранимого признака и признака опроса.

На выходах цифро-аналоговых преобразователей 4 образуются аналоговые величины U<

0,=e5„ « где  — масштабный коэффициент.

В селекторе 7 выделяется, например, минимальная величина(« (J mjn U,, которая сравнивается в блоках 5 сравнения с величинами U, и, в случае, например, совпадения этот факт фиксируется в соответствующем индикаторе 6. Тем самым отмечаются хранимые признаки, ближайшие к признаку опроса.

В качестве арифметического блока может быть использована схема с одним сумматором 11 (фиг. 3), на входы которого поступает, например, Х и У"" и на прямом выходе сумматора 1) устанавливается код

5"",(«X<,p YUH

U«< а на инверсном выходе — 5 „.

Если Х, У, то появляется сигнал переноса, который прибавляет единицу к полученной сумме и пропускает на выход коммутатора 12 код5,; в пр. противном случае на выход коммутатора 2 проходит код 5, В устройстве, при соответствующем выполнении арифметического блока 3 и, селектора 7, может быть осу1062790

Фиг 5 фиг 2 фиг 4

Составитель В. Рудаков

Редактор П. Коссей Техред Л,Пилипенко Коррек тор О. Тигор

Тираж 594 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 10229/54

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 ществлен поиск наиболее удаленных от признака опроса ближайших больших (меньших) к признаку опроса хранимых признаков.

На фиг. 4 показан пример выполнения арифметического блока 3 для осуществления поиска ближайшего большего (меньшего). В нем, например, кодб" проходит на выход блока 3 по сигналу переноса с сумматора 13, открывающего элементы И-НЕ 14; при выполнении селектора 7 в виде схемы, выделения минимума устройство реализует поиск ближайшего большего.

Таким образом, предлагаемое устройство реализует поиск по близости к признаку опроса, причем за один такт параллельного опроса, т.е. с повышенным быстродействием.