Устройство для сложения по модулю

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ПО МОДУЛЮ, содержащее первый и вто: ой сумматоры и одноразрядный сумматор первый и второй входы которого соединены с входами младших разрядов модуля и первого операнда устройства соответственно, первые входы разрядов первого сумматора соединены с входами старших разрядов первого операнда устройства, выход переноса однозарядного сумматора соединен с вЬсодом переноса второго сумматора.. отличающееся тем, что, с целью сокращения объема оборудования , выходда разрядов первого сумматора соединены с первыми вхрД1ами разрядов второго сумматора, вторые входа j -X разрядов второго сумматора ( j i , если ,(-м,м«Хо1;. М- «So- при М четном,- 1 ПРИ М нечетном ) соединены с выходом прямого значения переноса первого сумматора, вторые входы остальных разрядов второго сумматора соединены с выходом инверсного значения переноса первого сумматора, третий вход одноразрядного сумматора соединён с входом младшего разряда второго операнда .устройства, вторые входы разрядов первого сумматора соединены с вход1ами старших разрядов второгооперанда устройстваг выходы разрядов второго cyMMaTOipa и выход суммы одноО У: разрядного сумматора,являются выхо дами устройства. .f SD эо

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (П) З(51) С 06 Р 7 49,I

0ПИСАНИЕ ИЗОБРЕТЕНИЯ, -:

К АВТОРСКОМУ, СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

tlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3408561/18-24 (22) 12е03.82 (46) 30.12,83. Бюл. 9 48 (72) В.В.Балюк, Р,Быжиковски (ПНР) и Ю.С.Каневский (71) Киевский ордена Ленина политехнический институт им. 50-летия Великой Октябрьской социалистической революции (53) 681.325(088.8) .(56) 1. Авторское свидетельство СССР

В 332460, кл. G 06 F 7/72, 1970.

2. Авторское свидетельство СССР

В 570052, кл. G 06 F 7/72, 1977

{прототип). (54) (57) УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ

ПО МОДУЛЮ, содержащее первый и втоyoN сумматоры и одноразрядный сумматор первый и второй входы которого соединены с входами младших разрядов модуля и первого операнда устройства соответственно, первые входы разрядов :первого сумматора соединены с входами старших разрядов первого операнда устройства, выход переноса однозарядного сумматора соединен с входом переноса второго сумматора,.

I о т л и ч а ю щ е е с я тем, что, с целью сокращения объема оборудования, выходы разрядов первого сумматора соединены с первыми входами разрядов второго сумматора, вторые входы ) -х разрядов второго сумматора (1=, если я д =-() ((; (-«.«,М Х. а; -2, а (tl

М-«2 а;-2 . при М четной, . 1*« при М нечетном) соединены с выходом прямого значения переноса первого сумматора, вторые входы остальных разрядов второго сумматора соединены с выходом Я инверсного значения переноса первого сумматора, третий вход одноразрядного сумматора соединен с входом младшего разряда второго операнда устройства, вторые входы разрядов первого сумматора соединены с входами старших разрядов второго операнда устройства, выходы разрядов вто» рого сумматора и выход суммы одноразрядного сумматора являются выхо" дами устройства.

1064278

Изобретение относится к вычислит ельной технике и может быть использовано в вычислительных машинах и системах, работающих в позиционных и непозиционных системах счисления, системах контроля передачи дискретной информации, системах ! контроля вычислительных машин при построении сумматоров по произвольному модулю.

Известен сумматор по модулю, содержащий блок, позиционный и непозиционный сумматоры, группы элементов И и ИЛИ и соответствующие свя. зи fl).

Недостатками указанного устройства являются значительный объем оборудования, низкое быстродействие и невозможность его непосредственного использования для реализации операций сложения и вычитания над числами со знаком.

Наиболее близким к предлагаемому является сумматор по модулю, содержащий позиционный и непозиционный сумматоры, блок инвертирования кода, блок переполнения позиционного сумматора, группы элементов И и ИЛИ, причем входы блока инвертирования кода соединены с шинами первого числа, управляющий вход блока инвертирования кода — с шиной управления,. выходы — с первой группой входов позиционного сумматора, вторая группа входов которого соединена с шинами второго числа, третья — с шинами кода дополнения модуля, выходы позиционного сумматора соединены с входами блока переполнения позиционного сумматора и первыми входами элементов И первой группы, вторые входы которых подключены к первому выходу блока переполнения позиционного сумматора, а выходы — к первым входам группы элементов ИЛИ, вторые входы которой соединены с выходами элементов.И второй группы, а выходы являютСя выходами сумматора по модулю, первые входы элементов И второй группы подключены к выходам непоэиционного сумматора, вторые входы — к второму выходу блока переполнения позиционного сумматора, а первая группа входов позиционного сумматора подключена к выходам блока инвертирования кода, вторая группа входов — к шинам второго числа (2).

Основным недостатком прототипа является значительный объем оборудования, необходимый для его реализации, что обусловлено использованием позиционного сумматора, состоящего из сумматора без распространения переносов и сумматора с распространением переносов, непоэиционного сумматора, представляющего собой сумматор с распространением переносов, первой и второй групп элемен-. тов И, а также группь элементов ИЛИ.

Цель изобретения — сокращение объема оборудования.

Поставленная цель достигается тем, 5 что устройство для сложения по модулю, содержащее первый и второй сумматоры и одноразрядный сумматор, первый и второй входы которого соединены с входами младших разрядов

1О модуля и nepaoro операнда устройства соответственно, первые входы разрядов первого сумматора соединены с входами старших разрядов первого .операнда устройства, выход перено15 са одноразрядного сумматора соединен с входом переноса второго сумма.тора, кроме того, выходы разрядов первого сумматора соединены с первыми входами разрядов второго сумматора, вторые входы j-х разрядов вто20 т рого сумматора (=-1, если а =-1

Tl

a; e {- л, м = у-,„. д 1-(М пр и M четном М-1= Х О; а при =1 нечетном) соедине ны с выходом пр ямого значения переноса первого сумматора, вторые входы остальных разрядов второго сумматора соединены с. выходом инверсного значения переноса

ЗО первого сумматора, третий вход одноразрядного сумматора соединен с входом младшего разряда второго операнда устройства, вторые входы разрядов первого сумматора соединены с входа35 ми старших разрядов второго операнда устройства, выходы разрядов второго сумматора и выход суммы одноразрядного сумматора являются выходами устройства.

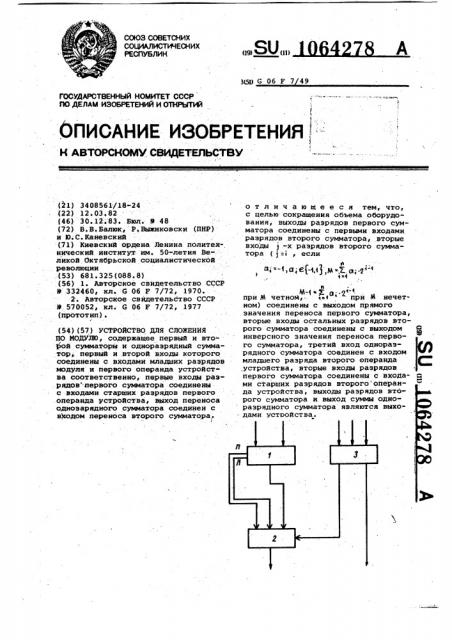

40 На чертеже представлена схема предлагаемого устройства..

Устройст во содержит первый ll -разрядный сумматор 1, первый и второй входы каждого разряда которого яв45 ляются соответственно входами разрядов первого и второго операндов, а выход суммы каждого разряда соединен с первым входом соответствующего разряда второго и -разрядного сумматора 2.

Выход переноса из старшего разряда сумматора 1 выполнен с вторыми входами разрядов сумматора 2 следующим образом.

Разряды сумматора 2, номера кото-. рых соответствуют разрядам кода числа М для М нечетного или числа М-1 для М четного, представленного в системе счисления с цифрами -1 и 1,, 60 в которых зафиксирована цифра -1, соединены с прямым выходом переноса из старшего. разряда сумматора 1, а остальные разряды сумматора 2 соединены с инверсным выходом переноса из старшего разряда сумматора 1, 1064278

Составитель В. Евстегнеев

Редактор A. Власенко Техред М. Гергель Корректор О. Билак

Заказ 10532/49 Тираж 706 Подписное.

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035 Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r.Óæroðoä, ул.Проектная, 4

Выходы разр ядов сумматора 2 являют-, ся выходами старших разрядов устройства, а его вход переноса соединен с выходом переноса одноразрядного сумматора 3, выход суммы которого является выходом младшего разряда 5 устройства, а первый, второй и третий входы являются входами младших разрядов соответственно модуля М, первого и второго операндов.

Устройство работает следующим об- 1О разом.

На первый вход одноразрядного сумматора 3 пост"упает младший разряд двоичного кода модуля М,„ а на его остальные входы и входы сумма- )5 тора 1 поступают (И+1)-разрядные двоичные операнды со знаком, представленные в дополнительном коде, знаковый разряд которого проинвертирован. При этом на второй и третий входы одноразрядного сумматора

3 поступают младшие разряды соот- ветственно первого и второго операндов, а на первый и .второй входы сумматора 1 поступают остальные разряды первого и второго операндов соответственно. После того как на выходе переноса иэ старшего разря- . да сумматора 1 образуется сигнал переноса, под его воздействием за счет соответствующей коммутации на входах сумматора 2 сформируется представленный в системе счисления с цифрами -1 и 1 код модуля -N или

-(М-1). для М нечетного или четного соответственно. Гсли сигнал переноса не образовался, на входах сумматора 2 формируется представленный в системе счисления с цифрами -1 и 1 код числа М или числа (М+1) для М нечетного или четного соответственно. Одновременно код, сформированный на.выходе суммы сумматора 1, поступает на первый вход сумматора 2, на вход переноса которого поступает сигнал переноса, образовавшийся на выходе переноса одноразрядного сумматора 3. Затем сумматор 2 производит суммирование кодов, поступивших на

его входы, формируя, таким образом, на выходах устройства все разряды результата, за исключением младшего разряда, который формируется на выходе суммы одноразрядного сумматора

3 обычным образом. При этом получаемый результат .представлен в дбполнительном коде с инверсным значением знакового разряда.

Таким образом, уменьшение объема оборудования по сравнению с известным устройством обусловлено тем, что вместо и-разрядного сумматора беэ распространения переноса, двух и-разрядных сумматоров с распространением переносов, первой и второй групп эЛеМентов И и группы элементов ИЛИ, используемых в базовом объекте, в данном устройстве применяются только два и-разрядных сумматора и одноразрядный сумматор. Отпадает необходимость использования h -разрядного сумматора беэ распространения переносов, двух групп элеМентов

И и группы элементов ИЛИ.