Элемент памяти для накопителя с произвольной выборкой

Иллюстрации

Показать всеРеферат

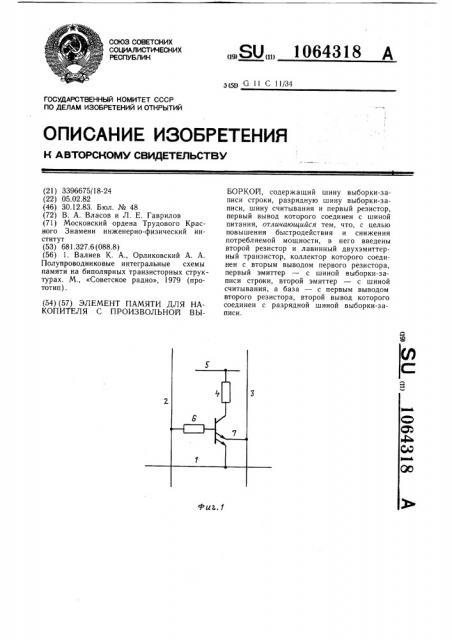

ЭЛЕМЕНТ ПАМЯТИ ДЛЯ НАКОПИТЕЛЯ С ПРОИЗВОЛЬНОЙ ВЫБОРКОЙ , содержащий шину выборки-записи строки, разрядную шину выборки-записи , шину считывания и первый резистор, первый вывод которого соединен с шиной питания, отличающийся тем, что, с целью повышения быстродействия и снижения потребляемой мош,ности, в него введены второй резистор и лавинный двухэмиттерный транзистор, коллектор которого соединен с вторым выводом первого резистора, первый эмиттер - с шиной выборки-записи строки, второй эмиттер - с шиной считывания, а база - с первым выводом второго резистора, второй вывод которого соединен с разрядной шиной выборки-записи . (Л о О5 j; со 00 fUZ. 1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК а 511 G 11 С 11/34

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCKOMY СВИДЕТЕЛЬСТВУ

Фиг. 1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3396675/18-24 (22) 05.02.82 (46) 30.12.83. Бюл. № 48 (72) В. А. Власов и Л. Е. Гаврилов (71) Московский ордена Трудового Красного Знамени инженерно-физический институт (53) 681.327.6 (088.8) (56) 1. Валиев К. А., Орликовский А. А.

Полупроводниковые интегральные схемы памяти на биполярных транзисторных структурах. М., «Советское радио», 1979 (прототип). (54) (57) ЭЛЕМЕНТ ПАМЯТИ ДЛЯ НАКОПИТЕЛЯ С ПРОИЗВОЛЬНОЙ ВЬ1„„SU„, 1064318 A

БОРКОЙ, содержащий шину выборки-записи строки, разрядную шину выборки-записи, шину считывания и первый резистор, первый вывод которого соединен с шиной питания, отличающийся тем, что, с целью повышения быстродействия и снижения потребляемой мощности, в него введены второй резистор и лавинный двухэмиттерный транзистор, коллектор которого соединен с вторым выводом первого резистора, первый эмиттер — с шиной выборки-записи строки, второй эмиттер — с шиной считывания, а база — с первым выводом второго резистора, второй вывод которого соединен с разрядной шиной выборки-записи.!

0643!8! !зобрстс1111с (ттносится к импульснои

l(1:Il. (,:;рс 1 ill illilчсHo для цифровых на1«,>11 313О, IéIIOH BbI60PI(OH H MO>KCT быть 1с ь3«1„lilo (3 интегральных быстрого с " -> 11 За11ом11нак>1цих устроис твах. 5 ! !1111б . t(е блпзк;1м к предлагаемому по т(11ичс(hoii сх 1ц(1(3сти является элемент

1гамяти, который содержит два двухэмиттерных транзистора, коллекторы которых сое ;(11 нены с шиной питания через сопротивлсния, первы(эмиттеры — с шинои выборки строки, а вторые эмиттеры — с разрядными шинами записи-считывания. С целью получения элемента с памятью заведены перекрестные связи с базы одного транзистора на коллетор другого и наоборот (!).

Недостатком известного элемента является постоянное потребление мощности от источника питания, связанное с тем, что транзист р исторы, составляющие элемент памяти, находятся постоянно в противоположных состояниях (закрыт-открыт).

К оме того, значительная коллекторная емкость, которая появляется из-за подключения к коллектору одного транзистоа базы другого и малого напряжения на коллекторе (не более Uw открытого транзистора), ), ограничивает быстродействие устройства.

Цель изобретения — повь(шение быстродействия и снижение потребляемой мощности.

Поставленная цель достигается тем; что в элемент памяти для накопителя с произвольной выборкой, содержащий шину выборки-записи строки, разрядную шину выборки-записи, шину считывания и первый резистор, первый вывод которого соединен с шиной питания, введены второй резистор и лавинный двухэмиттерный транзистор, коллектор которого соединен с втоа пе вый 40 рым выводом первого резистора, п р эмиттер — с шиной выборки-записи строки, второй эмиттер — с шиной считывания, а база — с первым выводом второго резистора, второй вывод которого соединен с разрядной шиной выборки-записи.

На фиг. 1 изображен элемент памяти; на фиг. 2 — эпюры управляющих сигналов в различных режимах.

Элемент памяти для IIdI(OIIIIT iii . ч13 вольной выборкой содержит шинi !,:.ьЯ(1рки-записи строки, разрядную шин 2 выборки-записи, шину 3 считывания, первый резистор 4, шину 5 питания, второй резистор 6 и лавинный двухэмиттерный транзистор 7, П едлагаемое выполнение элемента паP мяти обеспечивает его более высокое быстродействие, так как лавинный транзистор принципиально обладает более высоким быстродействием, чем обычный биполярный транзистор. Использование в эле менте памяти одного активного элемента— лавинного транзистора — позволяет упростить схему и получить экономичный элемент памяти, который в одном из состояний нс потребляет мощности от источника питания.

Вольтамперная характеристика лавинного транзистора со стороны базы отличается от вольтамперной характеристики обычного биполярного транзистора наличием частка отрицательного дифференциальУ ного сопротивления. Благодаря этому, дпоключив к базе сопротивление, можно получить чить гистерезисную переключательную характеристику между эмиттером и вторым выводом базового резистора.

Для управления элементом памяти используется система сигналов, представленная на фиг. 2, где U< — потенциал на шине выборки-записи строки, U — потенциал на разрядной шине выборки-записи, U — потенциал на шине считывания.

Элемент работает следующим образом.

Для записи информации на шину 1 выборки-записи строки и разрядную шину н 2 выборки-записи подают разнополярные импульсы. При этом потенциал на шине 3 считывания всегда выше, чем на разрядной шине выборки-записи.

При считывании потенциал шины 3 считывания понижается и ток (если транзистор находится в проводящем состоянии) пе еключается из первого эмиттера во второй эмиттер транзистора 7, т. е. в ш у пер шин

3 считывания.

Используемый в элементе памяти активный элемент — лавинный транзистор— — обладает по сравнению с обычным биполярным транзистором большим (на 1-2 порядка) быстродействием и большими схемотехническими возможностями.

l064318

Сч. „

Составитель О. Кулаков

Редактор Ю. Ковач Техред И. Верес Корректор И.Муска

Заказ 0448/51 Тираж 594 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )K — 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4