Преобразователь биполярного кода в однополярный

Иллюстрации

Показать всеРеферат

ПРЕОБРАЗОВАТЕЛЬ БИПОЛЯРНОГО КОДА В ОДНОПОЛ Я РНЫЙ по авт.. ев, № 1003334, отличающийс я тем, что, с целью повышения помехоустойчивости, в него введег ы два резистора, причем перзый резистор включен между выходом первого ключевого элемента и обратносмащенным входом первого дифференциального усилителе, .а второй резистор - между выходом второго ключевого элемента и обратносмещенным входом второго дифференциального усилителя

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

3(Я) Н 03 К 13 24

0llHGAHHE ИЗОБРЕТЕНИЯ К A8T0PCHOMV СВИДЕТЕЛЬСТВУ $8

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 1003334 (21) 3504952/18-21 (22) 26,10.82. (46) 30.12, 83, Бюл 9 48 (72) Л.К.Самойлов, В,B,Ãàéâîðoíский и С . П. Тжккун (71) Таганрогский радиотехнический институт им. В.Д.Калмыкова (53) 681.325. 3(088. 8) (54) (57) ПРЕОБРАЗОВАТЕЛЬ БНПОЛЯРНОГО КОДА В ОДНОПОЛЯРНЫЙ по авт.

„„SU„„10644 9 А св. 9 1003334, о т л и ч а ю щ и й-, с я тем, что, с целью повыаения помехоустойчивости, в него введены два реэистора, причем перзый реэистор включен между выходом первого ключевого элемента и обратносмещенным входом первого дифференциального усилителя, а второй реэистор — между выходом второго ключевого элемента и обратносмещенным входом второго дифференциального усилителя

1064459

Изобретение относится к импульс- ной технике и предназначено для приема и преобразования кодовых сигналов (однополярных или двуполярных).

По основному авт.св - Р 1003334 5 известен преобразователь биполярного кода в однополярный, содержащий два дифференциальных усилителя, два ключевых элемента,.четыре делителя, два фильтрующих конденсатора, элемент ИЛИ и выходной усилитель, причем к первому входу устройства подключены входы первого и второго делителя, к второму входу устройства подключены входы третьего и четвертого делителей, первый и второй фильтрующие конденсаторы включены соответственно между входами первого и второго дифференциальных усилителей, выходы первого и четвертого делителей с прямосмещенными входамч соответственно первого и второго дифференциальных усилителей, обратносме-. щенные входы которых соединены с выходами соответственно третьего и второго делителей, выходы первого и второго дифференциальных усилителей соответственно через перзый и второй ключевые элементы соединены с входами элемента ИЛИ, выход, которого соединен с выходом синхронизации устройства, выход второго ключевого элемента через выходной усилитель подключен к инфор.мационному выходу устройства.

Недостатком известного устройства является низкая помехозащищенность при работе устройства с, входными сигналами, близкими к порогу переключения, из-за появле- 4О ния на входах устройства дифференциального напряжения близкого к порогу срабатывания, при этом дифференциальный усилитель переходит в линейный Режим работы . 45 и под воздействием дестабилизирующих факторов: пульсаций напряжений питания, наводок в общей шине, парафазных помех на входе, — появляется высокочастотный звон, что ослож-. няет работу последующих блоков.

Цель изобретения — повышение помехоустойчивости. !

Поставленная цель достигается тем, что в преобразователь биполярйого кода в однополярный, содер- жащий два дифференциальных усилителя, два ключевых элемента, четыре делителя, рща фильтрующих конденсатора, элемент ИЛИ и выходной усилитель, причем к первому входу 60 устройства подключены входы первого и второго делителей, к второму входу устройства подключены входы третьего и четвертого делителей, первый и второй филътрующие кон- 65 денсаторы включены соответствен- . но между входами первого и второго дифференциальных усилителей, выходы первого и четвертого делителей соединены с прямосмещенными входами соответственно первого и второго дифференциальных усилителей, обратносмещенные входы которых соединены с выходами соответственно третьего и второго делителей, выходы первого и второго дифференциальных .усилителей соответственно через первый и второй ключевые элементы соединены со входами элемента ИЛИ, выход которого является выходом синхронизации устройства, выход второго ключевого элемента через выходной усилитель подключен к информационному выходу устройства, введены два резистора, причем первый резистор включен между выходом первого. ключевого элемента и обратносмещенным,вХОдом первого дифференциального усилителя, а второй резистор - между выходом второго ключевого элемента и обратносмещенным входом второго дифференциального усилителя.

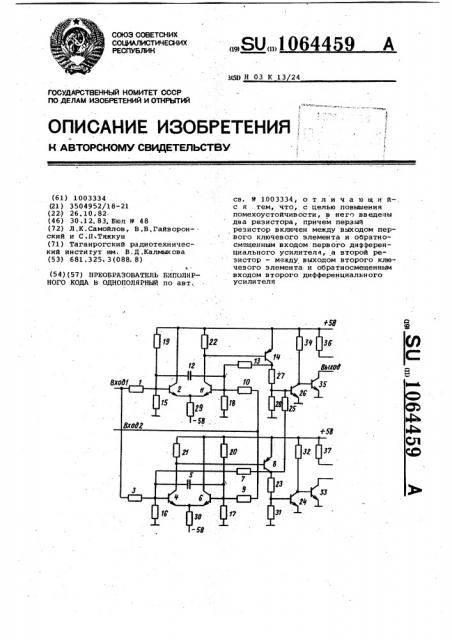

На чертеже изображена принципиальная схема устройства °

Первый вход устройства через резистор 1 соединен с базой транзи" .стора 2, а через резистор 3 с базой транзистора 4, которая через фильтрующий конденсатор 5 соединена с базой транзистора б, через резистор 7 соединена с коллектором транзистора 8, второй вход устройства через резистор 9 соединен с баЗой транзистора б, а через резистор 10 с базой транзистора 11-, — " которая через фильтрующий конденсатор .12 соединена с базой транзисто ра 2, а через резистор 13 с кол:лектором транзистора 14, базы транзисторов 2, 4, б и ll соединены с общей шиной соответственно через резисторы 15, 16, 17 и 18, Базы транзисторов 2 и б соединены с шиной источника питания и коллекторами этих транзисторов через резисторы 19 и 20, коллекторы транзисторов

4 и ll соединены с шиной источника питания через резисторы 21 и 22 и с базами транзисторов 8 и 14, эмиттеры которых соединены с шиной источника питания, коллектор транзистора 8 через резистор 23 соединен с базой транзистора 24, а через резистор 25 с базой транзистора 26, которая через резистор

27 соединена с коллектором транзистора 14., а через резистор 28 с общей шиной. Эмиттеры транзистоpos 2 и 11 соединены между собой и через резистор 29 соединены с другой шиной источника питания, эмиттеры транзисторов 4 и 6 соединены между собой и через резистор 30

1064459

Составитель С, Кривуценко

Техред И.Метелева .„„. Корректор О Билак

Редактор И Руднева

Заказ 10361f59 Тираж 936 Подпи сн се

ВНИИПИ Государственного комитета CCCP по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб ° д 4/5

Филиал ППП Патент, o oужгород, ул Проектная, 4 также соединены с другой шиной источника питания, база транзистора

24 через резистор 31 соединена с общей шиной, а коллектор через резистор 32 соединен с шиной источника питания и с базой транзистора"; 5

33, коллектор которого является выходом информации уотройства, Коллектор транзистора 26 через резистор 34 соединен с шиной источника питания и с базой транзистора 35, коллектор которого является выходом синхронизации устройства. Пре- образователь содержит резисторы 36 и 37.

Первый дифференциальный Усилитель реализован на транзисторах

2 и 11 и резисторах 19, 22 и 29, второй - на транзисторах 4 и б и резисторах 20, 21. и 30.. Первый делитель содержит резисторы 1 и 15, второй - резисторы 3 и 16, третий — . резисторы 10 и 18, четвертый — резисторы 9 и 17. Первый ключевой элемент выполнен на транзисторе 14, второй ключевой элемент на транзисторе 8 . Элемент ИЛИ содержит резисто» 25 ры 25, 27, 34 и 36, транзисторы

26 и 35. Вьыодной усилитель состоит иэ резисторов 23, 31,. 32 и 37 и транзисторов 24 и 33.

Устройство работает следующим 3Q образом .

При.дифференциальном напряжении между первым и вторым входами по модулю меньше пороговой величины, задаваемой резисторами 19„ 15 и Э5

20, 37 в первом и втором дифференциальных усилителях, транзисторы

2 и 6 открыты, транзисторы ll и 4 закрыты, закрыты транзисторы 8, 14, .24 и 26, а транзисторы ЗЗ и 35 открыты и на обоих выходах устрой- . ства установлены сигналы, соответ-ствующие низкому уровню . Резисторь1

Зб и 37 образуют внутреннюю нагрузку и при необходимости могут быть соединены с коллекторами транзисторов 35 и 33,, При синфазном изменении напряжения (+ 10 В) на входах устройство остается в исходном состоянии. При изменении дифференциального напряжения на входах выше порогового уровня в зависимости от полярности входного напряжения либо откроются транзисторы 8, 26 и 24 и на выходах появятся сигналы высоких уровней, либо откроются транзисторы 14 и 26 и на выходе синхронизации (транзисторе 35) установится высокий уровень, а на выходе (транзисторе 33) . — низкий, Реэистивные делители входного напряжения совместно с конденсаторами 5 и 12 образуют интегрирующие звенья первого порядка, выполняющие частичное подавление высокочастотных помех.

Включение в преобразователь резисторов 7 и 13 приводит к появлеч нию гистерезиса в ее передаточной характеристике, что эквивалентно повышению помехозащищенности устройства .

При достижении дифференциальным входным сигналом порога срабатывания и отпирания .транзистора, 14 или 8 порог срабатывания скачкомменяется в сторону уменьшения (на величину напряжения, приведенного к входу устройства, 1,0-1,2 В)

При уменьшении входного сигнала до нового порога переключения (задний фронт импульса) запираются транзистор 8 или 14, а порог скачком увеличивается ° Таким образом, суммарная величина дестабилизирующих факторов, приведенная к входу менее 1,0-1,2 В, не вызывает ложных переключений в схеме.