Многофункциональный логический элемент на мдп-транзисторах

Иллюстрации

Показать всеРеферат

МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ, содержащий первый, второй и третий информационные транзисторы п-типа, включенные последовательно, четвертый , пятый и шестой информационные транзисторы п-типа, включенные после-, довательно, четыре входные шины, шины прямого и инверсного сигнала управления, о т.пл ичающийся тем, что, с целью повышения надеж .ности, первый, второй и третий информационные транзисторы включены между выходной и общей шинами четвертый , пятый и шестой информационные транзисторы включены между выходной и общей шинами, первый, второй и третий нагрузочные транзисторы р-типа включены последовательно между шиной источника питания и выходной шиной, четвертый, пятый и шестой нагрузрчныё; транзисторы р-типа включены последовательно между шиной источника питания и выходной шиной, сток первого блокирующего транзистора р-тйпа соединен с шиной источника питания, а исток подключён к стоку третьего .нагрузочг ного транзистора р-типа, сток первого коммутирующего транзистора р-типа подключен к стоку второго на рузочного транзистора р-типа, а исток соединен со стоком шестого нагрузочного транзистора р-типа,сток второго коммутирующего транзистора р-типа подключен к стоку пятого нагрузочного транзистора р-типа, а исток соединен с выходной шиной, сток второго блокирующего транзисГтора п-типа соединен с общей шиной, а исток подключен к стоку первого информационного транзистора п-типа, сток третьего коммутирующего транзистора п-типа подключен к стоку второго информационного транзистора п-типа, а исток - к стоку четвертого информационного транзистора п-типа, сток четвертого коммутирующего транзистора .п-типа подключен к стоку пятого нагрузочно-го транзистора р-типа, а исток соединен с выходной шиной, сток второго блокирующего транзистора п-типа . соединен с общей шиной, а исток подключен к стоку первого информаен ционного транзистора п-типа, сток третьего коммутирующего транзистора п-типа подключен к стоку второго информационного транзистора ,п-типа, а исток - к стоку четвертого информационного транзистора п-типа , сток четвертого коммутирующего транзистора п-типа подключен к стоку пятого информацнон ного транзистора п-типа, а исток соединен с выходнойпшиной, затворы 4i первого нагрузочного транзистора vl р-типа и третьего информационного транзистора п-типа соединены с первой входной шиной, затворы второго нагрузочного транзистора р-типа и второго информационного тра нзистора .п-типа соединеныс второй входной шиной , затворы пятого нагрузочного транзистора р-типа .и пятого информа-ционного транзисшрра гт-типа соединены с третьей входной шиной, затворы шестого нагрузочного транзистора р-типа и четвер.того информационного транзистора п-типа соединены с четвертой входной шиной, затворы первого и шестого информационных тран зисторов п-типа и третьего и четвер

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (И) 3(50 Н 03 К 1 9/09 4

»

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

Ю

Cb

«Дь

Ю

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3493429/18-21 (22) 27.09.82 (46) 30.12.83. Бюл. Р 48 (72) С.В.Быков (53) 621.374(088.8) (56) l. Авторское свидетельство СССР

М 851397, кл. Н 03 К 19/08, 1981.

2. Каталог элементов ХА3.487.

152ЭЗ . (54) (57) МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ HA МДП-ТРАНЗИСТОРАХ, содержащий первый, второй и третий информационные транзисторы н -типа, включенные последовательно, четвертый, пятый и шестой информационные транзисторы и -типа, включенные после-. довательно, четыре входные шины, шины прямого и инверсного сигнала управления, о т.>.л и ч а ю шийся тем, что, с целью повышения надеж.ности, первый, второй и третий информационные транзисторы включены между выходной и общей шинами, четвертый, пятый и шестой информационные транзисторы включены между выходной и общей шинами, первый, второй и тре. тий нагрузочные транзисторы р-типа включены последовательно между шиной источника питания и выходной шиной, четвертый, пятый и шестой нагруэочные транзисторы р -типа включены последовательно между шиной источника питания и выходной шиной, сток первого блокирующего транзистора р-типа соединен» с шиной источника питания, а исток подключен к стоку третьего нагрузоч-, ного транзистора р-типа, сток первого коммутирующего транзистора р-типа подключен к стоку второго нагрузочного транзистора р -типа,а исток соединен со стоком шестого нагрузочного транзистора р-типа, сток второго коммутирующего транзистора р-типа подключен к стоку пятого нагрузочного транзистора р-типа, а исток соединен с выходной шиной, сток второго блокирующего транзистора и -типа соединен с общей шиной, а исток подключен к стоку первого информационного транзистора П-типа, сток третьего коммутирующего транзистора и -типа подключен к стоку второго информационного транзистора п-типа, а исток к стоку четвертого информационного транзистора п-типа, сток четвертого коммутирующего транзистора и--типа подключен к стоку пятого нагрузочно-. го транзистора р -типа, а исток соединен с выходной шиной, сток второго блокирующего транзистора и-типа .соединен с общей шиной, а исток подключен к стоку первого информа- Р9 ционного транзистора п-типа, сток третьего коммутирующего транзистора и-типа подключен к стоку второго ин. формационного транзистора,п-типа, а исток - к стоку четвертого информационного транзисторà и-ти- Ф па, сток четвертого коммутирующе ro транэ истора л -типа подключен к стоку пятого информационного транзистора и -типа, а исток соединен с выходнойяшивой, затворы первого нагрузочного транзистора р-типа и третьего информационного транзистора и-типа соединены с первой входной шиной, затворы второго нагрузочного транзистора р-типа и второго информационного транзистора ,и-типа соединены с второй входной ши ной, затворы пятого нагрузочного транзистора р-типа .и пятого информационного транзис»грра п -Tèïà соединены с третьей входной шиной, затворы шестого нагрузочного транзистора р-типа и четвертого информационного транзистора и-типа соединены с четвертой входной шиной, затворы первого и шестого информационных тран" зисторов и-типа и третьего и четвер1064470

20 того нагрузочных транзисторов р-типа соединены с шиной прямого сигнала управления„затворы коммутирующих

Изобретение относится к вычислительной технике и может быть использовано при разработке универсальных и специализированных цифровых вычислительных машин.

Известен многофункциональный логический элемент, содержащий два элемента равнозначности и элЕмент И, элемент НЕ, причем каждый .элемент равнозначности имеет один информационный и один управляющий входы-, входы элементов равнозначности подключены к.входам элемента И, выход которого соединен с ирямым выходом логического элемента и с входом элемента НЕ, выход которого связан с инверсным выходом логического элемента Г13.

Недостатком известного устройства является. низкая надежность схемы, виду большого числа аппаратных средств, что определяется избыточной функциональной возможностью данного устройства.

Наиболее близким к предлагаемому является многофункциональный логический элемент на ЬЩП-транзисторах, содержащий первый, второй и третий, информационные транзисторы и -типа, включенные последовательно, четвертый, пятый и шестой информационные транзисторы п-типа, включенные последовательно.четыре входныешины,шины прямого и инверсного сигнала управления (2 ).

Недостаток указанного элемента низкая надежность в виду большого числа компонентов схемы.

Цель изобретения — повышение

l надежности.

Поставленная цель достигается тем, что в многофункциональном логическом элементе на МДЩ-транзисторах, содержащем первый, второй и третий информационные транзисторы п-типа, включенные последовательно, четвертый, пятый и шестой информационные транзисторы и --типа, вклю-. ченные последовательно, четыре входные шины, шины прямого и инверсного сигнала управления, первый, второй и третий информационные тран зисторы включены между выходной и общей шинами, четвертый, пятый и шестой информационные транзисторы включены между выходной и общей шии блокирующих транзисторов соединены с шиной инверсного сигнала управления.

2 нами, первый, второй и третий нагрузочные транзисторы р -типа включены последовательно между шиной источника питания и выходной шиной, четвертый, пятый и шестой нагрузочные транзисторы р -типа включены последовательно между шиной источника питания и вы" ходной шиной, сток первого блокирующего транзистора р-типа соединен с шиной источника питания, а исток подключен к стоку третьего нагрузочного транзистора р-типа, сток первого коммутирающего транзистора р -типа подключен к стоку второго нагрузочного транзистора р-типа, а исток соединен со стоком шестого нагрузочного транзистора р-типа, сток второго коммутирующего транзистора р-типа подключен к стоку пятого нагрузочного транзистора р-типа, а исток соединен с выходной шиной, сток второго блокирующего транзистора и-типа соединен с общей шиной, а исток подключен к сто ку первого информационного транзистора и -типа, сток третьего коммутируще о транзистора n-THIGH подключен, стоку второго информационного транзистора и -типа, . а исток — к стоку четвертого информационного транзистора п-типа, сток четвертого

30 коммутирующего транзистора и -типа подключен к стоку пятого нагрузочного транзистора р-типа, а исток соединен с выходной шиной, сток второго блокирующего транзистора П --типа

35 соединен с общей шиной, а исток подключен к стоку первого Информационного транзистора и -типа, сток третьего коммутирукщего транзистора и-типа подключен к стоку второго

40 информационного транзистора и -типа, а исток — к стоку четвертого информационного транзистора H -типа, сток четвертого коммутирующего транзистора и -типа подключен к стоку пято45 го HH(f)QPMBL>+oHHoFQ TPBHBHGTQPB P -ти па, а исток соединен с выходной шиной, затворы первого нагрузочного транзистора р -типа и третьего информационного транзистора и --типа соединены с первой входной шиной,,затворы второго нагрузочного транзистора р-типа и второго информационного транзистора и-типа соединены с второй входной шиной, затворы пятого нагрузочного транзистора р-типа и

1064470

ВНИИПИ Заказ 10361/59 Тираж 936 Подписное

Филиал ППП "Патент", г.ужгород,ул.Проектная,4 пятого информационного транзистора и-типа соединены с третьей входной

Миной, затворы шестого нагруэочного транзистора р -типа и четвертого информационного транзистора и -типа соединены с четвертой входной шиной, затворы первого и шестого информационных транзисторов и-типа и третьего и четвертрго -нагрузочных транзисторов р-типа соединены с шиной прямого сигнала управления, затворы. коммутирующих .и блокирующих транзисторов соединены с шиной инверсного сигнала управления.

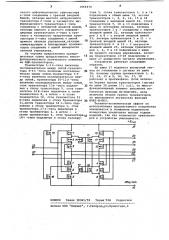

На чертеже представлена принципиальная схема предлагаемого многофункционального логического элемента на ИДП-транзисторах.

Транзисторы 1-3 h -типа включены последовательно между собой.транзис-. торы 4-6п -типа включены последовательно между собой, транзисторы 7-9 и-типа включены последовательно между собой, транзисторы 10-12 р -типа включены последовательно между, собой, сток транзистора 13р -типа подключен к стоку транзистора 9, сток тоанзистооа 14 р -типа подключен к стоку тюанзистооа 8, а исток — к стоку транзистора 12, сток тьанзистооа 15 п-.типа подключен к стоку. Транзистора

11,исток транзистора 16 и-типа под- ключен к стоку транзистора 1, сток транзистора.,17 и -типа подключен к стоку транзистора 2, а исток — к ,стоку транзистора 4, сток транзистора

18 п -типа подключен к стоку транзистора 5, стоки транзисторов 3, б и 16 подключены к общей шине 19, истоки транзисторов 1, 4, 9, 12, 15 и 18 соединены с выходной шиной 20, стоки транзисторов 7, 10 и 13 подключены к шине 21 источника питания, затворы транзисторов 3 и 7 соединены с первой входной шиной 22, затворы транзисторов 2 и 8 — с второй входной шиной

23, затворы транзисторов 5 и 11 — с о третьей входной шиной 24, затворы транзисторов 4 и 12 — с четвеот п входной шиной 25, затворы транзисторов 1, б, 9 и 10 подключены к шине .

26 прямого сигнала управления, затво35 ры транзисторов 13-18 подключены к шине 27 инверсного сигнала управления..

Устройство работает следующим образом.

На шину 27 подается инверсный сигнал по отношению к сигналу на шине

26, поэтому группы транзисторов 1, 6, 13, 14, 15 и 9, 10, 16, 17, 18

- работают в противофазе. Если включена первая группа транзисТоров (сигнал

25 йа шине 26 равен 17; с 1), то много. функциональный элемент выполняет ло.! гическую функцию И2-ИЛИ-НЕ2, если включена вторая группа транзисторов, то выполняется логическая функция

30 ИЛИ2-5-НЕ2.

Технико-зкономический эффект от использования предлагаемого устройства заключается в повышении надежности вследствие увеличения выхода годных изделий, так как количество транзисторов в устройстве уменьшается.

+Аюит