Многофункциональный логический элемент на мдп-транзисторах

Иллюстрации

Показать всеРеферат

МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ, содержащий первый, второй информационные и первый коммутирующий транзисторы n-THiia, включенные последовательно , первый, второй нагрузочные транзисторы р-типа, включенные посл едовательно , две информационные шины , шины прямого и инверсного сигналов управления, сток .первого информационного транзистора h-типа соединен с общей шиной, сток первого нагрузочного транзистора р-типа соединен с шиной источника питания, затворы первого информационного п-типа и первого нагрузочного р-типа транзисторов соединены с первой информационной шиной , затворы второго информационного п-типа и второго нагрузочного р-типа транзисторов соединены с второй информационной ШИНОЙ, аатвор .первого коммутирующего транзистора п -типа соединен с шиной прямого сигнала упра .вления, от личающййся т&л, что, с целью повышения надежности , в него введены второй коммутирующий транзистор р-типа, который включен последовательно с первым и вторым нагрузочным транзисторами р-тйпа,первый р-типаи второй п-типа блокирующие транзисторы, третий р-типа и четвертый h-типа коммутирующие транзисторы, сток первого блокирующего транзистора р-типа соединен с шиной источника питания, к выходной шине подключены истоки первого, четвертого п-типа и второго, третьего р-типа коммутирующих транзисторов, к общей шине подключен сток второго блокирующего транзистора п-типа, йсток первого блокирующего тра.нзисi тора р-типа подключен к стоку второго коммутирующего транзистора р-типа, (Л сток третьего коммутирующего транзистора р -типа подключен к стоку второго нагрузочного транзистора р-типа , сток четвертого коммутирующего транзистора п-типа подключен к стоку 2 второго информационного транзистора п-типа, исток второго блокирующего транзистора п-типа подключен к стоку первого, коммутирующего транзистора О) п-типа, затвор второго коммутирующего 0 транзистора р-типа соединен с шиной прямого ригнала управления, затворы первого р-типа, второго л-типа блокирующйхои третьего р-типа, четвертого п-типа ксялмутирующих транзисторов соединены с шиной инверсного .сигналауправления .

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

3(58 H 03 К 19/094

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

\ (.21) 3497845/18-21 (22) 06.10.82 (46) 30.12.83. Бюл. 9 48 (72) С.В.Быков (53) 621.374 (088.8) (56) 1 ° Авторское свидетельство СССР

9,851397, кл. 6 06 F 7/00, 1981.

2. Каталог элементов ХАЗ, 487.130.ЭЗ. (54) (57) МНОГОФУНКЦИОНАЛЬНКЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ HA МДП-ТРАНЗИСТОРАХ, содержащий первый, второй информационные и первый коммутирующий транзисторы п-типа, включенные последовательно, первый, второй нагрузочные транзисторы р-типа, включенные пос- ледовательно, две информационные шины, шины прямого и инверсного сигналов управления, сток .первого информационного транзистора и-типа соединен с общей шиной, сток первого нагруэочного транзистора р-типа соединен с шиной источника питания, затворы первого информационного и -типа и первого нагрузочного р-типа транзисторов соединены с первой информационной шиной, затворы второго информационного и-типа и второго нагруэочного р-типа транзисторов соединены с второй ин-, формационной шиной, аатвор,первого коммутирующего транзистора и-типа соединен с шиной прямого сигнала управления, от личающийс я тем, что, с целью повышения надеж»

„„SU„„1064471 . А ности, в него введены второй коммутирующий транзистор р-типа, который включен последовательно с первым и вторым нагруэочным транзисторами р типа, первый р-типа и второй l1-типа блокирующие транзисторы, третий р-типа и четвертый и --типа коммутирующие транзисторы, сток первого блокирующего транзистора р -типа соединен с шиной источника питания, к выходной шине подключены истоки первого, четвертого и -типа и второго, третьего р -типа коммутирующих транзисторов, к общей шине подключен сток второго блокирующего транзистора п-типа,,исток первого блокирующего транзистора р-типа подключен к стоку второго Pg коммутирукчцего транзистора р-типа, сток третьего коммутирующего транзистора р-типа подключен к стоку второго нагруэочного транзистора р-ти- С па, сток четвертого коммутирующего транзистора и-типа подключен к стоку второго информационного транзистора п-типа, исток второго блокирующего транзистора:и -типа подключен к стоку (, ) первого коммутирующего транзистора п-типа, затвор второго коммутирующего транзистора р-типа соединен с шиной 14йЬ прямого дигнала управления, затворы первого р-типа, второго -типа блокирующй3ои третьего р-типа, четвертого 3 п-типа коммутирующих транзисторов а соединены с шиной инверсного .сигнала управления.

1064471

Изобретение относится к вычислительной технике и может быть использовано при разработке универсальных и специализированных цифровых вычислительных машин.

Известен многофункциональный логический элемент, содержащий два элемента равнозначности и элемент

И, элемент НЕ, причем каждый элемент равнозначности имеет один информационный и один управляющий входы, выходы элементов равнозначности подключены к входам элемента И, выход которого соединен с прямым выходом логического элемента и с входом элемента НЕ, выход которого связан с инверсным выходом логического элемента (1 j, Недостатком известного устройства является низкая надежность схемы ввиду большого числа аппаРатных средств, что определяется избыточной функционально возможностью данного устройства.

Наиболее близким к предлагаемому является многофункциональный логи-, ческий элемент, содержащий две информационные шины, шины прямого и инвер" сного сигналов управления, первый, второй информационные и первый коммутирующий транзисторы и --типа, включенные последовательно, первый, второй нагрузочные транзисторы р-типа, включенные последова- . тельно, двухвходовый логический элемент И-НЕ, два двухвходовых логических элемента ИЛИ-НЕ, тги логических 35 элемента НЕ, сток первого информационного транзистора.п --типа соединен с общей шиной, сток первого нагрузочного транзистора р-типа соединен .с шиной источника питания, затвоРы 40 первого информационного и-типа и первого нагрузочного р-типа транзис.торов соединены с павой информационной шиной, затворы второго информационного п-Tèïà и второго нагрузочного 45 р-типа транзисторов соединены с второй инйоомацианной шиной, затвор первого коммутирующего транзистора и-типа соединен с шиной прямого сигнала управления (2 1.

Недостаток ука за нного элемента низкая надежность ввиду бОльшого числа компонентов схемы..

Цель изобретения — повышение на дежности многофункционального логического элемента.

Для достижения поставленной цели в многофункциональный логический элемент на КдП- тра нзисторах, содержащий первый, второй информационные и первый коммутирующий транзисторы „. 60 п-.òèïà, включенные последовательно, первый, второй нагрузочные транзис торы р-типа, включенные последовательно, две информационные шины, шины прямого и инверсного сигналов- ;65 управления, сток первого информационного транзистора и -типа соединен с общей шиной, сток первого нагрузочного транзистора р-типа соединен с шиной источника питания, затворы первого информационного и -типа и первого нагрузочного р-типа транзисторов соединены с первой информационной шиной> затворы второго.информационного и -типа и второго нагрузочного р-типа транзисторов соединены с второй информационной шиной, затвор первого коммутирующего транзистора и -типа соединен с шиной прямого сигнала управления, введены второй коммутирующий тоанзистоо р-типа: который включен последовательно с первым и вторым нагруэочными транзис-, торами р-типа, первый р-типа и второй и-типа блокирующие транзисторы, третий р -типа и четвертый п-типа коммутирующие. транзисторы, сток первого блокирующего транзистора р -типа соединен с шиной источника питания, к выходной шине подключены истоки первого, четвертого и-типа и второго, третьего р-типа коммутирующих транзисторов, к общей шине подключен сток второго блокирующего транзистора п-типа, исток первого блокируэхего транзистора р-типа подключен к стоку второго коммутирующего транзистора р-типа;сток третьего коммутирующего транзистора р-типа подключен к стоку второго нагрузочного транзистора р -типа, сток четвертого коммутирующего транзистора и -типа подключен к стоку второго информационного транзистора П -типа, исток второго блокирующего транзистора и -типа подключенк стоку первого коммутирующего транзистора и -типа, затвор второго коммутирующего транзистора р-типа соединен с шиной прямого сигнала управления, затворы первого р-типа, второго и-типа блокирующих и третьего р-типа, четвертого и -типа коммутирующих транзисторов соединены с шиной, инверсного сигнала управления.

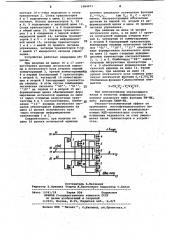

На. чертеже представлена принципи-. альная схема предлагаемого многофункционального логического элемента на

МДП-транзисторах.

Первый 1, второй 2 информационные и первый коммутируюший 3 транзисторы и-типа включены .последовательно, иервый 4, второй 5 нагрузочные и второй коммутирующий 6 транзисторы р-типа включены последовательно, исток первого блокирующего транзистора

7 р-типа подключен к стоку транзис- тора б, исток второг6 блокирующего

8 транзистора п.-типа подключен к стоку транзистора 3, сток третьего коммутирующего транзистора .9 р -типа подключен к стоку транзистора 5, сток четвертого коммутирующего тран1064471

+ Ение

16

Составитель A.Ìåçåíèåà.Редактор Е.Кривина Техред Ж.Кастелевич Корректор О.Билак

% и е

Заказ 10361/59 Тираж 936 Подписное

ВНИИЙИ ГосударствеииОго комитета СССР по делам изобретений:и открытий

113035, Москва, й-35 Раущская наб., д.4/5

Филиал ППП Патент,. г ужгород, ул.Проектная,4 эистора 10 и -типа подключен к стоку транзистора 2. Стоки транзисторов

4 и 7 подключены к шине ll источника питания. Истоки транзисторов 3, 10 и .6, 9 подключены к выходной шине 12.

Стоки транзисторов 1 и 8 подключены. ,к общей шине 13. Затворы транзисто- . ров 1 и 4 соединены с первой информационной шиной 14, затворы транзисторов.2 и 5 - с второй информационной шиной 15, затворы транзисторов

3 и 6 - с шиной 16 прямого сигнала управления, затворы транзисторов 7-10 с шиной 17 инверсного сигнала управления. устройство работает следующим -об- 15 разом.

При наличии на шинах 16 и 17 соответственно уровней логической единицы и логического нуля открыты первый коммутирующий 3, третий коммутирующий О

9" и первый блокирующий 7 транзисторы,. а второй 6, четвертый 10 коммутирующие и второй 8 блокирующий транзисто ры закрыты. В этом случае комбинация логических сигналов 00 ., 01, .25 10 на первой 14 и второй 15 информационных шннах обеспечивают фор мирование логической единицы на шине

12 через открытые нагрузочные тран-. зисторы 4 и 5 соответственно. Комби- ЗО нация 11. . входных логических сигналов обеспечивает формирование на шине 12 уровня логического нуля через. открытые информационные транзисторы 1 и 2.

Следовательно, при наличии на шйне 16 уровня логической единицы элемент реализует логическую функцию „= сх х, . где Х,, Х С вЂ” аргументы, соответствующйе логическим уровням на первой 14, второй 15 ин-. формационной шинах и. шине 16 прямого си гн ала управлени я.

При наличии на шине 16 уровня логического нуля, а на шине 17 уровня логической:единицы открыты второй 6, четвертый 10 коммутирующие и второй 8 блокирующий транзисторы.

Комбинации входных логических сигналов- 01 !, 10, 11 обеспечивают формирование логического нуля на шине 12 через открытые информационные транзисторы соответственно

2, 1, 1 и 2. Комбинация 00 через открытые нагрузочные транзисторы

4 и 5 обеспечивает формирование логической единицы на шине 12. Таким образом, при наличии на шине .16 уровня логического нуля элемент реализует логическую ф нкцию f> X ч „vc

Обобщенная. функция F,выполняемая элементом

F ся Х + х vjI Чс.

При использовании управляющего входа в качестве информационного элемент реализует либо функцию ЗИ-НЕ,: либо функцию ЗИЛИ-НЕ.

Технико-экономический эффект от применения многофункционального логического элемента на взаимодополняющих ИДП-транзисторах состоит в повышении надежности за счет уменьшения числа транзисторов в устрой- стве.