Усилитель-формирователь

Иллюстрации

Показать всеРеферат

УСИЛИТЕЛЬ-ФОРМИРОВАТЕЛЬ , содержащий усилительный каскад на трех инверторах, каждый из которых включает нагрузочный транзистор, сток которого соединен с шиной питания, исток подключен к стоку ключевого транзистора, истоки которых объединены, при этом затвор первого ключевого транзистора соединен с шиной входного сигнала и с затвором второго ключевого транзистора, затвор третьего ключевого транзистора соединен со стоком второго, и формирующий каскад на двух инверторах, каждый из которых содержит параллельно включенные нагрузочный транзистор с индуцированным кана.йом и нагрузочный транзистор с встроенным каналом, стоки которых соединены с шиной питания, истоки объединены и подключены к стоку соответствующего разрядного транзистора, затвор одного из которых соединен с затвором одного из нагрузочных транзисторов усилительного каскада, а затвор другого - с затвором соответствующего ключевого транзистора, исток - с шиной нулевого потенциала и с истоком блокирующего транзистора , отличающийся тем, что, с целью повышения его быстродействия при работе на емкостную нагрузку при уменьшении потребляемой мощности и упрощения переключения режимов работы, в него введены транзистор отсечки, сток которого соединен с истоками ключевых транзисторов, исток - с шиной Нулевого потенциала, а затвор подключен к шине управляющего сигнала, два разделительных транзистора, стоки которых являются соответственно инверсным и прямым входами усилительного каскада истоки подключены к затворам нагрузочных транзисторов формирующего каскада, а затворы подключены к шине управляющего сигнала, две форсирующие емкости, включенные каждая 5 между затворами и истоками соответствую (Л щей пары нагрузочных транзисторов формирующего каскада, второй и третий нагрузочные транзисторы усилительного каскада выполнены с встроенным каналом, причем затвор первого нагрузочного транзистора усилительного каскада соединен с П1иной питания, затвор второго соединен со стоком первого ключевого транзистора, затвор третьего нагрузочного транзистора усилительного каскада соединен со стоком третьего ключевого Ci транзистора, стоки блокирующих транзисел торов подключены к затворам соответствуюоо щих нагрузочных транзисторов формирую00 00 щего каскада, а затворы соединены со стоком транзистора отсечки. о// о//

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК у у б 11 С 7/00

ОПИСАНИЕ HSOEPE

Н АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3418268/18-24 (22) 06.04.82 (46) 07.01.84. Бюл. № 1 (72) В. П. Сидоренко, Н. И. Хцынский, А. А. Хоружий и С. В. Куриленко (53) 681.227.6 (088.8) (56) 1. Патент США № 4161040, кл. G 11 С ?/02, опублик. 1979.

2. Патент США № 4160291, кл. G 11 С 7/00, опублик. 1979 (прототип). (54) (57) УСИЛИТЕЛЬ-ФОРМИРОВАТЕЛЬ, содержащий усилительный каскад на трех инверторах, каждый из которых включает нагрузочный транзистор, сток которого соединен с шиной питания, исток подключен к стоку ключевого транзистора, истоки которых объединены, при этом затвор первого ключевого транзистора соединен с шиной входного сигнала и с затвором второго ключевого транзистора, затвор третьего ключевого транзистора соединен со стоком второго, и формирующий каскад на двух инверторах, каждый из которых содержит параллельно включенные нагрузочный транзистор с индуцированным каналом и нагрузочный транзистор с встроенным каналом, стоки которых соединены с шиной питания, истоки объединены и подключены к стоку соответствующего разрядного транзистора, затвор одного из которых соединен с затвором одного из нагрузочных транзисторов усилительного каскада, а затвор другого— с затвором соответствующего ключевого

ÄÄSUÄÄ 1065883 А транзистора, исток — с шиной нулевого потенциала и с истоком блокирующего транзистора, отличающийся тем, что, с целью повын ения его быстродействия при работе на емкостную нагрузку при уменьшении потребляемой мощности и упрощения переключения режимов работы, в него введены транзистор отсечки, сток которого соединен с истоками ключевых транзисторов, исток —с шиной нулевого потенциала, а затвор подключен к шине управляющего сигнала, два разделительных транзистора, стоки которых являются соответственно инверсным и прямым входами усилительного каскада, истоки подключены к затворам нагрузочных транзисторов формирующего каскада, а затворы подключены к шине управляющего сигнала, две форсирующие емкости, включенные каждая между затворами и истоками соответствующей пары нагрузочных транзисторов формирующего каскада, второй и третий нагрузочные транзисторы усилительного каскада выполнены с встроенным каналом, причем затвор первого нагрузочного транзистора усилительного каскада соединен с шиной питания, затвор второго соединен со стоком первого ключевого транзистора, затвор третьего нагрузочного транзистора усилительного каскада соединен со стоком третьего ключевого транзистора, стоки блокирующих транзисторов подключены к затворам соответствующих нагрузочных транзисторов формирующего каскада, а затворы соединены со стоком транзистора отсечки.

1065883

Изобретение относится к электронной и вычислительной технике и предназначено для использования в интегральных запоминающих устройствах в качестве усилителейформирователей входных и управляющих сигналов.

Известен усилитель-формирователь, содержащий усилительный каскад на двух бутстрепных инверторах, каждый из которых включает два нагрузочных транзистора, затвор первого и сток второго нагрузочных транзисторов соединены с шиной питания, сток первого нагрузочного транзистора с шиной первого управляющего сигнала, исток — с затвором второго нагрузочного транзистора и с одной обкладкой форсирующей емкости, вторая обкладка которой соединена с истоком второго нагрузочнаго транзистора и со стоками ключевого и блокирующего транзисторов, истоки которых соединены с шиной нулевого потенциала, затвор первого ключевого транзистора подключен к шине входного сигнала, затвор второго ключевого транзистора во втором бутстрепном инверторе — к стоку первого ключевого транзистора, затворы блокирующих транзисторов подключены к шине второго управляющего сигнала, и формирующий каскад на инверторах с перекрестными связями, каждый из которых содержит два параллельно включенных нагрузочных транзистора, стоки которых соединены с шиной питания, истоки объединены и подключены к стоку соответствующего разрядного транзистора, исток которого соединен с шиной нулевого потенциала, затвор одного из которых соединен с затвором первого нагрузочного транзистора первого инвертара и подключен к стоку второго ключевого транзистора усилительного каскада, а затвор другого — с затвором этого же ключевого транзистора и с затвором первого нагрузочного транзистора второго инвертора формирующего каскада, затвор второго нагрузоч- 4р наго транзистора подключен к шине третьего управляющего сигнала (1).

Недостатком указанного усилителя является низкое быстродействие при работе на большую емкостную нагрузку при малой 45 величине потребляемой мощности. Кроме того, в статическом режиме не компенсируются токи утечки в нагрузочных целях, что в конечном итоге приводит к нестабильНости выходных параметров устройства.

При этом в пассивном режиме — режиме с пониженным потреблением мощности на выходах усилителя-формирователя обеспечивается высокий уровень, что ограничивает применение быстродействующих дешифрирующих схем, реализованных по схеме 55

ИЛИ, так как их применение не позволяет существенно снизить в пассивном режиме

ЗУ потребляемую мощность.

Наиболее близким па технической сущности к предлагаемому является усилительформирователь, содержащий усилительный каскад на трех инверторах, каждый из которых включает нагрузочный транзистор, сток которого соединен с шиной питания, исток подключен к стоку ключевого транзистора, исток которого соединен с шиной нулевого потенциала, при этом затворы нагрузочных транзисторов соединены с шиной первого управляющего сигнала, затвор первого ключевого транзистора соединен с шиной входного сигнала, затвор вторего ключевого транзистора подключен к стоку первого, а затвор третьего ключевого транзистора соединен со стоком второго, и формирующий каскад на двух инверторах, каждый из которых содержит параллельно включенные нагрузочный транзистор с индуцированным каналом и нагрузочный транзистор с встроенным каналом, стоки которых соединены с шиной литания, истоки объединены и подключены к затвору нагрузочного транзистора с встроенным каналом и к стоку соответствующего разрядного транзистора, исток которого соединен с шиной нулевого потенциала, затвор одного из которых соединен са стоком третьего ключевого транзистора усилительного каскада, а затвор другого — с затвором этого же транзистора, при этом затвор каждого разрядного транзистора соединен со стоком соответствующего блокирующего транзистора, затвор которого соединен с затвором на грузочного транзистора с индуцированным каналом и с шиной управляющего сигнала, а исток — с шиной нулевого потенциала (2).

К недостаткам данного усилителя-формирователя относятся недостатки, характерные для усилителя (1). Крам< гаг . lë:; переключения усилителя-фармп1пиа .,i :I из активного режима работы в пасс- впь и и наоборот необходимо обеспечивать подачу двух управляющих сигналов, чта усложняет управляющую логику.

Цель изобретения — повышение быстродействия усилителя-формирователя при работе на большую емкостную нагрузку при малой величине потребляемой мощности и упрощение переключения режимов работы.

Поставленная цель достигается тем, что в усилитель-формирователь, содержащий усилительный каскад на трех инверторах, каждый из которых включает нагрузачный транзистор, сток которого соединен с шиной питания, исток подключен к стоку ключевого транзистора, истоки которых объединены, при этом затвор первого ключевого транзистора соединен с шиной входного сигнала и с затвором второго ключевого транзистора, затвоп третьего ключевого транзистора соединен со стоком второго, и формирующий каскад на двух ийверторах, каждый из которых содержит параллельно

1065883

3 включенные нагрузочный транзистор с индуцированным каналом и нагрузочный транзистор с встроенным каналом, стоки которых соединены с шиной питания, истоки объединены и подключены к стоку соответствующего разрядного транзистора, затвор одного из которых соединеН с затвором одного из нагрузочных транзисторов усилительного каскада, а затвор другого — с затвором соответствующего ключевого транзистора, исток — с шиНой Нулевого потенциала и с истоком блокирующего транзистора, дополнительно введены транзистор отсечки, сток- которого соединен с истоками ключевых транзисторов, исток — с шиной нулевого потенциала, а затвор подключен к шине управляющего сигнала, два разделительных транзистора, стоки которых являются соответственно инверсным и прямым входами усилительного каскада, истоки подключены к затворам нагрузочных транзисторов формирующего каскада, а затворы подключены к шине управляющего сигнала, две форсирующие емкости, включенные каждая между затворами и истоками соответствующей пары нагрузочных транзисторов формирующего каскада, второй и третий нагрузочные транзисторы усилительного каскада выполнены с встроенным каналом, причем затвор первого нагрузочного транзистора усилительного каскада соединен с шиной питаяия, затвор второго соединен со стоком первого ключевого транзистора, затвор третьего нагрузочного транзистора усилительного каскада соединен со стоком третьего ключевого транзистора, стоки блокирующих транзисторов подключены к затворам соответствующих нагрузочных транзисторов формирующего каскада, а затворы соедиНены со стокОм траизистора отсечки.

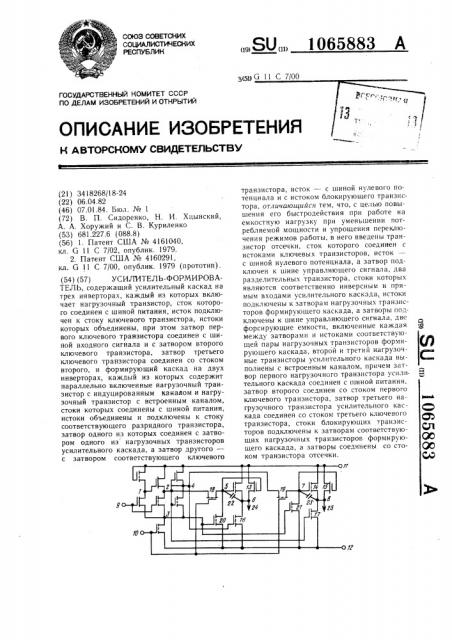

На чертеже предста влен а электри ческая схема предлагаемого усилителя-формирователя.

Усилитель-формирователь включает уси лительный и формирующий каскады. Усилительный каскад содержит три Нагрузочяых

МДП-транзистора 1 — 3, причем нагрузочные транзисторы 2 и 3 со встроенным каналом., три ключевых МДП-транзистора 4 — 6 с нндущ ровайным каналом, транзистор 7 отсечки а индуцмрованным каналом, шину 8 нитаниж, шину 9 вводимого аыд ала, шину 10 уиуэыявиипо ангнзла о цщ.ну ll нулевого попейцми.4ж

Формирующий каскад содержит четыре нагрузочных транзистора 12 — 15, причем натруаочные транзисторы 12 — 14 — МДПтранзисторы .с иидуцированным каналом, а earpyзочные транзисторы 13 и 15 — МДПтранзисторы с .встроенным каналом, два разрядных МДП-транзистора 16 и 17 с индуцированным каяалом, два разделительных МДП-транзистора 18 и 19 с индуцированным каналом, два блокирующих

МДП-транзистора 20 и 21 с индуцированНым каналом, две форсирующие емкости 22 и 23, а также инверсный 24 и прямой 25 выходы усилителя.

Усилитель работает в двух режимах: активном и пассивном.

Рассмотрим работу усилителя-формирователя в активном режиме. В этом режиме на шину 10 управляющего сигнала подает10 ся потенциал логической «1», открывающий транзистор 7 отсечки и разделительные транзисторы 18 и 19.

Если на входную шину 9 подается потенциал логического «О», то ключевые транзисторы 4 и 5 звпираютсн. Открытый транзистор 7 отсечки обеспечивает запирание блокирующих транзисторов 20 и 21. Емкостная Нагрузка первого инвертора усилительного каскада намного меньше емкостной нагрузки второго и третьего инверторов, вследствие чего процессы перезаряда в первом инверторе происходят быстрее, в результате быстро открывается нагрузочный транзистор 2 с встроенным каналом, работающий в крутой области и тем самым обеспечивающий максимальный ток заряда емкостной нагрузки второго инвертора и через открытый разделительный транзистор 18 ток заряда форсирующей емкости 22, формирующей напряжение на затворе нагрузочного транзистора 12. При этом ключевой транзистор 6 открывается и на выходе третьего инвертора устанавливается уровень логического «О», запирающий разрядный транзистор 16. Как только напряжение на затворе нагрузочного транзистора 12 становится выше порогового, нагрузочный транзистор 12 открывается и на его истоке появляется нарастающее напряжение, которое за счет положительной обратной связи приводит к перераспределению заряда форсирующей емкости 22, обеспечивающей на затворе нагрузочного транзистора 12 формирование напряжения, превышающего напряжение питания в нашем случае на 3 В (т.е. 8В), благодаря чему ускоряется процесс отработки сигнала логической «1» и напряжение питания полностью передается на инверсный выход усилителя-формирователя. Для ускорения процесса формирования сигнала логической «1», при заряде нагрузок с большей емкостью при малой величине потребляемой мощности используется второй Нагрузочный транзистор 13 с встроенным каналом, на затвор которого подается напряжение, превышающее напряжение литания затвора нагрузочного транзистора 12, вследствие чего при небольших геометрических размерах за счет высокой проводимости при работе в крутой области обеспечивается максимальный ток заряда. Кроме того, в статическом режиме нагрузочный транзистор 13 с встроенным

1065883

5 каналом обеспечивает компенсацию токов утечки в цепях затвора и истока нагрузочного транзистора 12, благодаря чему амплитуда сигнала логической «1» не снижается и поддерживается равной напряжению питания.

Затвор загрузочного транзистора 14 находится под потенциалом логического «О», а затвор разрядного транзистора 17 — под потенциалом логической «1», в результате на прямом выходе 25 усилителя-формирователя формируется сигнал логического «О».

Если на входную шину 9 подается потенциал логической «1», то ключевые транзисторы 4 и 5 открываются. На стоке ключевого транзистора 5 устанавливается нотеициал логического «О», запирающий ключевой транзистор 6, на стоке которого формируется потенциал логической «1», открывающий разрядный транзистор 16 и поступающий через разделительный транзистор 19 на затвор нагрузочного транзистора 14 и форсирующую емкость 23. В результате на прямом выходе 25 усилителя-формирователя формируется сигнал логической «1», а на инверсном выходе 24 — сигнал логического «О».

Для предотврашения стекания заряда с затвора нагрузочного транзистора 12 (14) в момент формирования на нем напряжения, превышающего напряжение питания, разделительный транзистор 18(19) выбран индуцированным.

Для исключения сквозных протекающих токов при отработке сигнала логического «О» нагрузочный транзистор 12(14), имеюший большой геометрический размер, выбран индуцированным, а ток через нагрузочные транзисторы 2(3) и 13(15), на затворах которых потенциал логического «О», незначителен. Таким образом, в схеме в активном режиме обеспечивается малая величина потребляемой мощности благодаря использованию минимального количества электрических цепей со сквозным протеканием тока.

В пассивном режиме на шину 10 управления подается потенциал логического «0», запирающий транзистор 7 отсечки и разделительные транзисторы 18 и 19. На стоке транзистора 7 отсечки устанавливается напряжение, близкое к напряжению питания, открываюшее блокирующие транзисторы 20 и 21, обеспечивающие установление уровня логического «О» на затворах нагрузочных транзисторов 12 — 15, что приводит к ограничению тока через встроенные нагрузочные транзисторы 13 и 15. Потенциал логической «1», устанавливающийся на выходах

5 !

О

35 второго и третьего инверторов схемы усиления, открывает разрядные транзисторы 6 и 17. В результате в режиме с пониженным потреблением мощности на прямом 25 и инверсном 24 выходах усилителя-формирователя формируется сигнал логического «0». В этом режиме схема усилителя-формирователя практически не потребляет мощности благодаря использованию транзистора 7 отсечки и разделительных транзисторов 18(19)> способствующих запиранию нагрузочных транзисторов 12(13) и ограничению тока нагрузочных транзисторов 14(15) с встроенным каналом.

Преимущество предлагаемого усилителяформирователя перед известными состоит в повышении быстродействия при работе на большую емкостную нагрузку при малой величине потребляемой могцносэ и. Кроме того, упрощается переключение режимов работы, во-первых,за счет введения форсирующей емкости и такого включения в формирующем каскаде нагрузочного транзистора с встроенным каналом, работающего в крутой области, которые обеспечивают крутой фронт при формировании сигнал логической «1», а во-вторых, за счет введения транзистора отсечки и двух разделительных транзисторов, обеспечивающих низкое потребление мощности путем загирания нагрузочных транзисторов с индуцированным каналом в формирующем каскаде к ограничения тока небольших по геометрическим размерам нагрузочных транзисторов с встроенным каналом. Г1ри этом .,ля переключения усилителя-формирователя из активного режима работы в пассивный и наэборот используется один управляюшии c Hãнал.

Применение предлагаемой схемы усилителя-формирователя в схемах ЭС ППЗУ позволяет повысить быстродействие этих схем ориентировочно на 20п/о, уменьшить потребляемую мошность Зу в целом в 1,5 раза в активном режиме и в 4 раза в режиме с пониженным потреблением мощности. Это обусловлено, во-первых, малым потреблением мощности адресными усилителямиформирователями, в качестве которых использована предлагаемая схема усилителяформирователя, во-вторых> в режиме с пониженным потреблением мощности на выходах прямого и инверсного сигналов обеспечивается уровень логического «0», что исключает сквозное протекание тока в цепях дешифраторов Х и V, принципиальная схема которых представляет собой схемы совпадения, обеспечивающие максимальное быстродействие.

ВНИИПИ Заказ 10709/51 Тираж 58) Подписное

Филиал ППП «Патент», r. Ужгород, ул. Проектная, 4