Динамическое запоминающее устройство

Иллюстрации

Показать всеРеферат

ДИНАМИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее накопители, коммутаторы, регистр числа, регистр запросов, блок управления и регистр адреса, выходы которого подключены соответственно к первым входам накопителей, коммутаторов и блока управления, первый и второй выходы которого соединены соответственно с первым входом регистра запросов и вторыми входами коммутаторов, выходы которых подключены к вторым входам накопителей, третья входы и выходы которых соединены соответственно с третьим выходом блока управления и входами регистра числа, выходы которых являются информационными выходами устройства , информационными входами которого являются четвертые входы накопителей. отличающееся тем, что, с целью уменьшения потребляемой устройством мощности, в него введены элемент ИЛИ, первая и вторая группы элементов И, группа элементов ИЛИ, первый и второй блоки приоритета, выходы которых подключены соответственно к второму входу блока управления и первым входом элементов И второй группы, выходы которых соединены с первыми вводами элементов ИЛИ группы и вторым входом регистра запросов, выход которого подключен к входам элемента ИЛИ и первым входам элементов И первой группы, выходы которых соединены с первым входом второго блока приоритета, выход которого подключен к третьим входам коммутаторов и пятым входам накопителей, шестые входы которых соединены с выходами элементов ИЛИ группы, выход элемента ИЛИ подклюсл чен к первому входу первого блока приоритета , второй, третий и четвертый входы которого соединены соответственно с третьим входом, четвертым и пятым выходами блока управления, четвертый вход и выходы с шестого по девятый которого подключены соответственно к выходу элемента ИЛИ и вторым входам элементов И групп, второго блока приоритета и элементов ИЛИ группы. О5 ел оо ас 05

СОЮЗ СОВЕТСКИХ социАлистических

РЕСПУБЛИК

G 11 С ll/34

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСНОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3492672/18-24 (22) 22.09.83 (46) 07.01.84. Бюл. № 1 (72) Л. И. Гончаров и В. В. Слюсарь (53) 681.327.6 (088.8) (56) I. Авторское свидетельство СССР № 506908; кл. G 11 С 7/00, 1973.

2. Заявка Японии № 54 — 2528, кл. 97(7) С опублик. 1979 (прототип). (54) (57) ДИНАМИЧЕСКОЕ ЗАПОМИHAIOIllEE УСТРОЙСТВО, содержащее накопители, коммутаторы, регистр числа, регистр запросов, блок управления и регистр адреса, выходы которого подключены соответственно к первым входам накопителей, коммутаторов и блока управления, первый и второй выходы которого соединены соответственно с первым входом регистра запросов и вторыми входами коммутаторов, выходы которых подключены к вторым входам накопителей, третьм входы и выходы которых соединены соответственно с третьим выходом блока управления и входами регистра числа, выходы которых являются информационными выходами устройства, информационными входами которого являются четвертые входы накопителей, „„SU„„1065886 A отличающееся тем, что, с целью уменьшения потребляемой устройством мощности, в него введены элемент ИЛИ, первая и вторая группы элементов И, группа элементов

ИЛИ, первый и второй блоки приоритета, выходы которых подключены соответственно к второму входу блока управления и первым входом элементов И второй группы, выходы которых соединены с первыми входами элементов ИЛИ группы и вторым входом регистра запросов, выход которого подключен к входам элемента ИЛИ и первым входам элементов И первой группы, выходы которых соединены с первым входом второго блока приоритета, выход которого подключен к третьим входам коммутаторов и пятым входам накопителей, шестые входы которых соединены с выходами элементов

ИЛИ группы, выход элемента ИЛИ подключен к первому входу первого блока приоритета, второй, третий и четвертый входы которого соединены соответственно с третьим входом, четвертым и пятым выходами блока управления, четвертый вход и выходы с шестого по девятый которого подключены соответственно к выходу элемента ИЛИ и вторым входам элементов И групп, второго блока приоритета и элементов ИЛИ группы. (()65886

1 2

Изобретение относится к вычислительНоА технике и может быть использовано в

Ьперятивных запоминаннцих устройствах (ОЗУ), (iocTpoBIII!hix ия пОлупроводникОВЫХ }ин}}ми }еских з}1}}оми}}аюп(их узлах.

Известно динамическое запоминающее устройство, содержащее блок начальной установки, элементы памя ги, дешифратор, регистр строк, элементы И, ИЛИ, И-ИЛИ, шифратор, счетчик адреса, блок запуска счетчика, коммутатор адреса и блок коммутации запроса. Регенерация ячеек памяти В данном устройстве производится построчно В режиме записи-считывания !11.

Однако при страничной организации памяти объем оборудования указанного устройства увеличивается пропорционально количеству страниц памяти. Кроче того, при отсутствии обращения хотя бы по одному адресу накопителя запоминающего устройства необходимо провести одновременно регенеряци}о всего объема памяти, что приводит к резкому увели}ению потребляемой устройством мощности, Наиболее близким к предлагаемому является динамическое запоминающее устройство, содержащее блок управления, схему модификации адреса, схемь1 выборки адреса, регистры, cxet)lv сч}пывания, накопители и счетчик адресы регенерации.

При необходимости провести регенерацию устройство управления устанавли>зает триггеры регистра запросов в еди}шчное состояние, причем каждому триггеру соогве1 ствует определенный накопитель.

Адрес регенерации определяется по содержимому счетчика адреса регенерации.

Если внешнее устройство осуществляет обращение к одной части запоминающего устройства, то в другой части в этс> время прс>исходит регенерация. 1(осле осуществления регенерации регистр сбрасывается в начальное состояни(12 .

Недостатком известного устройства является также значительное увеличение потребляемой устройc TBOM мощHOcTH при регенерации.

Цель изобретения -- уменьшение мощности, потребляемо:, динамическим запоминающим устройс вом.

Поставленная цель достигается тем, tiTO

В диHÇMи Iе(кое запоминя}0}цее устройстBÎ, содержащее накопители, коммутаторы, p(гистр числа, регистр запросов, блок управления и регистр адреса, выходы котор<.го подключены соответственно к первым вхо дам накопителей, коммутаторов и б,и кы управления, первый и второй выходы которого соединены соотв(тственно с первым Входом регистра запросов и вторыми Входами ком мутя то (и) В, В ы х () I ы к() т(ц) ы х }10, I I< Jl !0 l(и ы

}(BT0PhlM е)хода M на ко пи 1 ел(>Й, TP(тьи B x< tды и Bbfx(ULhi которых с<>еди н(и и c00 I B(l

IO

2(!

tIÎ .1 с t( сс

ВЕННО С тР TÜH Ì Вhl XO.IOÌ бЛОКсl УП Р:I BËB ния и Вход 1 ми p(. Гистра числя, Выхо,1ы кОтОрых являк>тся информационными в}*}ходами устрс>йствя, информационными входами коТОРО ГО и B 1Я K)TCH Ч(.TB(. PTh}C ВХОДЫ Н3 Ко. пителей, введс ны элемент ИЛИ, первая и вторая группы элемеHToB И, группа элементов ИЛИ, первый и второй блоки приоритета, выходы которых подключены со<>тветственно к второму входу блока управления и первым входам элементов И второй группы, Выходы которых соединены с первыми входами элементов ИЛИ группы и вторым входом регистра запросов, выход которого подключен к входа м элемента

ИЛИ и первым входам элеме}}тов И первой

ГРУ ППЫ, ВЫХОДЫ KOTOPBIX СОЕДИ}!(.НЫ С ПЕPвым входом второго блока приоритета, выход которого подкл}оче>1 к третьим входам коммутаторов и пятым входам накопителей, шестые входы которых соединены с выходами элемснтов ИЛИ группы, выход элемента ИЛИ подключен к первому входу первого блока приоритета, второи, третий и четвертый входы которого соединены сOOTBCTcòВСННО С ТРЕТЬИМ ВХОДОМ, ЧЕТ}1(РТЫМ И ПЯтым выходами блока управления, четвертый

Вход и выходы с шестого ilt) девятый которого подключены соответственно к выходу элемента ИЛИ и вторым входам элементов И групп, второго блока }p»0pHTBT3 и элсл-ентов ИЛИ группы.

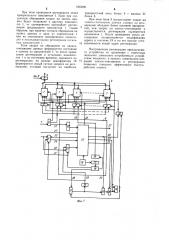

На фи}.. приведена cTptt кту рн-.я схемы динамического запоминающего уcTpOHcTB;1; фиг. 2 — — cTpvKTyp! I3 H схем;1 B;i pHB II (3 блока синхронизации, вхо.}ящегс> в блок управления.

Устройство (фиг. 1) содержит накопители 1, одни Н3 входов кс)горых являютсН информационными входами 2 у(тройствы, р(.Гистр 3 чис.13, ВыхОды которОГО HB.1яют(я инфо(2мацио}lными выход3MH 4 <стрс>и(твя, коммутаторы 5, регистр 6 адрсся с Входами <, блок 8 управления, первь>й 9 и второй (! блоки пр}(оритета, регистр ! запросов. элемент ИЛИ 12, первую 13

ИЛИ. Блок 8 управления (фпг. 1) содержит генератор 16 импульсов, счетчик 17 импульсов, первый дешифратор 18, ce(. I }пк !9 адреса регенерации, блок 20 cHIIхронизации, дополнительный элемент И.}(И 21 и второй дешифратор 22. Блок 8 имеет в-.oды 23- 27 соответственно с первого по пятый и выходы 28--37 соответственно с IiepB<>IO !10 десятый.

Блок 29 синхронизации фиг. 2) содержит распределитель 38 импульсов, третий дешифратор 39, триггеры 40 и 41. элементы

И 42 и 43 и элементы И- Н f . 44 и 45.

Рассмотрим два режимы рябо гы ) C! pOHствя: режим записи-считывания д;: ппьых при

<огсутстBHH регенерации и режим зып}н urHHòûB3íHÿ при наличии реп il< р;>цип.

1065886

В первом режиме работы код адреса ячейки, к которой необходимо обратиться в режиме записи, выставляется на входах 7, а данные — на входах 2.

На входе 27 выставляется код операции (запись-считывание), а на вход 25 блока 8 управления подается сигнал запроса от внешнего устройства на обращение к устройству.

Сигнал запроса поступает на один из входов элемента ИЛИ 21, на выходе которого формируется сигнал единичного уровня, поступающий на вход блока 20.

При наличии всех единиц на входах элемента И вЂ” НЕ 44 на его выходе формируется сигнал нулевого уровня, поступающий на информационный D-вход распределителя 38. Под первый же тактовый импульс, поступающий на его тактовый С-вход, состояние D-входа распределителя переписывается на его первый выход, т.е. на его первом выходе формируется сигнал нулевого уровня. Однако благодаря наличию обрат- 20 ной связи между выходами распределителя 38 и входами элемента И вЂ” HE 44 на выходе элемента И вЂ” НЕ 44 формируется сигнал единичного уровня.

Под следующий тактовый импульс, воздействующий на С-вход распределителя 38, состояние его первого выхода перезаписывается на его второй выход, а на первом выходе состояние сигнала соответствует единичному уровню. Таким образом, под воздействием тактовых импульсов, формируемых генератором 16, на выходах распределителя 38 формируются сигналы унитарного позиционного кода, один из которых принимает нулевое значение, т.е. распределитель 38 формирует тактовую сетку частот.

Под воздействием первого тактового им- 35 пульса, поступающего с выхода 32 блока 8 на один из входов первого блока 9 приоритета, осуществляется запуск последнего.

На выходе блока 9 формируется сигнал запроса, поступающий на вход 24 блока 8. 4О

Старшая часть кода адреса поступает с выхода регистра 6 адреса на вход дешифратора 22, который производит выбор соответствующего накопителя I и на одном из своих выходов формирует сигнал разрешения единичного уровня, поступающий на 45 вход блока 20.

Часть разрядов кода адреса, например младшая часть, поступает с выхода регистра 6 адреса через коммутатор 5 на один из входов накопителей 1, остальная часть разрядов кода адреса поступает на другие входы накопителей I. По сигналу обращения, поступающему на входы соответствующего накопителя с выхода одного из элементов ИЛИ 15, осуществляется запись данных в один из выбранных накопителей 1, адрес которого указан в старших разрядах кода адреса.

Считывание данных из устройства происходит аналогично.

Считанные данные с выхода соответствующего накопителя записываются вз регистр 3 по сигналу, формируемому блоком 8 управления на его выходе 37.

Декодирование кола операции (записьсчитывание слова, запись-считывание байта) осу1цествляется с помощью дешифратора 39. Сигнал с его выхода поступает на первый вход элемента И-HF. 45, на второй вход которого поступает один из тактовых импульсов распределителя 38.

Во втором режиме работы по формированию на выходе счетчика 17 кода начала регенерации на выходе 28 блока 8 формируется сигнал, устанавливающий регистр 1! в единичное состояние, что соответствует наличию запроса на регенерацию соответствующего накопителя 1.

Через элемент ИЛИ 12 сигнал запроса на регенерацию поступает на вход блока 9 и на один из вколов элемента ИЛИ 21.

При отсутствии запроса на запись-считывание данных на вхоле 25 блоков 8 блок 20 запускается через элемент ИЛИ 21 сигналом запроса на регенерацию.

Блок 20 разрешает работу блока 10.

Так как каждой странице памяти отведен определенный приоритет, то лля определения страницы с высшим приоритетом сигналы запросов на регенерацию через элементы И 13 поступа1от на вход блока !О, на выходе которого выделяется запрос на регенерацию наиболее приоритетного накопителя 1.

Данный сигнал подключает выход счетчика 19 через соответствующий коммутатор 5 к наиболее приоритетному накопителю 1. После этого на выходе 35 блока 8 формируется сигнал обращения к наиболее приоритетному накопителю 1, который «ерез соответствующие элементы И 14 и

ИЛИ 15 поступает на вход соответствующего накопителя 1. Этим же сигналом обращения с выхода элемента И 14 триггер регистра l запросов сбрасывается в нулевое состояние.

Так как регенерация прошла не во всех накопителях 1, то на выходе элемента

ИЛИ 12 присутствует запрос на регенерацию и поэтому блок 20 осуществляет второй цикл по регенерации следующего по приоритету накопителя I. Таким образом, регенерация накопителей 1 в порядке возрастания приоритетов продолжается до тех пор, пока все триггеры регистра !1 запросов не установятся в нулевое состояние.

При наличии сигнала запроса от внешнего устройства на входе 25 блока 8, например, на запись данных и сигнала регенерации на выходе элемента ИЛИ !2 устройство работает аналогично вышеуказанному.

1065886

При этом проводится регенерация менее приоритетного накопителя l. Если при следующем обращении запрос на запись данных будет направлен к другому накопителю 1, То одновременно произойдет регенерация предыдущего накопителя 1. Таким образом, при наличии сигнала обращения на запись данных в один из накопителей 1 или их считывание одновременно происходит и последовательная регенерация остальных накопителей 1.

Если запрос на обращение на записьсчитывание данных формируется постоянно к одному из накопителей 1, то после проведения регенерации в остальных накопителях 1 и по истечении времени, заданного на регенерацию, на выходе дешифратора 18 формируется новый сигнал запроса на регенерацию, который поступает на наиболее приоритетный вход блока 9 с выхода 31 блока 8.

При этом блок 9 осуществляет запрет на запись-считывание данных (запрос íà регенерацию обладает более высоким приоритетом, чем запрос на запись-считывание) и осуществляется регенерация оставшегося накопителя 1. После проведения цикла регенерации осуществляется модификация адреса в счетчике 19 и на его выходе уста10 навливается новый адрес регенерации.

Постраничная регенерация предлагаемого устройства по сравнению с известным позволяет уменьшить потребляемую устройством мощность, а процесс совмещения one15 раций записи-считывания и регенерации позволяет повысить эффективное быстродействие памяти.

106588б

Составитель В. Рудаков

Редактор М. Рачкулинец Техред И. Верес Корректор И. Муска

Заказ 10709 51 Тираж 5О Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП <Патент», г. Ужгород, ул. Проектная, 4