Устройство для вычисления функций

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ, содержащее регистр старших разрядов первого аргумента,регистр младших разрядов первого аргумента, блок памяти, первый блок умножейия , первый и второй коммутаторы, буферный регистр, сумматор и регистр результата, причем выход регистра старших разрядов первого аргумента соединен с первыгл входом блока памяти , первый выход которого соединен с первым информационным входом первого коммутатора, выход которого соединен с первым входом сумматора, выход которого соединен с входом регистра результата и информационным входом буферного регистра, выход :которого соединен с первым информационным входом второго коммутатора, выход регистра младших разрядов первого аргумента соединен с первым входом первого блока умножения, о тличающееся тем, что, с целью расширения класса решаемых задач за счет возможности вычисления функций от аргументов, в него введены блок синхронизации, регистр старших разрядов второго аргумента, регистр младших разрядов второго аргумента и второй блок умножения, первый и второй входы которого соединены соответственно с выходом регистра младших разрядов второго аргумента и вторым выходом блока i памяти, третий .выход которого соединен со вторым входом первого блока умножения, выход которого соединен со вторым информационным входом первого коммутатора, управляющий вход которого соединен с первр.лм выходом блока синхронизации, второй и третий выходы которого соединены соответственно с входом записи буферного регистра и управляющим входом второго коммутатора, второй информационный вход и выход которого соединены соответственно с выходом второго блока умножения и втоСП рым входом сумматора, выход pe иcтра старших разрядов второго аргумента соединен со вторым входом блока памяти.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) 3(51) 0 06 Р 15 31

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬП ИЙ (21) 3495525/18-24 (22) 27 ° 09 ° 82 (46) 15.01.84. Бюл. Р 2 (72) А.Н.Флоренсов (71) Омский политехнический институт (53) 681.325 (088.8) (56) 1. Заявка Великобритании

Р 1413045, кл. & 06 15/20, опублик. 1975.

2. Потапов В.И.р Нестерук В.Ф. и Флоренсов A.Н. Быстродействующие арифметико-логические устройства цифровых вычислительных машин.

Новосибирск. 1978, с, 36 (прототип) . (54) (57) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ

ФУНКЦИЙ, содержащее регистр старших разрядов первого аргумента, регистр младших разрядов первого аргумента, блок памяти, первый блок умножения, первый и второй коммутаторы, буферный регистр, сумматор и регистр результата, причем выход регистра старших разрядов первого аргумента соединен с первым входом блока памяти, первый выход которого соединен с первым информационным входом первого коммутатора, выход которого соединен с первым входом сумматора, выход которого соединен с входом регистра результата и информационным. входом буферного регистра, выход которого соединен с первым информационным входом второго коммутатора, выход регистра младших разрядов первого аргумента соединен с первым входом первого блока умножения, о тл и ч а ю щ е е с я тем, что, с целью расширения класса решаемых задач за счет воэможности вычисления функций от аргументов, в него введены блок синхронизации, регистр старших разрядов второго аргумента, регистр младших разрядов второго аргумента и второй блок умножения, первый и второй входы которого соединены соответственно с выходом регистра младших разрядов второго аргумента и вторым выходом блока

Я памяти, третий выход которого соединен со вторым входом первого блока умножения, выход которого соединен со вторым информационным входом первого коммутатора, управляющий вход которого соединен с первым выходом блока синхронизации, второй Я и третий выходы которого соединены соответственно с входом записи буферного регистра и управляющим входом второго коммутатора, второй информационный вход и выход которого соединены соответственно с выходом второго блока умножения и вторым входом сумматора, выход регистра старших разрядов второго аргу мента соединен со вторым входом блока памяти.

1067510

Изобретение относится к нычислй- тельной технике и может быть использовано для ускоренного вычисления произвольной. функции двух ар" гументон, н частности для вычисления функции необходимой при выполнении преобразования декартовых координат в полярные координаты.

Известно вычислительное устройство, предназначенное для вычисления функций двух аргументов и со- 30 держащее регистр старших разрядов первого аргумента, регистр младших разрядов первого аргумента, регистр старших разрядов второго аргумента, регистр младших разрядов второго аргумента, блок памяти, сумматор, выход которого соединен со входами буферного регистра и регистра результата, н блок синхронизации (1) .

Педостатком такого устройства 20 янл лют с я относитель но невысокие точность и быстродействие.

Паиболее близким к предлагаемому по технической сущности является устройство для вычисления Функций, содержащее регистр старших разрядов ар гумента, регистр младших разрядов аргумента, три блока памяти, блок умно>кения, два коммутатора, сумматор, буферный регистр и регистр результата, причем выход регистра старших разрядов первого аргумента соединен с первым входом блока памяти, первый выход которого соедиIQEi с первым информационным входом псрного коммутатора, выход которого соединен с входом регистра резуль" тата и информационным входом буфер- .. ного регистра, ныход которого соединен с первым информационным входом второго коммутатора, выход ре 40 гистра младших разрядов первого аргумента соединен с первым входом первого блока умно>кения 2g °

Целью изобретения является расширение класса решаемых задач за счет 45 возможности дополнительного нычисления функции от одного и двух аргументов.

Поставленная цель достигается тем, что н устройство для вычисления 5О функций, содержащее регистр старших раэрядон первого аргумента, регистр младших разрядов первого аргумента, блок памяти, первый блок умножения, первый и второй коммутаторы, буферный регистр, сумматор и регистр результата, причем выход регистра Старших разрядов первого аргумента соединен с первым входом блока памяти, первый выход которого соединен с первым информационным входом первого коммутатора, выход которого сое"; динен с первым входом сумматора, выход которого соединен с входом регистра результата и информационным входом буферного регистра, ны- 65 ход которого соединен с первым информационным входом второго коммутатора, выход регистра младших разрядов первого аргумента соединен с первым входом первого блока умножения, дополнительно введены блок синхронизации, регистр старших разрядов второго аргумента, регистр млад ших разрядов второго аргумента и второй блок умножения, первый и второй входы которого соединены соответственно с выходом регистра младших разрядов второго аргумента и вторым выходом блока памяти, третий выход которого соединен со вторым входом первого блока умножения, выход которого соединен со вторым информационным входом первого коммутатора, управляющий вход которого соединен с первым ныходом блока синхронизации, второй и третий выходы которого соединены соответственно со входами записи буфер ного регистра и управляющим входом второго коммутатора, второй информационный вход и выход которого соединены соответственно с выходом второго блока умножения и вторым входом сумматора, выход регистра старших разрядов второго аргумента соединен со вторым входом блока памяти.

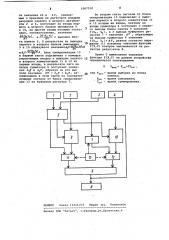

На чертеже изображена блок-схема предлагаемого устройства.

Устройство содержит регистр 1 старших разрядов первого аргумента, регистр 2 младших разрядов первого аргумента, регистр 3 старших разрядов второго аргумента, регистр 4 младших разрядов второго аргумента, блок памяти 5, сумматор б, буферный регистр 7, регистр результата 8, блоки умножения 9, 10, коммутаторы 11 и 12, блок синхронизации 13.

Вычисление значения функции

f(Х, Y) в устройстве производится на основе соотношения

f (X,VJ =Е(4,Vol+ — Зх — ЬХ вЂ” по= — ЙУ, И (1 Оу ) дХ (xo, y ) (1) где Х и У определяются старшими. разрядами, соответственно, аргументов Х и Y а е>Х и 6У определяются младшими разрядами аргументов

Хи У.

Устройство работает в дна такта; определяемых блоком синхронизации 13„

На входы блока памяти 5 с регистра 1 старших разрядов первого аргумента поступает значение Х, а срегистра 3 старших разрядов второго аргумента, поступает значение Уд ..

Блок памяти 5 хранит три таблицы значений, соответственно f(X, Y);

Ж .V ) . М(т,т.1 .. 8 первом тав3x aY

1067510

Т,„„+ Т,„+2тсм, время выборки иэ блока памяти, время умножения, время суммирования. где Tsb(c, ВНИИПИ Заказ 11211/53 Тираж 703 Подписное

Филиал ППЛ "Патент", г.ужгород,ул. Проектная,4 те значения: ЬХ и A Y, снимаемые с хранящих их регистров младших разрядов первого и второго аргументов 2 и 4, поступают на входы первого и второго блоков умножения 9 и 10, на другие входы которых поступают, соответственно, значения — - и М/Х У, ) Bf (Хо Yo) дх BY с выходов блока памяти 5. В результате на выходах первого и второго блоков умножения

9 и 10 образуются значениями сЛХЙа )ДМ

1 дх х(хо, М и А Г= . Блок синхронизации 13 в первом такте подключает с помощью управляющих входов к выходам первого )5 и второго коммутаторов 11 и 12 их первые входы, в результате чего,на входы сумматора 6 поступают значения h F и daF образуя на его выходе зйачение hF = AqF + b2F, запоминаемое в этом такте по соответствующему сигналу от блока синхронизации 13 на буферном регистре -7.

Во втором такте сигналы от блока синхронизации 13 подключают к выходам первого и второго коммутатора 11 и 12 вторые их входы, поэтому на входы сумматора 6 поступают с первого выхода блока памяти 5 значение

f (X» У©), а с выхода буферного регистра 7 - значение h образующее на выходе сумматора 6 значение

f (Х, Yo ) + AFy равное согласно вира кению (1) искомому значению функции

f(X,Y) которое запоминается на регистре результата 8. !

Время Т вычисления значения функции f(X,Y). на данном устройстве определяется соотношением