Многоуровневая ячейка памяти

Иллюстрации

Показать всеРеферат

МНОГОУРОВНЕВАЯ ЯЧЕЙКА ПАМЯТИ , содержащая элементы связи/ входной элемент, выходые элементы,опорный и блокировочные элементы, выполненные на р-п-р-транзисторах, и триггеры , первые выходы которых подключены к коллектору р-п-р-транзистора соответствующих элементов связи, эмиттеры которых подключены к соответствующим коллекторам опорного элемента , база р-п-р-транзистора блокировочного элемента является управляющим входом ячейки памяти и подключена к соответствующему коллектору р-п-р-транзистора опорного элемента, коллекторы р-п-р-транзисторов выходных элементов являются выходом ячейки памяти, эмиттеры р-п-рттранэисторов выходных элементов подключены к первому входу соответствующего триггера , эмиттер р-п-р-транзистора блокировочного элемента и база р-п-ртранзистора опорного элемента подключены к общей шине, причем эмиттер р-п-р-транзистора входного элемента является информационным входом ячейки , памяти, отл. ичающаяся тем, что, с целью повышения надежности ячейки за счет снижения требований к амплитуде и фронтам тактовы в импульсов, в неё введены допол нительные элементы связи, выполненные на р-п-р-т.ранзисторах, коллекторы которых подключены к вторым вы- § ходам соответствующих триггеров, (Л базы - к общей шине, а эмиттеры к соответствующим коллекторам p-h-p .транзисторов опорного и блокировочного элементов, вторые входы триггеров подключены к соответствующим коллекторам р-Н-р-транзистора блокировочного элемента, третий выход каждого триггера подключен к первому входу последукицего триггера, о эмиттер р-п-р-транзистора входного элемента подключен к тактовой шине. сд со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (И),, 3(5D G ll С 19 28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 2928621/18-24 (22) 22. 05.80 (46) 15.01.84. Бюл. )р 2 (.72) Л..К.Самойлов и Ю.И,Роговов (71) Таганрогский радиотехнический институт им. В.Д.Калмыкова (53) 681.327.6 (088.8) (56) 1. Авторское свидетельство СССР

)р 615541, кл. G 11 С 11/40, 1976.

2. Авторское свидетельство СССР

9 705523, кл . (Х ll С 1 1/40, 1977 (прототип) . (54)(57) МНОГОУРОВНЕВАЯ ЯЧЕЙКА ПАМЯ-.

ТИ, содержащая элементы связи, входной элемент, выходые элементы, опорный и блокировочные элементы, выполненные íà p -n-p-транзисторах, и триггеры, первые выходы которых подключены к коллектору р-п-р-транзистора соответствующих элементов связи, эмиттеры которых подключены к соответствующим коллекторам опорного элемента, база р-п-р-транзистора блокировочного элемента является управляю-. щим входом ячейки памяти и подключена к соответствующему коллектору

p-n-p-транзистора опорного элемента, коллекторы р-п-р-транзисторов выходных элементов являются выходом ячейки памяти, эмиттеры р-и -р транзистаров выходных элементов подключены к первому входу соответствующего триггера, эмиттер р- n-р-транзистора блокировочного элемента и база р-и-ртранзистора опорного элемента подключены к общей шине, причем эмиттер р-и-р-транзистора входного элемента является информационным входом ячейки памяти, отличающаяся тем, что, с целью повышения надежности ячейки эа счет снижения требований к амплитуде и фронтам тактовы импульсов, в нее введены дополнительные элементы связи, выполненные на р-п-р-транзисторах, коллекторы которых подключены к вторым вы- Е

Ф ходам соответствующих триггеров, базы - к общей шине, а эмиттерык соответствующим коллекторам р-и-ргрананогорон опорного н бпоннронон". ного элементов, вторые входы триггеров подключены к соответствующим Я коллекторам р-и-р-транзистора блокнровочного элемента, третий выход каждого триггера подключен к первому входу последующего триггера, эмиттер р-и-р-транзистора входного элемента подключен к тактовой шине.

1067534

Изобретение относится к .импульс-" ной технике и может быть использовано, например, для построения многоуровневых структур.

Известна схема инжекционного запоминающего элемента, содержащая 5 триггер, выполненный на транзисто- . рах с непосредственными связями, транзисторы записи и считывания, а также источники тока, выходы которых подключены к соответствующим ба- 10 зам транзисторов (11.

Основным недостатком данного устройства являются низкие возможности, обусловленные запоминанием лишь двухуровневого сигнала, 15

Наиболее близкой к изобретению является многоуровневая ячейка памяти, содержащая элементы связи, входной элемент, выходные и опорные элементы, выполненные íà р-и — р-транзисторах, блокировочный элемент и триг20 геры, выполненные на и-р-и-транзисторах, причем первые выходы, триггеров подключены к соответствующим коллекторам элементов связи, эмиттеры которых подключены к коллекторам соответствующих опорных элементов, база блокироночного транзистора янляется управляющим входом ячейки памяти и подключена к соот нет ст нующему входу опорного транзистора (2 ).

Недостатком этого устройства является его низкая надежность, которая обусловлена наличием н схеме двух шин питания. Использование различных шин питания для записи и хранения может принести к неоднозначности входного и ныходного тока.

Цель изобретения — повышение надежности устройства за счет снижения требования к амплитуде и фронтам так-40 тового импульса.

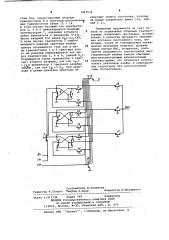

Поставленная цель достигается тем, что н устройство, содержащее элементы связи, входной элеглент, выходные элементы, опорные и блокировочные 45 элементы, выполненные на р-П р-транзисторах, и триггеры, первые выходы которых подключены к коллектору р- и-р-транзистОра соответствующих элементов связи, эмиттеры которых подключены к соответствующим коллекторам опорного элемента, база р-и-р-транзистора блокировочного элемента является управляющим входом ячейки памяти и подключена к соответствующему коллектору р-и-р-транзисто-55 ра опорного элемента, коллекторы р-tl p — транзисторон выходных элементов являются выходом ячейки памяти, эмиттеры р- n-p-тран зи сторон выходных элементов подклюиены к первому входу 60 соответствующего триггера, эмиттер р-и — р-транзистора блокировочного элемента и база р-и-р-транзистора опорного элемента подключены к общей LIIH не, причем эмиттер р-и-p-транзистора Q5 входного элемента является информационным входом ячейки памяти, введены дополнительные элементы св язи, выполненные на р-п-р-транзисторах, коллекторы которых подключены к вторым выходам соответствующих триггеров, базы - к общей шине, а эмиттеры — к соответстнующим коллекторам р- и-р-транзисторов .опорного и блокировочного элементов, вторые входы триггеров подключены к соответствующим коллекторам. р -п- р-транзистора блокировочного элемента, третий выход каждого триггера подключен к первому входу пбследующего триггера, эмиттер р-и-р-транзистора входного элемента подключен к так1 оной шине, На чертеже приведена принципиальная электрическая схема четырехуровневой ячейки памяти, Устройство содержит соответственно первые и вторые и-р-и-транзисторы триггеров 1, — б, входной р-и-р-транзистор 7, опорный транзистор 8, р-п- р-транзисторы связи 9 — 11, до"" полнительные р-и-р-транзисторы связи 12 — 14, выходные р-n-p-транзисто- ры 15 — 17, блокировочный р-п-р-транзистор 18.

Многоуровневая ячейка памяти работает в режиме записи и в режиме хранения.

В режиме хранения на тактовую шину (ТИ) подается сигнал низкого логического уровня, что приводит к заЙиранию нходного 7 и блокировочного 18 транзисторов; Базовые токи транзисторов триггера подаются через транзисторы снязи 9 — 14, причем значения токов идентичны, поэтому состояние триггеров не изменяются.

В зависимости от состояния триггеров через выходные транзисторы 15 — 17 инжектируется или не инжектируется значение входного тока. Если для определенности считать, что транзистор 1 первого триггера открыт, второго 3 — закрыт, а третьего 5 открыт, то выходной ток устройства равен значению 2 Зо, в противном случае, т.е. первые транзисторы первого и третьего триггеров закрыты, а второго — открыт, выходной ток равен величине 3 1 . В базы транзисторов триггера самого младшего разряда подаются через транзистор 9 (10,11) и дополнительный транзист. тор 12 (13,14) токи, равные 1 3О, в базы транзисторов триггера второго разряда — 2 3О, третьего - 3 Л „, и-го — и J g Задание требуемого значения тока можно измерить путем изменения rеэметрии базовых р-областей инжектора и переинжектора.

В режиме записи на тактовую шину подается второй догический уронень.

В этом случае транзистор 18 открывается и отбирает через свои коллек1067534

Составитель. В.Теленков

Редактор A.Ãóëüêî Техред О.Неце Корректор К).Макаренко т

Заказ 11217/%4 Тираж 581 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г.ужгород, ул .Проектная, 4 торы ток, инжектируемый опорным транзистором 8 в эмиттеры дополнительных транзисторов связи 12 — 14, В этом случае базовый ток транзисторов 2, 4 и 6 инжектируется входным транзистором 7, значение которого .может изменяться в диапазоне 0-4;, Пусть входной ток равен J g= 2J +аЗ., В этом случае транзистор 2 самого . младшего разряда триггера ячейки памяти открывается (так как в.ба- 10 эы транзисторов 3 и 5 триггера этого же разряда инжектируется ток чере з т ран зисторы 2, 4 и 6, рав ный 0 в ) .

:Открывается также транзистор 4 триггер второго разряда,.так как 1э„). 5

> 2,à транзистор 6 третьего разряда закрыт, так как 8K<-3 Хo При прреходе в режим хранения .триггеры не изменяют своего состояния, поэтому на входе устройство имеет ток, равный 2 le.

Повышение надежности эа счет отказа от управления опорными транзис торами, позволяет, во-первых, использовать в качестве питаюшего напряжения источник постоянного тока, вовторых, отказ от тактирования потенциалом позволяет понизить уровень помех внутри БИС, в-третьих, появляется возможность тактирования многоуровневой ячейки памяти обычными многоколлекторными инжекционными транзисторами, что позволяет испольэовать укаэанную ячейку в инжекционных структурах беэ использования схем согласования.