Устройство для измерения частоты синусоидального сигнала

Иллюстрации

Показать всеРеферат

(19) (11):

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ .

РЕСПУБЛИН

ЗСЮ 01

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCNOIA(ЕВЕДатВЪСтвм

° с

Ма

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЭОБРЕТЕНИЙ И ОТКРЫТИЙ бМ 920552

21) 3498232/18-21 (22) 01. 10. 82 (46) 23.06..84. Вюл. В 3 (722 В.В.Карпов и В.В.Машкин (53) 621.307(088.8) (561 1, Авторское свидетельство СССР и 920552, кл. Я 01 к 23/00., 25.01.80

В (54 ) (57 t УС 1РОЯСТВО Д)1Я ИЭИЕРЕНИ11

4ACT0%3 СИНУСОИДАЛЬНОГО СИ1 НИ% по авт.св. 9 920552, о т л и ч а ю щ е- ,.е с я тему что, с целью повышения точности иэмерения частот, в него вВедены последовательно соединенные элемент эадержки, первый блок сравнения, второй пороговый блок, элемент Й и ключ, последовательно соединенные второй блок сравнения и третий пороговый блок, выход которого подключен к второму входу элемента И, прн этом выход элемента задерики соединен с первым входом второго блока сравнения, второй вход последнего подключен к,второму входу первого блока сравнения, к второму входу ключа, к выходу блока выделения ре зультата и к входу элемента эадеряки, а третий вход элемента И соединен с выходом первого порогового блока.

1068833

О„(ц=яшсов(с- )

Изобретение относится к радиоизмерительной технике и может использоваться для измерения неизвестных на приемной стороне параметров сигналов цифровых данных, модулированных различными частотами. 5

По основному авт.св. М 920552 известно устройство для измерения частоты синусоидального сигнала, содержащее последовательно соединенные форглирователь второй производной,ig блок деления, блок извлечения квадратного корня, блок выдачи результата, а также последовательно соединенные формирователь модуЛя и пороговый блок, причем сигнальный выход формирователя второй производной подключен к входу формирователя модуля, выход которого. соединен с вторым входоМ блока делителя, выход порогового блока подключен к второму входу блока выдачи результата Г1 1.

Недостатком устройства является наличие ложных, оценок частот и сигналов цифровых данных в моменты смены его частот или при воздействии помех, что приводит к снижению оценок частот сигналов цифровых данных.

Цель изобретения — повышение точности измерения частот сигналов цифровых данных.

Поставленная цель достигается 30 тем, что в устройство для измерения частоты синусоидального сигнала введены последовательно соединенные элемент задержки, первый блок сравнения, второй пороговый блок, элемент И и 35 ключ, последовательно соединенные второй блок сравнения и третий пороговый блок, выход которого подключен к второглу входу элемента И, при этом выход элемента задержки соединен с первым входом второго блока сравнения, второй вход последнего подключен к второму входу первого блока » сравнения, к второму входу ключа, к выходу блока выделения результата 45 и к входу элемента задержки, а третий вход элемента И соединен с выходом первого порогового блока.

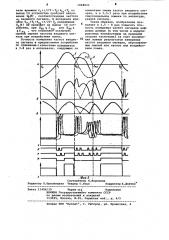

На фиг. 1 приведена структурная схема устройства; на фиг. 2 — диаграммы напряжений, поясняющие работу устройства.

Устройство содержит формирователь 1 второй производной, состоящий из соединенных последовательно первого и второго формирователей

1-1 и 1-2 первой производной, а также первого элемента 1-3 задержки, вход . которого подключен к входу первого формирователя 1-1 первой производной, соединенному с входом формиро- 60 вателя 1 второй производной. Выходы второго формирователя 1-2 производной и первого элемента 1-3 задержки подключены соответственно к первому и второму выходам формирователя. 1 65

2 второй производной, первый выход ко торого соединен с первым входом бло ка 2 деления. Выход блока 2 деления подключен к входу блока 3 извлечения квадратного корня, выход которого соединен с первым входом блока 4 выдачи результата.

Второй выход формирователя.1 второй производной подключен к входу формирователя 5 модуля, выход которого соединен с вторым входом блока

2 деления и с входом первого порогового блока 6, выход которого подключен к второму входу блокр 4 выдачи результата.

Выход блока выдачи результата подключен к первому входу ключа 7, входу второго элемента 8 задержки, а также к первым входам первого и второго блоков 9 и 10 сравнения, вторые входы которых соединены соответственно с первым и вторым выходами второго элемента 8 задержки.

Выходы первого и второго блоков 9 и 10 сравнения подключены соответственно к входам второго и третьего пороговых блоков 11 и 12, выходы которых соединены с первым и вторым входами элемента И 13. Выход первого порогового блока 6 подключен к третьему входу элемента 13, выход которого соединен с вторым входом ключа 7, выход которого соединен с выходом 14 устройства.

Устройство работает следующим образом.

Формирователь 1 второй производной осуществляет формирование на своем первом выходе напряжения, равного второй производной входного сигнала, а на второй выходе - напряжения входного сигнала, согласо° ванного по времени с его второй производной путем задержки с помощью первого элемента 1-3 задержки входного сигнала на время ., где Гвремя дифференцирования.

При входном сигнале Я =АЭ пий где A u hr — - соответственно амплитуда и круговая частота сигнала, на выходах первого и второго формирователей 1-1 и 1-2, а также элемента

1-3 задержки формируются в момент времени напряжения

02(Ю Дж Ы(! (г (41=ASinCV (t- Jг, а на выходе формирователя 5 модуля присутствует напряжение О (tJ фЯв1яиф- Я которое определяет коэффициент деления блока 2 деления, на выходе,которого формируется напряжение Уу(tI=

02Й1 2

U> (Ц= — = ш,эяак которого определя 4®

1068833 ется напряжением U2(t). 3а выходе, блока 3 извлечения квадратного корня, осуществляющего формирование на своем выходе напряжения, равного квадратному корню от значения входного сйгнала стаыавливается. напряжение

6((5(1 Р по знаку с напряжением 02 (tl . Напряжение . 0<(tl проходит на выход блока 4 выдачи результата только при наличии на его втором входе положитель- ) ного потенциала, формируемого пороговым блоком 6 при V4(tl ) E>, где

Е - порог срабатывания первого по1 рогового блока 6.

При 04<Е„ на выходе первого порогового блока 6 формируется нулевой потенциал, нри этом напряжение U6(tl не проходит на выход блока 4 выдачи результата. Этим достигается исключение ошибок измерения частот входного сигнала, обусловленных неопределенностью напряжения 0 (t при

02 0 и 04Ф О, при этом Е> выбирается, исходя из требований к точности и динамическому, диапазону блока 2 деления. Выходное напряжение Ug блока

4 выдачи результата поступает на первый вход ключа 7.

Второй элемент 8 задержки формирует на своих первом и втором выходах напряжения 001 и 002, равные 30

00, (М =Ц,((- <1) и 002(t) = " (4-, ).

Первый и второй блоки 9 и 10 сравнения формируют на своих. выходах на00, (Ц = иО (t) -00« - )

0 p4(tl= 00 (И 00 (т — 72), представляю-35 щие собой приращение напряжения О () за интервалы времени с1 и .

Второй и третий пороговые блоки

11 и 12 идентичны и представляют собой двухпороговые устройства с пора- 4О гами +Е„2и -Е„З,выбираеьими симметричклми относительно нулевого уровня.

При -Е, (О„(Ez на выходе второго порогового блока 12 формируется. положительный потенциал, а при

Uo2(tl C =Е или 002(tl En

Аналогично формируются потенциалы на выходе третьего порогового блока 12. При наличии хотя бы одного нуeBoI o IIoTeHIIH83IB HB BxoQах элемен- 50 та И 13 на его выходах формируется нулевой потенциал, при наличии кото.— рого на втором входе ключа 7 напряжение 00(tl с выхода блока 4 выдачи результата не проходит на выходе 14 устройства. .- 55

Дополнительная задержка напряжения

0p(tl на время 72, формирование напряжения 004(tl и его сравнение с пороговыми значениями обеспечивает исключение возможных ложных оценок частоты40 многочастотного сигнала (при этом напряжение Up(tl является переменным) при up(Ч =up(t — с1) °

Предполагается, что в интервале времени С0 ", t1 На входе, устройства 65 присутствует сигнал A2$in и 11, а в интервале t14 t2 — сигнал А & nur. t, причем A1=Л2, ж1 (ы2 (Ъиг;2а).

Текущие значения напряжения U>(t) и 04(4) (фиг.20 и 2в) соответствуют моментам времени (t — 1 входного сигнала. С момента врЕмени 1 и до момента времени t1 ++ T напряжение

U2{tf второй производной не соответствует сигналам ..A15in со 1и A2Sinm t при этом напряжение 00 (t) (фиг.2г l

2 2 также не соответствует частотам Ю и М2 сигналов.

В интервале времени 10 —, 11 напряжение 00 постоянно И равно 01 (фиг.2I)

В этом случае 001=002= 003=0 =О

01 02 03 04 на выходах второго и третьего пороговых блоков 11 и 12 (фиг. 2д и 2е ), а следовательно, и на выходе эле.лента

13 фиг.2ж j формируется положительный потенциал, при этом напряжение

0p(tl, соответствующее частоте входного сигнала, через открытый ключ 7 проходит йа выход 14 устройства (фиг.2з ).

В интервале времени от t1 до

11+3/2, (за счет несоответствия напряжения 02(tl сигналам сначала

А1 Sin ut t, a затем A2sInm2t напря жение lip является перемейной вели-, чиной. В этом случае 00 (4) Ф 00 (Ф! и U02 (tl f 00 (tl и при Upy(tl p =Е или 00>(t ) Е на выходе второго порогового блуа 11, а при 00<(t)(- е о или Up< (t) ) Е „на выходе тРетьего

:порогового блока 12 формируется нулевой потенциал. При наличии хотя бы одного нулевого гэтечциала на входах элемента 13 на его выходе формируется нулевой потенциал, при этом электронный ключ закрыт и напряжение

0a(tl н соответствующее частотам б01 или WZ входного сигнала, не проходит на выход 14 устройства.

В интервале времени от t1 +3/? с до t2 напряжение 00 постоянно, соответствует частоте 02 входного сигйала.и через открытый ключ 7 проходит на выход 14 устройства.

При выборе lq ь в емя задержки определяет быстродействие процесса включения блокировки появления на выходе 14 устройства ложных оценок, а время задержки ig определяет время выключения упо лянутой блокировки.

С учетом задержек,1 и 72 включения и выключения упомянутой бло<кировки ключ 7 закрыт в интервале

Времени оТ t1 + I,1 до 11+3/2 + 62

Значения Е> второго и третьего пороговых блоквй 11 и 12 выбираются, исходя из допустимых искажений сигнала и требований к точности оценки его частот.

При воздействии помех, например синусоидальной (фнг.2а — 2и, пунктир) в интервале времени t 1 в интер t п2

1068833

3 . Фиг.2

Составитель Л.Воронина

Редактор О.Юрковецкая Техред О.Неце Корректор А. Дзятко

Ф

Заказ 11456/39 Тираж 715 Подписное

ВНИИНИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г„ Ужгород, ул. Проектная, 4 вале времени (1+3/2t +t> п +7„на

2 и1 1 выход 14 устроиства проходит напряжение Цр(Й, соответствующее частоте

w. входною о сигнала. В интервале времени t +W„ t„ +3/2" г напряжение

Up(t,t йе проходит на вйход 14 устройства, при Upy Е „ или Opg у Е и, что позволяет исключить ошибЬ оценки частоты входного сигнала при воздействии помех.

Точность измерения частот входного сигнала в предлагаемом устройстве по сравнению с известным повыаается в 3-8 раэ в интервалах, следующих эа моментами смены частот входного сигнала, н в 1,5-3 раза при воздействии сйнусоидальной помехи по амплитуде, равной сигналу.

Таким образом, изобретение позволяет в 1,5 - 8 раз повысить точность измеренчя частот сигналов цифровых данных (в том числе и модулированных неизвестными на приемной стороне частотами) за счет исключения ложных результатов измерения частот входного сигнала, обусловленных сменой его частот или воздействием помех.