Устройство диспетчеризации вычислительной системы

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДИСПЕТЧЕРИЗАЦИИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ, содержащее регистр приращений, коммутатор, регистр управления, девлифратор, первую и вторую группы блоков эле ментов И, группу элементов ИЛИ, блок элементов И, группу регистров, вход каждого из которых является первым информационным входом устройства,. первый вход каходого блока элементов И первой группы является кодовым входом устройства, выходы блоков элементов И первой группы являются выходами обращения устройства, выходы блоков элементов И второй группы являются адресными выходами устройства, первый вход каждого блока элементов .И второй группы является соответствую11,им адресным входом устройства, сигнальный вход устройства соединен с первым входом блока элементов И, выход которого соединен с первым вход ом регистр а управления , второй информационный вход устройства соединен с входом регистра приращений, вход прерывания устройства соединен с управляющим входом коммутатора, информационный вход которого соединен с выходом регистра приращений, выход коммутатора соединен с вторыл входом регистра управления, выходы которого соединены с входами де чифратора , каждый, выход которого соединен -с первым входом соответствующего элемента ИЛИ группы, выход которого соединен с вторыми входа- j ми одноименных блоков элементов И (Л первой и второй групп, отличающееся тем, что, с -целью сокращения оборудования, в него введен узел поиска минимального кода, входы которого соединены с выходами регистров группы, первый выход узла поиска минимального кода соединен с вторыми входами элементов ИЛИ группы, второй выход узла поиска минимального кода явСХ ) ляется выходом прерывания устройства и соединен с вторым входом бло:о ка элементов И. Л

СОЮЗ СО8ЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (111

44 А

3(59 G 06 F 15/00

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

> (21) 3433144/18-24 (22) 30. 04. 82 (46) 23.01.84, Бюл. Р 3 (72) В.A. Титов, В..Л. Гайдуков, С.М.Кильчик и В.П.Неверов (53) -681. 325 (088. 8) (56) 1. Авторское свидетельство СССР

Р 533928, кл. G 06 Ч 15/16, 1975.

2. Авторское свидетельство СССР

Р 951316, кл. 6 06 15/00, 1982. (54 ) (57) УСТРОЙСТВО ДИСПЕТЧЕРИЗАЦИИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕИЫ, содержащее регистр приращений, коммутатор, регистр управления, деиифратор, первую и вторую группы блоков элементов И, группу элементов. ИЛИ, блок элементов И, группу регистров, вход каждого из которых является первым информационным входом устройства,. первый вход каждого блока элементов И первой группы является кодовым входом устройства, выходы блоков элементов И первой группы являются выходами обращения устройства, выходы блоков элементов И второй группы являются адресными выходами устройства, первый вход каждого блока элементов .Р. второй группы является соответствующим адресным входом устройства, сигнальный вход устройства соединен с первым входом блока элементов И, выход которого соединен с первым входом регистра управ ления, второй информационный вход устройства соединен с входом регистра приращений, вход прерывания устройства соединен с управляющим входом коммутатора, информационный вход которого соединен с выходом регистра приращений, выход ком(утатора соединен с вторым входом регистра управления, выходы которого соединены с входами дещифратора, каждый . выход которого соединен .с первым входом соответствую.щего элемента ИЛИ группы, выход которого соединен с вторыми входами одноименных блоков элементов P первой и второй групп, о т л и— ч а ю щ е е с я тем, что, с целью сокращения оборудования, в него введен узел поиска минимального кода, входы которого соединены с выходами регистров группы, первый выход узла поиска минимального кода соединен с вторыми входами элементов ИЛИ группы, второй выход узла поиска минимального кода является выходом прерывания устройства и соединен с вторым входом блока элементов R.

1068944

Изобретение относится к вычисли тельной технике и может быть исполь зовано для построения устройств сопряжения в многомашинных вычислительных системах.

Известно устройство диспетчеризации вычислительной системы, содержащее группы элементов И, дешифратор, регистр управления, коммутатор и регистр приращений ill.

Иедостатком этого устройства яв- 10 ляется невозможность обмена по инициативе управляемой ЭВМ.

Иаиболее близким к изобретению по технической сущности и достигаемому результату является устройство для диспетчеризации вычислительной системы, содержащее регистр приращений, коммутатор, регистр управления, первый дешифратор, первый элемент ИЛИ, группу элементов ИЛИ, группу узлов формирования сигналов состояния, содержащих триггер, регистр состояния, регистр приоритета, схему сравнения, и группу элементов И причем вход регистра приращений соединен с входом кода настройки устройства, выход регистра приращений соединен с информационным входом коммутатора, управлякщий вход которого соединен .со строби- З0 рукщим входом устройства, выход коммутатора соединен с информационным входом регистра управления, управляющий вход которого соединен с управлякщим входом устройства, выход 35 регистра управления соединен с входом первого дешифратора, выход ко-.орого является первым выходом устройства, входы регистров состояния соединены с первой группой кодовых 40 входов устройства, единичные входы триггеров являются установочными входами устройства, нулевые входы триггеров соединены с выходами соответствукщих схем сравнения, вхо- 45 ды регистров приоритета являются второй группой кодовых входов устройства, выходы регистров приоритета соединены с первыми входами схем сравнения и первыми входами элементов И групп, вторые и управляющие входы которых соединены соответственно с выходами регистров состояния и выходами схем сравнения, а выходы — с в ходами элементов ИЛИ группы, выходы которых подключены к группе управляющих выходов устройства, выходы триггеров соединены с управлякщими входами схем сравнения, входы первого элемента ИЛИ соединены с выходами триггеров, устрой-60 ство содержит также управляющий триггер, генератор импульсов, элемент И, счетчик импульсов, второй дешифратор и второй элемент ИЛИ, причем выход первого элемента ИЛИ соединен с единичным входом управляющего триггера, нулевой вход которого соединен с выходом второго элемента ИЛИ, выход управлякщего триггера соединен с управляющим входом элемента И, информационный вход которого соединен с выходом генератора импульсов, а выход - с входом счетчика, выход которого соединен с входом второго дешифратора, и с вторыми входами схем сравнения, выходы которых соединены с входами второго элемента ИЛИ, выход второго дешифратора является вторьм выходом устройства, управляющий вход второго дешифратора соединен с командным входом устройства 523.

Иедостатком этого устройства является большой объем оборудования.

Цель изобретения — сокращение оборудования.

Поставленная цель достигается тем, что в устройство диспетчеризации вычислительной системы, содержащее регистр приращений, коммутатор, регистр управления, дешифратор, первую и вторую группы блоков элементов И, группу элементов ИЛИ, блок элементов И, группу регистров, вход каждого из которых является первым информационным входом устройства, первый вход каждого блока элементов И первой группы является кодовым входом устройства, ьыходы блоков элементов И первой группы являются выходами обращения устройства, выходы блоков элементов И второй группы являются адресными выходами устройства, первый вход каждого блока элементов И второй группы является соответствующим адресным входом устройства, сигнальный вход устройства соединен с первым входом блока элементов И, выход которого соединен с первьм входом регистра управления, второй информационный вход устройства соединен с входом регистра приращений, вход прерывания устройства соединен с управлякщим входом коммутатора, информационный вход которого соединен с выходом регистра приращений, выход коммутатора соединен с вторьм входом регистра управления, выходы которого соединены с входами дешифратора, каждый выход которого соединен с первьм входом соответствующего элемента ИЛИ группы, выход которого соединен с вторыми входами одноименных блоков элементов И первой и второй групп, введен узел поиска минимального кода, входы которого соединены с выходами регистров группы, первый выход узла поиска минимального кода соединен с вторымй входами элементов

ИЛИ группы, второй выход узла поис1068944 ка минимального кода является выходом прерывания устройства и соединен с вторьм входом блока элементов И.

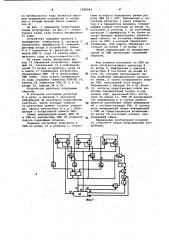

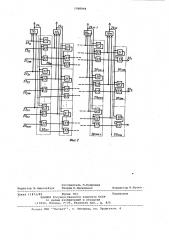

На фиг. 1 приведена структурная схема устройства; на фиг.2 — структурная схема узла поиска минимального кода.

Устройство содержит регистр 1 приращений, коммутатор 2, регистр 3 управления, дешифратор 4, информа;ционныр входы 5 устройства, блоки

".6 и 7 элементов И, регистры 8, элементы ИЛИ 9, узел 10 поиска минимального кода и блок элементов И 11.

На схеме такие обозначены выход 12 обращения устройства, адресный 13, сигнальный 14 и информационный 15 входы устройства, вход 16 и выход 17 прерывания устройства, управлякщая ЭВМ 18 и управляемые

ЭВМ (УВМ). Узел поиска минимального кода содержит элементы ИЛИ-HE 19, группы 20 элементов ИЛИ 21 и И 22, входы 23, выходы -24 и 25.

Устройство работает следующим образом.

В исходном состоянии регистры

8 в нуле, в регистр 1 заносится информация на несколько характерных участков, число которых зависит от различных причин (чтенне операнда, запись результата и т.д.) обращенный у.оперативной памяти УВМ;

Обмен информацией между ЭВ11 18 и УВМ по инициативе ЭВМ 18 осуществляется следукщим образом.

Команда настройки заносится в

УВМ по входу 15 в регистр 1,:состояние которого определяет режим ра- боты ЭВМ 18 с УВ?1. Информация о состоянии регистра 1 через коммутатор 2 в промежутки времени, определяющие подачу сигналов по входу 14, поступает в регистр 3. По состоянию регистра 3 дешифратор 4 на одном из своих выходов вырабатывает управлякщий сигнал; по которому определяется та УВМ, к которой происходит

10 обращение. Код адреса обращения поступает на блоки 7 по входу 13.

Обмен информацией по инициативе одной из УВМ происходит следующим образом.

Код запроса поступает от УВМ на вход соответствукщего регистра 8 по входу 5. Информация с выходов регистров 8 поступает на входы .23

20 узла 1 О, который обеспечивает выбор наиболее приоритетного запроса на обмен, а также позиционного номера УВМ, приславшей этот запрос.

Информация с выходов 24 и 25 блока

25 10, которая представляет собой наиболее приоритетный запрос и код номера уВМ, приславшей его, поступает на выход 17. ЭВМ 18 анализирует эту информацию и в случае необходимости производит обмен информацией с соответствукшей УВМ. В случае, если немедленный обмен информацИей с УВМ не представляется возможным,. по входу 16 поступает -сигнал, пре35 к Ращающий

Применение изобретения позволяет сократить объем. оборудования устройства.

1068944

Фиг: 2

С ос тав итель Н. Кудряшев

Техред Л. Пилипенко

Редактор И.Николайчук т.илиал ППП Патент., г. Ужгород, ул. Проектная ° 4

Эаказ 31473/45 Тираж 703

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1) 3035, москва, ) .-35,. Раушская наб., д. 4/5

Корректор И.Иуска, Подписное