Дешифратор адреса

Иллюстрации

Показать всеРеферат

ДЕШИФРАТОР АДРЕСА, содержащий ключевые МОП-транзисторы, истокн . которых объединены, затворы являются адресными входами первой группы дешифратора, усилительный МОП-транзистор, сток которого является входом питания дешифратора, а исток - выходом дешифратора, о т ли ч а ю щ и и с я тем, что, с целью повышения быстродействия, стоки ключевых МОП-транзисторов являются адресными входами второй группы дешифратора , а затвор усилительного МОП-транзистора соединен с истоками ключевых МОП-транзисторов..

СОЮЗ COBETCHHX

СОЦИАЛИСТИЧЕСКИХ

РЕСГ)УБУ)ИН (1% (И) щр G 11 С 8/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ 4»М »»»-»»» «»»»».

I (.ОПИСАНИЕ ИЗОБРЕТЕНИЯ с:. у

3 :.:=, . "ЛУ а .

В =-" ъ ;», ° »

И» с»

0aaL

К АВТОРСКОМЪ СВИДЕТЕЛЬСТВУ (21) 3444869/18-24 (22) 25.05.82 (46) 23.01.84. Бюп. В 3 (72) Б. С-Кугаро (71) Государственное союзное конструкторско-технологическое бюро по проектированию специализированных микросхем (53) 621.327.6 (088.8) (56) 1. Патент США 9 4099162, кл. 340-173, опублик. 1979.

2. Патент CttJA Р 4048629,. кл. 340-173, опублик. 1977 (прототип ). (54)(57l ДЕШИФРАТОР АДРЕСА, содержащий ключевые МОП-транзисторы, истоки.которых объединены, затворы являются адресными входами первой группы дешифратора, усилительный

МОП-транзистор, сток которого является входом питания дешифратора, а исток — выходом дешифратора, о т л и ч. а ю шийся тем, что, с целью повышения быстродействия, стоки ключевых МОП-транзистороэ являются адресными входами второй группы дешифратора, а затвор усилительного

МОП-транзистора соединен с истоками ключевых МОП-транзисторов,.

1068999

Изобретение относится к микро электронике и может быть испольэова но в микросхемах памяти на МДП элементах.

В интегральных схемах памяти на .

МДП-транзисторах в качестве дешифраторов адреса наибольшее распространение получили элементы НЕ-ИЛИ, в которых используется принцип предзаряда, а для активации выбранной шины прйменяются динамические повторители(Использование предзаряженных узлов позволяет исключить сквозное потребление в схеме дешифратора адреса и уменьшить время йереключения венти.лей НЕ-ИЛИ, а применение динамических повторителей повышает скорость заряда выбранной выходной .шины дешифратора (1 ).

Однако разряд затвора транзисто" ра динамического повторителя невыб- 20 .раиного вентиля дешифратора происходит через проходной транзистор, разУ еляющий затвор транзистора динами ческого повторителя и шину, объединяющую стоки адресных транзисторов g5 вентиля НЕ-ИЛИ, и через открытые адресные транзисторы (в худшем случае через один открытый адресный транзистор,:т.е. процесс разряда относительно большой емкости затво-, ра транзистора динамического повторителя эамедлен, .так как в póäøåì случае разряд,емкости проходит. через два трайзистора. Кроме того, для. надежного отделения емкости затвора транзистора .динамического повторителя от емкости шины, объединяющей стоки/адресных транзисторов, затворы проходных транзисторов смещаются источником опорного напряжения или же тактируются специально формируемым 4О импульсом, что усложняет схему де. шифратора и уменьшает скорость ее работы.

Наиболее близким к изобретению по 45 технической сущности и схемному решению является дешифратор адреса, в котором управление затвором проходного транзистора осуществляется при помощи источника опорного напряжения, благодаря чему уменьшается опасность паразитного роста потенциала в невыбранном вентиле дешифратора при условии неполного разряда емкости затвора динамического повторителя и одновременном включении импульса, управляющего включением дешифратора 3 2).

Дешифратор адреса обладает перечисленными выше недостатками, причем в нем шины адресных сигналов предва- 60 рительно разряжены. Заряд адресных шин при активации адресных буферов является относительно длительным процессом, что дополнительно снижает быстродействие известного дешифратора.,65

Целью изобретения является повышение быстродействия.

Поставленная цель достигается тем, что в дешифраторе адреса, содержащем ключевые МОП-транзисторы, истоки которых объединены, затворы являются адресными входами первой группы дешифратора, усилительный МОП-транзи- . стор, сток которого является входом питания дешифратора, а исток — выходом дешифратора, затвор усилительного

МОП-транзистора соединен с истоками ключевых МОП-транзисторов, стоки ключевых МОП-транзисторов являются адресными входами второй группы дешифратора.

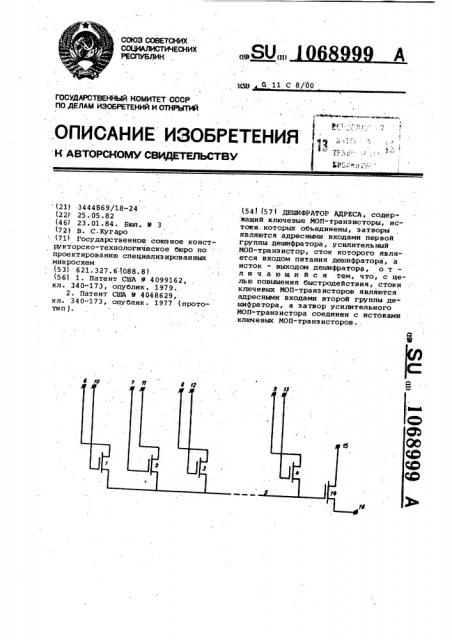

На чертеже представлена принципиальная схема дешифратора на восемь выходов.

Дешифрат ор адреса содержит ключе- вые МОП-транзисторы 1-4, истоки которых объединены шиной 5, шины 6-9 прямых адресных сигналов, шины 1013 инверсных адресных сигналов, усилительный МОП-транзистор 14, затвор которого соединен с шиной 5, сток соединен с шиной 15 питания, а исток

16 является выходом дешифратора.

Дешифратор работает следующим образом.

В течение периода. восстановления, т.е. когда нет.обращения к схеме памяти, все шины 6-13 адресных сигналов заряжены до потенциала логической единицы и через транзисторы 1-4 заряжена шина 5, объединяющая истоки транзисторов и затвор транзистора 14.

В течение периода восстановления на шине 15 тактового питания поддержи- вается уровень логического нуля, так что шина 16 выхода дешифратора адреса разряжена через открытый транзистор

14 . При обращении к схеме питания на адресных шинах фррмируются сигналы, соответствующие принятой адресной информации. В тех вентилях дешифратора, где сток хотя бы одного .транзи-стора, например транзистора 2, подключен к адресной шине, на которой установлен потенциал логического ну-. ля, шина, объединяющая истоки транзисторов, разряжается через этот транзистор (его затвор при этом подключен к шине адресного сигнала инверсного сигналу, тактирующему сток адресного транзистора, т.е. к шине,. на которой поддерживается потенциал логической единицы ). В выбранном вен" тиле дешифратора, то есть в таком вентиле, где все затворы транзисторов подключены к адресным шинам, имеющим потенциал логического нуля, на шине, объединяющей истоки транзисторов, сохраняется потенциал логической единицы. При появлении импульса тактового питания начинается заряд шины выхода дешифратора адреса, и

1068999

Составитель Г. Бородин

Редактор А. Шишкина Техред И.Асталош Корректор O° . Тигор

Тираж 579 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб ., д. 4/5

Заказ 11480/48

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 на шине 5 выбранного вентиля дешифратора растет потенциал благодаря емкостной передаче напряжения через затвор транзистора 14; В невыбранных вентилях дешифратора рост .потенциала на шинах, объединяющих истоки транзисторов 1-4, невозможен из-за того, что открыт хотя бы один иэ этих транзисторов невыбранного вентиля дешифратора. При этом передающая емкость транзистора 14 невыбранного вентиля дешифратора уменьшается до величины емкости перекрытия затвор — сток

-транзистора 14, так:как потенциал на затворе транзистора 14 ниже порогового напряжения транзистора. 15

После завершения периода обращения к схеме питания, т.е ° при переводе схемы памяти н невыбранное состояние, происходит восстановление начального состояния схемы дешифратора адреса. Все потенциалы на шинах прямых и инверсныс адресных сигналов принимают значение логической единицы. При этом заряжаются все шины, объединяющие истоки транзисторов 1- 25

:4, разряженные при обращении к схеме памяти. Одновременно с этим шина 15 тактового питания разряжается до уровня логического нуля, и ранее выбранная выходная шина дешифратора адреса разряжается через открытый транзистор 14.

Высокая скорость работы схемы дешифратора адреса достигается за счет использования предэаряда как шин, объединяющих истоки транзисторон 1-4, так и шин прямых и инверс-.. ных адресных сигналов, управляющих .работой дешифратора адреса. В предлагаемой схеме разряд невыбранных вен тилей дешифратора проходит, в худшем 40 случае, через один из транзисторов 14, тогда как в известных схемах:дешифраторов адреса разряд затвора транзистора 14 проходит через два транзистора — проходной и адресный, соединенных последовательно. Уменьшение количества транзисторов в цепи разряда приводит к более быстрому раэразряду невыбранных вентилей дешифратора, что позволяет Раньше включать импульс тактового питания. Схема предлагаемого дешифратора проще известных схем так как не содержит ни пред- з аряженных транзисторов, ни проходных транзисторов отделяющих затвор а транзистора 14 от вентиля дешифратора. Уменьшение количества транзисторов в схеме приводит к увеличению ее надежности.

Уменьшение коэффициента передачи напряжения для транзистора 14 выбранного вентиля дешифратора,. связанное с тем, что в предложенной схеме увеличена параэитная емкость .затвора транзистора 14, компенсируется тем, что н современных интегральных схемах памяти, изготавливаемых по и-канальной технологии, величина порогового напряжения МДП-транзистора составляет величину порядка 0„8 В и менее, что увеличивает эффективность работы МДП-транзистора, как передающей емкости.

В схемах памяти большой емкости дешифратор строки помещают в, середине матрицы запоминающих элементов, разрывая при этом строки матрицы пополам, что позволяет уменьшить задержку распространения сигнала в поликремниевой строке. Такое размещение дешифратора вызывает необходи- мость испольэовать два усилительных (транзистора в каждом вентиле дешиф-- ратора, один иэ котор |х управляет леной, а второй — правой половинами строк матрицы. Это обстоятельство позволяет для выбранного вентиля дешифратора дополнительно .Увеличить коэффициент передачи напряжения для шины, объединяющей истоки адресных транзисторов, или же позволяет уменьшить размеры транзисторов динамического повторителя.

Таким образом, предложенная схема дешифратора адреса обладает повышенным быстродействием за счет использования предзаряда шин прямых и инверсных адресных сиГналов и эа счет уменьшения количества транзисторон в цепи разряда в невыбранных вентилях дешифратора. Схема обладает боль шей надежностью эа:счет уменьшения количества транзисторов в вентиле.

Для схемы не требуется формировать специального тактоного импульса или источника опорного потенциала, управляющего проходными транзисторами.

Упрощение управления работой дешифратора адреса дополнительно увеличивает скорость ее работы и надежность схемы.