Корреляционный измеритель скорости

Иллюстрации

Показать всеРеферат

КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ СКОРОСТИ, содержащий два приемника, выходы которых соединены с входами соответствующих усилителей-ограничителей , выход первого из которых подключен к информационнок входу первого регистра, выход которого соединен с информационным входом второго регистра и первым входом решающего логического устройства, второй вход которого подключен к выходу второго регистра сдвига, третий - к выходу второго усилителя-ограничителя, а выходы - к суммирующему и вычитающему входам реверсивного счетчика, информационные выходы которого соединены с информационными входами управляемого делителя частоты, тактовый вход которого подключен к выходу генератора тактовых импульсов, а выход - If входу устройства отсчета и к тактовым входам регистров сдвига, отличающийся тем что, с целью обеспечения его работо-.. способности при больших ускорениях, в него введены два формирователя, первая схема совпадения, первый триггер и делитель частоты с постоянным коэффициентом деления, а решающее логическое устройство включает в себя второй и третий трип еры и вторую и третью схемы совпадения, причем выход первого регистра сдвига соединен с первыми входами второго и третьего триггеров, вторые входы которых подключены к выходу второго регистра сдвига, выход второго триггера соединен с первым входом первой схемы совпадения и с вторым входе мторой схемы совпадения, первый вход которой подключен к первому входу треть- s ей схемы совпадения, а через делиО ) тель частоты с постоянным козффициентом деления к выходу управляемого делителя частоты, вход второй схемы совпадения соединен с выходом второго усилителя-ограничителя и с третьим входом третьей схемы совпадег ния, а выход - с суммирующим входом реверсивного счетчика, вычитаннций вход которого подключен к выходу ;третьей схемы совпадения, второй вход которой соединен с выходом третьего триггер, а четвертый вход с выходом первого триггера, первый 4: X) вход которого подключен к вЕссоду первой схемы совпадения, а второй вход - к второму входу первой схемы СО совпадения, а через формирователь к выходу второго усилителя-ограничите .ля, при этом выход второго формирователя соединен с установочным входом реверсивного счетчика.

(19) SU (и) СОКИ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

3(51) G 01 Р 3/64

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 3462115/18-10 (22) 24.05.82 (46) 30.01.84, Бюл. Р 4 (72) Б.Г. Абрамович, B . .В. Завьялов и A.A.Ïàí÷åíêo (71) Дальневосточное высшее инженерное морское училище им. адм. Г.И.Невельского (53) 621.317.39:531 7(088 ° 8) (56) 1. Авторское свидетельство СССР

Р 466453, кл. G 01 P 3/64, 1975 °

2. Патент ФРГ Р 2345106, кл. G 01 Р 3/64; 1975 (прототип) . (54)(57) КОРРБЛЯЦИОННЫИ ИЗИБРИТЯЛЬ

СКОРОСТИ, содержащий два приемника, выходы которых соединены с входами соответствующих усилителей-ограничителей, выход первого из которых подключен к информационному входу первого регистра, выход которого соединен с информационным входом второго регистра и первым входом решающего логического устройства, второй вход которого подключен к выходу второго регистра сдвига, третий - к выходу второго усилителя-ограничителя, а выходы - к суммирующему и вычитающему входам реверсивного счетчика, информационные выходы которого сое-. динены с информационными входами управляемого ° делителя частоты, тактовый вход которого подключен к вы-. ходу генератора тактовых импульсов, а выход - к входу устройства отсчета и к тактовым входам регистров сдвига, отличающийся тем что, с целью обеспечения его работо-. способности при больших ускорениях, в него введены два формирователя, первая схема совпадения, первый триггер и делитель частоты с постоянным коэфФициентом деления, а решающее логическое устройство включает в себя второй и третий триг еры и вторую и третью схемы совпадения, причем выход первого регистра сдвига соединен с первыми входами второго и третьего триггеров, вторые входы которых подключены к выходу второго регистра сдвига, выход второго триггера соединен с первым входом первой схеьйя совпадения и с вторым входом второй схемы совпадения,. первый вход которой подключен к первому входу треть- Щ ей схемы совпадения, а через делитель частоты с постоянным коэффициентом деления к выходу управляемого делителя частоты, третий вход второй С схемы совпадения соединен с выходом второго усилителя-ограничителя и с ф третьим входом третьей схем совпаде.— ния, а выход — с суммирующим входом реверсивного счетчика, вычитающий вход которого подключен к выходу третьей схемы совпадения, второй вход которой соединен с выходом третьего триггера, а четвертый вход— с выходом первого триггера, первый вход которого подключен к выходу первой схемы совпадения, а второй вход — к второму входу первой схема совпадения, а через формирователь к выходу второго усилителя-ограничите.ля, при этом выход второго формирователи соединен с установочным входом реверсивного счетчика.

1070482

15 ра и первым входом решающего логичес-20 кого устройства, второй вход которого подключен к выходу второго регист25

40

60 формационные выходы которого соединены с информационными входами управля-65

Изобретение относится к приборостроению и может бйюь использовано предприятиями, выпускающими и эксплуатирующими измерители скорости.

Известен корреляционный измеритель скорости, содержащий два усилителя-ограничителя, два регистра сдвига, схемы совпадения, генератор тактовых импульсов, счетчик импульсов и соответствующие связи (1).

Наиболее близким к предлагаемому по технической сущности является корреляционный измеритеий скорости, содержащий два приемника, выходы которых соединены с входами соответствующих усилителей-ограничителей, выход первого из которых подключен к информационному входу первого регистра, выход которого соединен с информационным вхсдом второго регистра сдвига, третий — к выходу второго усилителя-ограничителя, а выходы— к суммирующему и вычитающему входам реверсивного счетчика, информационные выходы которого соединены с информационными входами управляембго; делителя частоты, тактовый вход которого подключен к выходу генератора тактовых импульсов, а выход — к входу устройства отсчета и к тактовым входам регистров сдвига f2).

Недостатком известного измерителя является нарушение его работоспособности. Это выражается в отсутствии или ошибочных показаниях скорости объекта и обусловлено большими начальными рассогласованиями между временем задержки входных сигналов измерителя скорости (транспортное, запаздывание) и временем задержки в регистрах сдвига, которые возникают при резком изменении скорости объекта, при произвольном во времени включении устройства и т.д.

Цель изобретения — обеспечение работоспособности измерителя прн больших ускорениях.

Указанная цель достигается тем, что в корреляционный измеритель скорости, содержащий два приемника, вы.ходы которых соединены с входами соответствующих усилителей-ограничителей, выход первого иэ которых подключей к .информационному входу первого регистра, выход которого соединен с информационным входом второго регистра и первым входом решающего логического устройства, второй вход . которого подключен к выходу второго регистра сдвига, третий — к выходу второго усилителя-ограничителя, а выходы — к суммирующему и вычитающему входам реверсивного счетчика, ин45

55 емого делителя частоты, тактовый вход которого подключен к выходу генератора тактовых импульсов, а выход — к входу устройства отсчета и к тактовым входам, регистров сдви- га, введены два формирователя, первая схема совпадения, первый ° триггер и делитель частоты с постоянным коэффициентом вселения, а решающее логическое устройство включает в себя второй и третий триггеры и вторую и третью схемы совпадения, причем выход первого регистра сдвига соединен с первыми:входами второго и третьего триггеров, вторые вхоцы которых подключены к выходу второго регистра сдвига, выход второго триггера соединен с первым входом первой схемы совпадения и с вторым входом второй схемы совпадения, первый вход которой подключен к первому входу третьей схемы совпадения, а через дели-тель частоты с постоянным коэффициентом деления к выходу управляемого делителя частоты, третий вход второй схемы совпадения соединен с выходом второго усилителя-ограничителя и с третьим входом третьей схемы совпадения, а выход — с суммирующим входом реверсивного счетчика, вычитающий вход которого подключен к выходу третьей схемы совпадения, второй вход которой соединен с выходом третьего триггера, а четвертый вход— с выходом первого триггера, первый вход которого подключен к выходу первой схемы совпадения, а второй вход к второму входу первой схемы совпадения, а через первый формирователь к выходу второго усилителя-ограничителя, при этом выход второго формирователя соединен с установочным входом реверсивного счетчика .

Такое построение. корреляционного измерителя позволяет обеспечить его работоспособность при больших начальных рассогласованиях между временем задержки входных сигналов измерителя и временем задержки в регистрах сдвига„которые возникают при резком изменении скорости или при произвольном во времени включении устройства, что приводит к отсутствию или ошибочным показаниям скорости объекта.

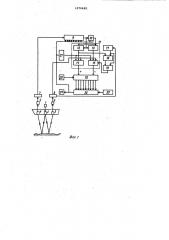

На фиг. 1 приведена принципиальная схема корреляционного измерителя скорости; на фиг. 2 — временные диаграммы его работы.

Измеритель содержит генератор 1, выход которого подключен к вибратору-иэлучителю 2, два вибратора-приемника 3 и 4, выходы которырс подключены к усилителям 5 и 6 с амплитудным детектированием, соединенным с усилителями-ограничителями 7 и 8, регистр.9 сдвига, подключенный к

1070482 усилителю-ограничителю 7 первого ка- нала, регистр 10 сдвига, подключенный к первому -регистру 9 сдвига, решающее логическое устройство 11, содержащее два триггера 12 и 13, подключенные к выходам первого

9 и второго 10 регистров сдвига, и две схемы 14 и 15 совпадения, подключенные к двум триггерам 12 и 13 и усилителю-ограничителю 8 второго канала, схему 16 совпадения, подклю- 10 ченную к выходам триггера 12 и формирователя 17, формирователь 17, подключенный к усилителю-ограничителю 8 второго канала, триггер 18, входы которого подключены к схеме 16 15 совпадения и формирователю 17, а выход — на вход схемы 15 совпадения, реверсивный счетчик 19, подключенный к выходам схем 14 и 15 совпадения,,и выходу формирователя 20, делитель

21 частоты с постоянным коэффициентом деления, вход которого подключен к управляемому делителю 22 частоты, а выход — к входам схем 14 и

15 совпадения, управляемый делитель

22 частоты, входы которого подключены к выходам реверсивного счетчика 19 и генератора 23 тактовых импульсов,. а также устройство 24 отсчета, подключенное к выходу управляемого делителя частоты. 30

Корреляционный измеритель работает следующим образом.

Электрический гармонический сигнал с генератора 1 подается на вибратор-излучатель 2, где он преобразу-35 ется в акустический сигнал, который излучается вертикально вниз и отражается от дна. Отраженный сигнал принимается двумя вибраторами-приемниками 3 и 4., где акустический сигнал 40 преобразуется в электрический и усиливается затем усилителями 5 и 6 с амплитудным детектированием. С . выходов этих усилителей сигналы поступают на усилители-ограничители

7 и 8. С выхода усилителя-ограничителя 7 сигнум-сигнал q»=siq»»)»» подается на вход регистра 9 сдвига, число разрядов которого больше. числа разрядов регистра 10 сдвига. С выхода усилителя-ограничителя 8 сигнум-сигнал =@»р Х1 подается на входы схем 14 и 15 совпадения и на вход формирователя 17. При включении питания измерителя скорости формирователь 20 записывает в каскады реверсивного счет-55

Г чика 19 двоичное число, соответствующее минимальной измеряемой скорости объекта, и на выходе управляемого делителя 22 частоты присут»твует минимальная частота следования тактовых импульсов, а в регистре 9 сдвига - максимальное время задержки. Передним фронтом сигнала с выхода регистра 9 сдвига запускается триггер 12, который возвращается в исходное состояние передним фронтом сигнала с выхода регистра 10 сдвига.

Выходной сигнал триггера 12 подается на первые входы схем 14 и 16 совпадения. Задним фронтом сигнала с выхода регистра 9 сдвига запускается триггер 13, который возвращается в исходное состояние задним фронтом сигнала с выхода регистра 10 сдвига.

Выходной сигнал триггера 13 подается на первый вход схемы 15 совпадения. На вторые входы схрм 14 и 15 совпадения подаются сигналы с выхода делителя 21 частоты с постоянным коэффициентом деления. На третьи входы схем 14 и 15 совпадения и на вход формирователя-17 подаются сигналы с усилителя-ограничителя 8.

Формирователь 17 формирует короткие сигналы из передних фронтов сигналов »9)»."у . Выходные сигналы формирователя 17 подаются на второй вход схемы 16 совпадения и на первый вход (вход синхронизации D-триггера) триггер 18. Выходные сигналы схемы 16 совпадения подаются на второй вход (информационный вход D-триггера) триггера 18. Выходные сигналы триггера 18 подаются на четвертый вход

cxemu -15 совпадения. Выходные сигналы схемы 14 совпадения подаются на вход сложения реверсивного счетчика. 19. Выходные сигналы схемы 15 совпадения подаются на вход вычитания реверсивного счетчика 19.

При больших начальных,рассогласо,ваниях сигналы формирователя 17 не ходе, следовательно, время задержки в регистре 9 сдвига уменьшается.

Как только рассогласование умень+ шится до такой величины, что сигналы с выхода формирователя 17 будут совпадать с сигналами с выхода триггера 12, на выходе схемы 16 совпаде- ния появляются сигналы (уровень логической 1 ) . В триггере 18 записываются сигналы с выходд схем 16. совпадения (уровень логической 1 ).

Выходным сигналом триггера 18 (уровень логической 1 ) отпирается схема 15 совпадения и на вход вычитания, реверсивного счетчика 19 начинают поступать сигналы и измеритель скорости начинает отслеживать скорость объекта.

Делитель 21 частоты с постоянным коэффициентом деления позволяет выбирать требуемые динамические свойства (скорость отработки рассогласования) и тбчность измерителя скорости таким образом, чтобы при небольших рассогласованиях формирователь 17, схема 16 совнадения и триггер 18 не показывали влияния на работу предлагаемого измерителя.

1070482, 1

1070482

НИИПИ 3 акаэ 11673/42 ираж 823 Подписное

4илиал ППП "Патент", г.Ужгород,ул.Проектная,4