Преобразователь код-мощность

Иллюстрации

Показать всеРеферат

ПРЕОБРАЗОВАТЕЛЬ КОД-МОЩНОСТЬ , содержащий источник пере7 манного напряжения, выход которого через управляемый вентиль соединен с нагрузкой и через делитель напряжения - с входом первого нульоргана и входом амплитудного детектора , двоичный вычитающий счетчик, установочныйвход которого подключен к ВЫХОДУ первого нуль-органа и первому управляющему входу управляемого вентиля, блок сравнения кодов, выход которого соединён с вторым управляющим входом управляемого вентиля, а выходы - с одноименными выходами двоичного вычитающего счетчика и выходами .регистра памяти, генератор импульсов, выход которого подключен к счетному входу двоичного вычитающего счетчика , интегратор, выход которого подключен к входу второго нуль-органа, и двоичный суммирующий счетчик, о.тличающийся тем, что, с целью повышения надежности, в него введены квадратор напряжения, два ключа, источник опорного напряжения , делитель частоты, матрица памяти, элемент И, два ftS-триггера и преобразователь код-интервал времени, выход которого подключен к S-входу первого триггера, Й-входу второго триггера и установочному входу двоичного суммирующего счетчика, счетный вход преоб э.азователя код-интервал времени под .ключен к первому входу элемента И и к второму выходу генератора импульсов , а синхронизирующий вход подключен к синхронизирующему входу регистра памяти, 3 -входу второго триггера и к выходу делителя частоты , вход которого соединен с выходом первого нуль-органа, причем выход амплитудного детектора через (Л соединенные последовательно квадратор Напряжения и первый ключ соединен с первым входом интегратора, второй вход которого через второй ключ соединен с выходом источника опорного Напряжения, при этом управляющий вход первого ключа соединен с выходом второго триггера, а управляющий вход второго ключа - с выходом первого триггера и с вторым входом элемента И, выход которого соединен со счетньм входом :л двоичного, суммирующего счетчика, : выходы которого соединены с адресными входами матрицы памяти, выходы которой подключены к одноименным входам регистра памяти, выход второго нуль-органа подключен к R-входу первого триггера.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) (И) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3498917/18-21 (2?) 28.09.82 (46) 30.01.84. Бюл. Р 4 (72) А.В.Заборня, В.H.Èâàíîâ, A.Ð.Ìoðoçoâ и Б.С.Мухин (53) 621.316.72(088.8) (56) 1. Патент СНА 9 1361452, кл. 323 †, 1972.

2. Авторское свидетельство СССР

N 7143811 . G 05 Г 1/66, 1978. (54)(57) ПРЕОБРАЗОВАТЕЛЬ КОЦ вЂ МОЩНОСТЬ, содержащий источник переменного напряжения, выход которого .через управляемый вентиль соединен с нагрузкой и через делитель напряжения — с входом первого. нульоргана и входом амплитудного детектора, двоичный вычитающий счетчик, установочный- вход которого подключен к выходу первого нуль-органа и первому управляющему входу управляемого вентиля, блок сравнения кодов, выход которого соединен с вторым управляющим входом управляемого вентиля, а выходы — с одноименными выходами двоичного вычитающего счетчика и выходами .регистра памяти, генератор импульсов, выход которого подключен к счетному входу двоичного вычитающего счетчика, интегратор, выход которого подключен к входу второго нуль-органа, и двоичный суммирующий счетчик, о .т л и ч а ю шийся тем, что, с целью повышения надежности, в него введены квадратор напряжения, два ключа, источник опорного на3(51) G 05 F 1/66/ Ч 03 К 13 02 пряжения, делитель частоты, матрица памяти, элемент И, два kS -триггера и преобразователь код-интервал времени, выход которого подключен к S -входу первого триггера, 1-входу второго триггера и установочному входу двоичного суммирующего счетчика, счетный вход преобразователя код-интервал времени подключен к первому входу элемента И и к второму выходу генератора импульсов, а синхронизирующий вход подключен к синхронизирующему входу регистра памяти, -входу второго триггера и к выходу делителя частоты, вход которого соединен с выходом первого нуль-органа, причем выход амплитудного детектора через соединенные последовательно квадратор напряжения и первый ключсоединен с первым входом интегратора, второй вход которого через второй ключ соединен с выходом источника опорного напряжения, при этом управляющий вход первого ключа соединен с выходом второго триггера, а управляющий вход второго ключа — с выходом первого триггера и с вторым входом элемента И, выход которого соединен со счетным входом двоичного суммирующего счетчика, выходы которого соединены с адресными входами матрицы памяти, выходы которой подключены к одноименным входам регистра памяти, выход второго нуль-органа подключен к

%-входу первого триггера.

1070530

Изобретение относится к импульсной технике и может быть использовано при построении цифровых систем управления технологическими процессами.

Известен преобразователь кодмощность, работа которого основана на периодическом сравнении управляющего напряжения с выходным напряжением генератора пилообраз ного напряжения и на отпирании управляемого вентиля, включенного последовательно с источником переменного напряжения и нагрузкой на время, в течение которого выходное напряжение генератора пилообразного напряжения превьпаает управляющее напряжение 11..

Недостатком данного устройства является невысокая стабильность выходного сигнала в зависимости от изменений амплитуды напряжения, питающего нагрузку.

Наиболее близким к предлагаемому является преобразователь код-мощ. ность, содержащий источник переменного напряжения, выход которого через управляемый вентиль соединен с нагрузкой и через делитель на- пряжения с входом первого нуль-органа и входом амплитудного детектора, двоичный вычитающий счетчик, установочный вход которого подключен к выходу первого нульоргана и первому управляющему входу управляемого вентиля, блок сравнения кодов, выход которого соединен с вторым управляющим входом . управляемого вентиля, а входы — с одноименными выходами двоичного вычитающего счетчика и выходами регистра памяти, генератор импульсов, выход которого подключен к счетному входу двоичного вычитающего счетчика, интегратор, выход которого подключен к входу второго нуль-органа, и двоичный суммирующий счетчик t2I..

Недостатком известного устройства является невысокая стабильность выходного сигнала при изменении амплитудного значения напряжения, питающего нагрузку, что снижает надежность его работы.

1О!

25

35

45

I

Цель изобретения — повышение

° надежности.

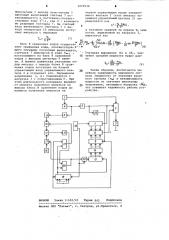

Поставленная цель достигается тем, что.в преобразователь кодмощность, содержащий источник переменного напряжения, выход которого через управляемый вентиль соеди-, нен с нагрузкой и через делитель 60 напряжения — с входом первого нульоргана и входом амплитудного детектора, двоичный вычитающий счетчик, установочный вход которого подключен-к выходу первого нуль-органа и первому управляющему входу управляемого вентиля, блок сравнения кодов, выход которого соединен с вторым управляющим входом управляемого вентиля, а входы — с одноименными выходами двоичного вычитающего счетчика и выходами регистра памяти, генератор импульсов, выход которого подключен к счетному входу двоичного вычитающего счетчика, интегратор, выход которого подключен к входу второго нульоргана, и двоичный суммирующий счетчик, введены квадратор напряжения, два ключа, источник опорного напряжения, делитель частоты, матрица памяти, элемент И, два З— триггера и преобразователь код-ин-тервал времени, выход которого подключен к S -aõoäó первого триггера, R-aõoäó второго триггера и установочному входу двоичного суммирующего счетчика, счетный вход преобразователя код-интервал времени подключен к первому входу элемента И и к второму выходу генератора импульсов, а синхронизирующий вход подключен к синхронизирующему входу регистра памяти, S -входу второго триггера и к выходу делителя частоты, вход которого соединен с выходом первого нуль-органа, причем выход амплитудного детектора через соединенные последовательно квадратор напряжения и первый ключ соединен с первым входом интегратора, второй вход которого через второй ключ соединен с выходом источника опорного напряжения, при этом управляющий вход первого ключа соединен с выходом второго триггера, а управляющий вход второго ключа — с выходом первого триггера и с вторым входом элемента И, выход которого соединен со счетным входом двоичного суммирующего счетчика, выходы которого соединены с адресными входами матрицы памяти, выходы которой подключены к одноименным входам регистра памяти, выход второго нуль-органа подключен к -входу первого триггера, На чертеже приведена функционарьг ная схема преобразователя код-мощность °

Преобразователь код-мощность содержит источник 1 переменного напряжения, соединенный с управляемым вентилем 2, выход которого подключен к нагрузке 3, делитель 4 напряжения, вход которого соединен с источником 1 переменного напряжения, а выход - с нуль-органом 5 и с амплитудным детектором 6, двоичный вычитающий счетчик 7, соединен- . ный с входами блока 8 сравнения кодов, другие входы которого подклю1070530 чены к выходам регистра 9 памяти, .генератор 10 импульсов, интегратор

;ll, выход которого подключен к входу нуль-органа 12, двоичный суммирующий счетчик 13, выходы которого соединены с входами матрицы 14 памяти, квадратор 15 напряжения, ключи 16 и 17, источник 18 опорного напряжения, преобразователь 19 код-интервал времени, выход которого соединен с соответствующими входами RS -триггеров 20 и 21, элемент И 22 и делитель 23 частоты.

Преобразователь работает следующим образом.

С выхода источника 1 переменного напряжения снимается напряжение

U» lt) = u sin T )

2з1. (1) 10

20 где U» и Т вЂ” значение ампдитуды и периода напряжения U»(t)..

Это напряжение поступает на вход управляемого вентиля 2 и через делитель 4 напряжения с коэй»))ициентом передачи К» на входы нуль-органа 5 и амплитудного детектора 6.

С выхода нуль-органа 5 снимается последовательность импульсов, появляющихся в моменты перехода напряжения »I» (<) через нуль. )la выходе. делителя 23 частоты через каждые К импульсов с выхода нуль-органа 5 появляется импульс, который запускает преобразователь 19 кодинтервал времени, записывает в регистр 9 памяти состояние выходов матрицы 14 памяти и перебрасывает

RS-триггер 21. Сигнал с выхода -триггера 21 открывает ключ 17, подключая тем самым напряжение

Ов с выхода источника 18 опорного напряжения к входу интегратора 11, второй вход интегратора 11 отключен от выХода квадратора 15 напряжения ключом 16. При этом выходное напряжение интегратора 11 начинает меняться от нуля до значения равНОГО UR

Uf = ()в -.г-,(2) 25

35

45

50 где U — напряжение на выходе источника 18 опорного напряжения;

U — нижнее допустимое значение амплитуды напряжения U» (t)„ постоянная интегрирования интегратора 11 ;

+ — время интегрирования.

Входной управляющий вход йвх по- 60 ступает на входы преобразователя 19 код-интервал времени. Через время

1» после прихода импульса запуска, поступающего с выхода делителя 23 частоты, на выходе преобразова-.еля 1965 код-интервал времени появляется импульс, который перебрасывает $триггеры 20 и 21, размыкая при этом ключ 17, обнуляя двоичный суммирующий счетчик 13 и замыкая ключ 16, подключая тем самым выход квадраI тора 16 напряжения к входу интегратора 11. . Время .) определится выражением где 1» — частота импульсов выхода генератора 10 импульсов.

При этом сигнал с выхода 1$— триггера 20 разрешит прохождение импульсов частотой » с выхода генератора 10 импульсов через элемент И 22 на счетный вход двоичного суммирующего счетчика 13, а также напряжение К„ О, с выхода амплитудного детектора 6 поступает на вход квадратора 15 напряжения. Напряжение К л- U> с его выхода подаетсЯ через ключ 16 на вход интегратора 11. Напряжение на выходе интегратора 11 изменится от значения 0 до нуля за время - равное

Оо » (4)

При достижении нуля напряжением на выходе интегратора 11 на выходе нуль-органа 12 появится импульс; который перебросит I1S, †òðèãã 20 в исходное положение, запретив темсамым прохождение импульсов частотой 1» чере — э;пемент И 22 на счетный вход двоичного суммирующего счетчика 13. При этом за веемя и в счетчике 13 накопится код H))„л равный (л(в)»л =-4 1 (5)

Учитывая выражения (2), (3), (4) и (5) очевидно, что:

0 (Чвх.л у с

Код Мвх.л поступает на адресные входы матрицы 14 памяти, устанавливая на ее выходах код ) a )I определяемый заранее решением трансцендентного уравнения

»»вх.х л ° 2Ъ»»вх.Z М в с. л (6)

gn y где n — количество двоичных разрядов кодов йцх, Кв „

Следующим импульсом с выхода делителя 23 частоты код йвх записывается в регистр 9 памяти, а вышеописанная часть функциональной схемы преобразователя начинает новый подобный цикл работы.

Далее преобразование кода в мощность происходит следующим образом

1070530

Таким образом, достигается линейная зависимость выходного сигнала (мощности) от значения входного сигнала (NQ и независимость мощности от значения амплитуды напряжения, питающего нагрузку ((4), что повышает надежность работы устройства.

ВНИИПИ Заказ 11630/45 Тираж 842 Подписное

Филиал ППП "Патент", r. Ужгород, ул.Проектная, 4

Импульсами с выхода нуль-органа 5 первом управляющем входе управлядвоичный вычитающий счетчик 7 -ус- емого вентиля 2 (этот импульс затанавливается в состояние,соответ- крывает управляемый вентиль 2) опствующее коду 2"-1, где p — количест- ределяется как во разрядов счетчика 7. На счетный «7».. Кват.g вход вычитающего счетчика .7 с вы5 2 2" хода генератора 10 импульсов посту- а значение средней за период Т мощпают импульсы с периодом ности, выделенной на нагрузке 3, выразится как

Т

Блок 8 сравнения кодов осуществ» + . р Т» 2 R (" ) ляет сравнение кода, соответствую- щего текущему состоянию вычитающего.... счетчика 7 импульсов и кода N,„z., учитывая выражения (6) и (8), знапоступающего на блок 8 сравнения 15 чение средней мощности будет равкодов с выходов регистра 9 памя- но ти. В момент равенства укаэанных ко- р Оси N g дов импульс с выхода блока 8 срав»» (9) нения кодов поступает на второй управляющий вход управляемого вентиля 2 и открывает его. Переменное напряжение u, (t) подключается к нагрузке 3 с сопротивлением . . При этом длительность интервала времени от момента появления импульса на выходе блока 8 сравнения кодов до момента появления импульса на