Устройство для селекции информационных каналов

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО ДЛЯ СЕЛЕКЦИИ ИНФОРМАЦИШНЫХ КАНАЛОВ, содержащее блокпамяти, счетчик адреса, счетчик тактов,регистр фазы,схему сравнения, выход которой соединен со счетным входом счетчика адреса и управляющим входом блока памяти,первый выход которого является первым выходом устройства , а второй выход соединен с информационным входом регистра фазы, выходкоторого соединен с первым входом схемы сравнения, входы установки счетчика адреса, счетчика тактов и регистра фазы являются входом УСТАНОВКА устройства, счетный вход счетчика тактов Является входом тактовых импульсов устройства, о т л и ч а ющ а а с я тем, что, с целью повышения надежности устройства путем обеспечения защиты от помех, в него введены сумматор, счетчик помех и блок выделения помех, первый и второй выходы которого .соединены с первым и вторым входами счетчика помех, третий вход которого подключен к входу УСТАНОВКА устройства, а выход соединен с первым входом сумматора, второй вход которого соединен с выходом счетчика тактов, а выход соединен с вторым входом схемы сравнения, первый вхсл блока выделения помех подключен к входу тактовых импульсов устройства, а второй вход блока выделения помех является входом ПУСК устройства. 2. Устройство по п. 1, отличающееся тем, что блок выделения помех содержит первый, второй, третий и четвертый триггеры, первый, второй, третий, четвертый и пятый элементы И, элемент ИЛИ, элемент НЕ, счетчик импульсов, генератор импульсов , регистр сдвига и мультиплексор , информационные входы которого соединены с выходами регист ра сдвига, первый вход которого соединен с выходом элемента ИЛИ и входом генератора импульсов, выход котО рого соединен с первым входом первого элемента И, вторым входом регистра сдвига и синхровходов первого триггера, выход которого является первым выходом блока и соединен с W третьим входом регистрасдвига, первый вход элемента ИЛИ соединен -С выходом второго элемента И, первый вход которого соединен с первым входом третьего элемента И, синхровходами второго и третьего триггеров, первым входом блока и входом элемента НЕ, выход которого соединен с первым входом четвертого элемента И, выход которого соединен с входом установки второго триггера, выход которого является вторым выходом блока и соединен с вторым входом четD1 :о эо вертого элемента И, первый выход мультиплексора соединен с первым входом пятого элемента И, выход которого соединен с вторым входом второго элемента И и D-входом первого триггера , второй выход мультиплексора соединен с D-входом второго триггера , второй вход пятого элемента И соединен с первым выходом третьего триггера, второй выход которого соединен с вторым входом первого элемента И и первым входом четвертого триггера, выход которого соединен с вторым входом третьего элемента И и D-входом третьего триггера, а вто

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОЛИСАНИЕ ИЗОБРЕТЕН

Н ABTOPCHOIVIV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3480266/18-24 (22) 06.08 ° 82 (46) 30.01.84. Бюл. М 4 (72) В.M.Гриць, В.С.Лупиков, С.С.Спиваков и A,В.Табачков (53) 681. 327 ° 11 (088. 8) (56) 1. Авторское свидетельство СССР

9 553465, кл. Н 04 У 3/00, 1975.

2. Авторское свидетельство СССР

9 489232, кл. Н 04 J 3/00, 1973

{прототип) . (54)(57) 1, УСТРОЙСТВО ДЛЯ СЕЛЕКЦИИ

ИНФОРМАЦИОННЫХ КАНАЛОВ, содержащее блок. памяти, счетчик адреса, счетчик тактов, регистр фазы, схему сравнения, выход которой соединен со счетным входом счетчика адреса и управляющим входом блока памяти, первый выход KG торого является первым выходом устройства, а второй выход соединен с информационным входом регистра фазы, выход которого соединен с первым входом схемы сравнения, входы установки счетчика адреса, счетчика тактов и регистра фазы являются входом УСТАHOBKA устройства, счетный вход счетчика тактов является входом тактовых импульсов устройства, о т л и ч а ющ е е с я тем, что, с целью повышения надежности устройства путем обеспечения защиты от помех, в него введены сумматор, счетчик помех и блок выделения помех, первый и второй выходы которого .соединены с первым и вторым вхсщами счетчика помех, тре.тий вход которого подключен к входу

УСТАНОВКА устройства, а выход соединен с первым входом сумматора, второй вход которого соединен с выходом счетчика тактов, а выход соединен с вторим входом схемы сравнения, первый вход блока выделения помех подключен к входу тактовых импульсов устройства, а второй вход блока выделения помех является входом ПУСК устройства.

1 (19) (l1)

3(50 G 06 Г 3/04) Н 04 J 3/00

2. Устройство по и. 1, о т л ичающ е е с я тем, что блок выделения помех содержит первый, второй, третий и четвертый триггеры, первый, второй, третий, четвертый и пятый элементы И, элемент ИЛИ, элемент НЕ, счетчик импульсов, генератор импульсов, регистр сдвига и мультиплексор, информационные входы которого соединены с выходами регистра сдвига, первый вход которого соединен с выходом элемента ИЛИ и входом генератора импульсов, выход которого соединен с первым входом перво"

ro элемента И, вторым вхоцом регистра сдвига и синхровходов первого триггера, выход которого является В первым выходом блока и соединен с третьим входом регистра сдвига, .йервый вход элемента ИЛИ соединен с выходом второго элемента И, первый вход которого соединен с первым входом третьего элемента И, синхровходами второго:и третьего триггеров, первым входом блока и входом элемента НЕ, выход которого соединен с первым входом четвертого элемента И, выход которого соединен с входом установки второго триггера, выход которого является вторым выходом блока и соединен с вторым входом четвертого элемента И, первый выход мультиплексора соединен с первым входом пятого элемента И, выход которого соединен с вторым входом второго элемента И и D-входом первого триггера, второй выход мультиплексора соединен с D-входом второго триггера, второй вход пятого элемента И соединен с первым выходом третьего триггера, второй выход которого соединен с.вторым входом первого элемента И и первым входом четвертого триггера, выход которого соединен с вторым входом третьего элемента И и D-входом третьего триггера, а вто1070538 рой вход соединен с вторым входом блока, выход третьего элемента И соединен с вторым входом элемента ИЛИ, входами установки первого триггера

Изобретение относится к вычислительной технике и может быть использовано для ввода данных в системе обработки измерительной информации.

Известны устройства для селекции информационных каналов, осуществляющие селекцию каналов по их временному состоянию и идентификацию их адреса, который передается в систему обработки вместе с сообщением. Временное положение (фаза) сообщений в известных устройствах определяется путем подсчета синхроимпульсов, сопровождающих каждое сообщение, а выделение сообщений осуществляется путем сравнения текущей фазы с фазой выделяемого информационного канала (1) .

Однако известные устройства нейадежны в работе в условиях влия ния помех, особенно если помехам подвергается канал передачи синхроимпульса сопровождения, так как в этом случае текущее значение фазы сообщения не будет соответствовать действительному временному положению этого информационного канала.

Наиболее близким по технической сущности к предлагаемому является устройство для селекции информацион.ных каналов, содержащее счетчик синхроимпульсов сопровождения (тактов) слов и последовательно соединенные счетчик. адреса, оперативное запоминающее устройство (0ЗУ), регистр фазы и схему сравнения, выход которой соединен с управляющим входом

ОЗУ и входом счета счетчика адреса.

Выходы счетчика адреса соединены с адресными входами ОЗУ, второй выход которого является выходом устройства. Входы установки счетчика адреса счетчика тактов слов и регистра фазы подключены к шине маркера цикла, счетный вход счетчика тактов слов соединен с шиной тактов слов(2).

Однако данное устройство также обладает низкой надежностью из-за искажения тактов слов (пропадение или появление ложных тактов) .

Цель изобретения - повышение надежности работы устройства путем обеспечения защиты от помех.

Поставленная цель достигается тем, что в устройство для селекции инфори счетчика импульсов, счетный вход которого соединен с выходом первого элемента И, а выход соединен с адресными входами мультиплексора. мационных. каналов, содержащее блок памяти, счетчик адреса, счетчик тактов, регистр фазы и схему сравнения, выход которой соединен со счетным входом счетчика адреса и управляющим входом блока памяти, первый выход которого является первым выходом устройства, а второй выход соединен с информационным входом регистра фазы, выход которого соединен с первым входом схемы сравнения, входы установки счетчика адреса, счетчика тактов и регистра фазы являются входом УСТАНОВКА устройства, счетный

15 вход счетчика тактов является входом тактовых импульсов устройства, введены сумматор, счетчик помех и блок выделения помех, первый и второй выходы которого соединены с

gp первым и вторым входами счетчика помех, третий вход которого подключен к входу УСТАНОВКА устройства, а выход сбединен с первым входом сумматора, второй вход которого соеди25 нен с выходом счетчика тактов, а выход соединен с вторым входом схемы сравнения, первый вход блока выделения помех подключен к входу тактовых импульсов устройства, а второй

Зр вход блока выделения помех является входом ПУСК устройства.

Блок выделения помех содержит первый, второй, третий и четвертый триггеры, первый, второй, третий, З5 четвеРтый и пятый элементы И, элемент ИЛИ, элемент НЕ, счетчик импульсов,. генератор импульсов, регистр сдвига и мультиплексор, информационные входы которого соединены с выходами регистра сдвига, перый вход которого соединен с выходом элемента ИЛИ и входом генератора импульсов, выход которого соединен с первым входом первого элемента И, вторым входом регистра сдвига и синхро45 входом первого триггера, выход которого является первым выходом блока и соединен с третьим входом регистра сдвига, первый вход элемента ИЛИ соединен с выходом второго элемента

50 И, первый вход которого соединен с первым входом третьего элемента И, синхровходами второго и третьего триггеров, первым входом блока и входом элемента НЕ, выход которого сое55 динен с первым входом четвертого

1070538 элемента И, выход которого соединен с" входом установки второго триггера, выход которого является вторым выходом блока и соединен с вторым входом четвертого элемента И, первый выход мультиплексора соединен с первым входом пятого элемента И, выход которого соединен с вторым входом второго элемента И и D-входом первого триггера, второй выход мультиплексора соединен с 0-входом второго триггера, второй вход пятого элемента И соединен с первым выходом третьего триггера, второй выход которого соединен с вторым входом первого . элемента И и первым входом четверто- )5 го триггера, выход которого соединен с вторым входом третьего элемента

И и D-входом третьего триггера, а второй вход соединен с вторым входом блока, выход третьего элемента И сое-20 динен с вторым входом элемента ИЛИ, входами установки первого триггера и счетчика импульсов, счетный вход которого соединен с выходом первоГо элемента И, а,выход соединен с адрес-25 ными входами мультиплексора °

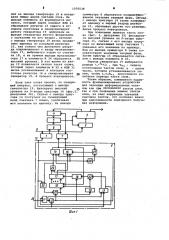

На фиг. 1 представлена Функциональная схема предлагаемого устройства; на фиг. 2 и 3 — временные диаграммы его работы.

Устройство (фиг. 1) содержит счетчик 1 тактов, счетчик 2 адреса, блок

3 памяти. (ОЗУ), регистр 4 фазы, схему 5 сравнения, блок б выделения помех, счетчик 7 помех, сумматор 8, вход УСТАНОВКА 9, вход 10 тактовых импульсов. Блок б выделения помех содержит четвертый триггер 11, третий элемент И 12, третий триггер 13, первый триггер 14, второй триггер 15, регистр 16 сдвига, мультиплексор 17, 40 счетчик 18 импульсов, генератор 19 импульеов,элемент HE 20,элемент ИЛИ, второй элемент HE 20, элемент ИЛИ

21, второй элемент И 22, первый элемент И 23, пятый элемент И 24, 45 четвертый элемент И 25, вход 26 ПУСК.

На временных диаграммах работы при пропадании такта (фиг. 2) обозначены импульс 27 иа входе.26 (пуска измерения); сигнал 28 на выходе 50 триггера) такты 11 и 29 на входе 10 тактов; сигнал 30 на первом выходе

-триггера 13; импульсы 31 на выходе генератора 19; сигналы 32 на первом(пРямом) выхоце мультиплексора 17; сигнал 33 на выходе элемента ИЛИ 21; сигнал 34 на выходе триггера 14

На временных диаграммах работы при появлении ложного такта (фиг. 3) обозначены) такты 35 на входе 10; 60 сигнал 36 на выходе триггера 15 °

Устройство работает следующим образом.

По сигналу маркера цикла, поступающего на вход 9, устанаЪливаются 65 в исходное (нулевое) состояние счетчик 1 тактов, счетчик 2 адреса, счет= чик 7 помех, а в регистр 4 фазы заносится фаза, определяющая первый выделяемый канал в соответствии с фазой его такта слова. Поступакицие на вход 10 такты слов увеличивают содержимое счетчика 1. При равенстве содержимого регистра 4 фазы и кода на выходе сумматора 8(к при отсутствии ложных тактов и пропаданий так» тов), равенстве содержимых регистра

4 и счетчика 1 на выходе схемы 5 сравнения формируется сигнал, по переднему фронту которого .осуществляется считывание кз ОЗУ по адресу в счетчике 2 следумцей фазы и номера (адреса ), выделяемого в данном такте канала, а по заднему — добавление единицы к содержимому счетчика

2 адреса. Считанный из ОЗУ адрес, идентифицирующий выделенный канал, передается вместе с входным словом в систему обработки.

Прн наличии помех или возможности искажения тактов слов перед рабо- .. той устройства на вход 26 подается импульс (фиг. 2, диаграмма 27), устанавливающий триггер 11 (фиг. 2, .диаграмма 28) . С поступлением такта слова (фиг. 2, диаграмма 29) устанавливается триггер 13 (Фиг. 2, диаграьеаа 30), сбрасываются в нулевое состояние счетчики 18 и 7, регистр 16 сдвига принимает исходное состояние значения крайнего правого нулевого разряда — единица значения остальных - нуль}, запускается генератор 19. Импульсы с выхода генератора 19 (фиг. 2, диаграмма 31) поступают на вход сдвига регистра

16 и через элемент 23 и на вход счетчика 18. По каждому импульсу на выходе генератора производится счет счетчика 18 и сдвиг единицы в регистре 16 влево. Код в счетчике 18 определяет выбор соответствующего входа мультиплексора 17. Выходы регистра

16 соединены с мультиплексором fàêèì образом, что в режиме измерения единица, продвигаемая по разрядам регистра 16, последовательно поступает на входы мультиплексора 17, выбкраеьые (подключаемые) значениями счетчика 18,при этом на первом (пряkov) выходе мультиплексора 17 присутствует высокий уровень (фкг. 2, диаграмма 32) . Триггер 11 сброшен установленным триггером 13, поэтому по переднему фронту следующего такта слова низкий уровень на 0-входе триггера 13 сбрасывает его. Сигналы с выхода триггера 13 блокируют поступление импульсов через элемент 23 на вход счета счетчика 18 и открывают элемент И 24. В счетчике 18 зафиксировано число импульсов, сформирован1070538. ных на выходе генератора 19 в интервале между двумя тактами слов. На выходе элемента 22 формируется импульс, который через элемент ИЛИ 21 сбрасывает регистр 16 сдвига в исходное состояние H синхронизирует работу генератора 19 (импульсы на выходе генератора жестко Фазированы с сигналами на его входе) . Сигналы с выхода генератора 19 вновь продвигают единицу по разрядам регистра

16, как только она достигнет разряда подключенного к входу мультиплексора 17, выбранного кодом со счетчика 18, а на прямом выходе мультиплексора 17 и элемента И 24 образуется 15 высокий уровень. В это время на sxoде 10 появляется сигнал такта слова, который через элементы И 22 и ИЛИ 21 вновь устанавливает в исходное состояние регистра 16 и синхронизирует gp генератор 19. И процесс повторяется.

Если такт слова пропал, то следующий импульс, поступающий с выхода генератора 19, фиксирует высокий 2 уровень на D-входе триггера 14 {Фиг.2, диаграмма 34) . Сигнал с выхода триггера 14 поступает на суммирующий вход счетчика 7 помех, увеличивая его значение на единицу. На выходе сумматора 8 образуется скорректиро= ванное значение текущей фазы. Сигнал. с выхода триггера 14 также записывает единицу в первый разряд регистра 16, сбрасывая другие его разряды.

Далее процесс повторяется.

При появлении лишнего такта слова (фиг. 3, диаграмма 35) Фиксируется высокий уровень на 0-входе триггера 15, сигнал с его выхода поступает на вычитающий вход счетчика 7, уменьшая его значение на единицу.

Код на выходе сумматора 8 также соответствует значению текущей фазы.

Затем триггер 15 сбрасывается сигналом с выхода элемента И 25.

Период генератора 19 выбирается равным,- " /, где Тщ — период Щ поступления тактов слов; n — целое число, которое устанавливается таким, чтобы tp 3аТщ допустимого Колебания периода такта слов.

Таким образом, повышается надежность Функционирования устройства для селекции информационных каналов как при пропадании тактов слов, так и при появлении лишних тактов слов, за счет коррекции значений счетчика тактов, что особенно важно при невозможности повторного получения информации.

1070538

ЮО

Риа. 2

Составитель С.Гапич

Редактор Е.Кривина Техред A.Вабинец Корректор A,Повх

Закаэ . ll682/45 Тираж 699 Подписное

ВНИИПИ ГосУдарственного комитета СССР по делам иэобретений и открытий

ll3035, Иосква, Ж-35, Раушская наб,, д. 4/5

Филиал ППП Патент, г.Ужгород, ул.Проектная, 4