Фазовый дискриминатор

Иллюстрации

Показать всеРеферат

ФАЗОВЫЙ ДИСКРИМИНАТОР, содержащий , пять элементов И, два инвертора , линию Эсщержки и два RS-триггера , выход первого из которых соединен с первым входом первого элемента И, выход которого соединен с выходом Отставание устройства, первый вход первого RS-триггера соединен с выходе второго элемента И, первый вход которого подключен к сигнальному входу устройства, выход третьего элемента И соединен с выходом Опережение устройства, первый вход - с выходом второго 53-триггера , первые входы четвертого и пятого элементов И соединены с выходами соответственно первого и второго инверторов, отличающийся тем, что, с целью расширения полосы пропускания и повышения надежности работы, в него введен D-триггер, тактовый вход которого соединен с опорньш входом устройства, входом первого инвертора, вторыми входами второго и пятого элементов И и вторым входом третьего элемента И, третий вход которого через линию задержки соединен с выходом четвертого элемента И, второй вход которого соединен с входом второго инвертора, скгнальньм входом устройства и информационным входом С-триггера,прямой выход которого соединен с чет (Л вертым входом третьего элемента И, а инверсный - с вторым входом первого элемента И, третий вход которого соединен с выходом пятого элемента И, первый вход которого соедид нен с первым входом второго ftS-триггера , второй вход/которого соединен, с выходом первого инвертора и вторь входом первого ftS-триггера.

(1% (И)

y(5g Н .03 0 13/00

COl03 СОВЕТСКИХ

COUNVI

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ,::

Й ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЭОБРЕТЕНИЙ И ОТНРЫПФ (21) 3502899/18-21 (22) 18,10.82 (46) 30.01,84. Бюл. 9 4 (72) В.С. Зимин, Е.П. Коваленко и A.A. Панчук (53) 621 ° 376 ° 5(088.8) (56) 1. Авторское свидетельство СССР

У 497708, кл. Н 03 D 13/00,07.06.74.

2, Авторское свидетельство СССР

В 652685, кл. Н 03 Ъ 13/00,29.09.76 (прототип) . (54)(57) ФАЗОВЫЙ ДИСКРИМИНАТОР содержащий. пять элементов И, два инвертора, ливию задержки и два QS-триггера, выход первого из которых соединен с первым входом первого элемента И, выход которого соединен с выходом Отставание устройства, первый вход первого QS-триггера соединен с выходом второго элемента И, первый вход которого подключен к сигнальному входу устройства, выход третьего элемента И соединен с выходом Опережение устройства, первый вход - с выходом второго З-триггера, первые входы четвертого и пятого элементов И соединены с выходами соответственно первого и второго инверторов, отличающийся тем, что, с целью расширения полосы пропускания и повышения надежности работы, в него введен >-триггер, тактовый вход которого соединен с опорным входом устройства, входом первого инвертора, вторыки входами второго и пятого элементов И и вторьм входом третьего Элемента И, третий вход которого через линию задержки соединен с выходом четвертого элемента И, второй вход которого соединен с входом второго инвертора, сигнальньач входом устройства и информационным входом D-триггера,пря- Я мой выход которого соединен с четвертым входом третьего элемента И, а инверсный - с вторым входом первого элемента И, третий вход которого соединен с выходом пятого элемента И, первый вход которого соеди- нен с первым входом второго RS-триг-гера, второй вход которого соединен. с выходом первого инвертора и вторыл входом первого k3-триггера.

1070684

Изобретение относится к импульсной технике и может быть использовано в устройствах синхронизации с дискретным управлением.

Известен фазовый дискриминатор, содержащий две линии задержки, четыре элемента И, три инвертора,,цва элемента ИЛИ и счетный триггер f13 .

Недостаток данного устройства заключается в повышенной чувствительности к изменению частоты опорного 10 сигнала, что ведет к погрешностям в

Работе устройства.

Наиболее близким, к предлагаемому является фазовый дискриминатор, содержащий шесть элементов И, три инвертора, линию задержки и два RSтриггера, выход первого из которых соединен с первым входом первого элемента И, выход которого соединен с выходом Отставание устройства, первый вход первого К8-триггера сое-., динен с выходом второго элемента И, первый. вход которого подключен к сигнальному входу устройства, выход третьего элемента И соединен с выходом Опережение устройства, а . его первый вход - с выходом второго

QS-триггера, первые входы четверто. го и пятого элементов И соединены с выходами соответственно первого и второго инверторов, кроме того, вход первого инвертора через линию за,цержки соединен с опорным входом устройства и вторым входом четвертого элемента И, выход которого соединен через третий инвертор с вто- 35 ром входом второго элемента И и непосредственно с вторым входом пятого и первым входом шестого элементов И, выход последнего соединен с вторым входом третьего элемента И, первым входом второго RS-триггера и вторым входом первого элемента И, третий вход которого соединен с вторым выходом второго RS-триггера, второй вход которого соединен с первым 45 входом первого RS -триггера, второй вход которого подключен к выходу пятого элемента И, а вход второго инвертора и второй вход шестого элемента И подключены к сигнальному входу устройства.f23.

Недостатком известного устройства является его узкополосность и в результате этого низкая надежность работы, так как любой уход параметров линии задержки от номинальных, а так-55 же любое изменение частоты входного сигнала приводит к искажению выходной информации устройства.

Цель изобретения — расширение полосы пропускания и повышение надеж- 60 ности работы. фазового дискриминатора.

Поставленная цель достигается тем, что в устройство, содержащее пять элементов И, два инвертора, линию задержки и два RS -триггеРа, выход пер- 65.вого из которых соединен с первым входом первого элемента И, выход ко.«торого соединен с выходом Отставание устройства,первый вход первого $-триггера соединен с выходом второго элемента И, первый вход которого подключен к сигнальному входу устройства, выход третьего элемента И соединен с выходом Опережение устройства, первый вход — с выходом второго %8 -триггера, первые входы четвертого и пятого элементов И соединены с выходами соответственно первого и второго инверторов, введен

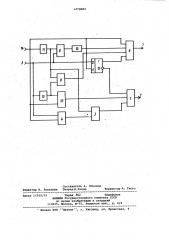

D-триггер, тактовый вход которого соединен с опорным входом устройства, входом первого инвертора, вторыми входами второго и пятого элементов И и вторым входом третьего элемента И, третий вход котброго через линию задержки соединен с выходом четвертого элемента И, второ13 вход которого соединен с входом второго инвертора, сигнальным входом устройства и информационным входом Э-триггера, прямой выход которого соединен с четвертым входом третьего элемента И, а инверсный — с вторым входом первого элемента И, третий вход которого соединен с выходом пятого.эле-мента И, первый вход которого соединен с первым входом второго 8— триггера, второй вход которого соединен с выходом первого инвертора и вторым входом первого 5-.триггера. На чертеже приведена структурная схема фазового дискриминатора. фазовый дискриминатор содержит первый элемент И 1, выход которого соединен с выходом 2 Отставание, первый вход элемента 1 соединен с выходом первого Ъ -триггера 3., первый вход которого соединен с выходом ,второго элемента И 4, первый вход элемента 4 подключен к сигнальному входу 5 устройства, выход третьего элемента И 6 соединен с выходом 7 Опережение устройства, а его первый вход — с выходом BTopoFORS— триггера 8, первые входы четвертого и пятого элементов И 9 и 10 соединены с выходами соответственно первого и второго инверторов ll и 12, тактовый вход D-триггера 13 соединен с опорным входом 14 устройства, входом инвертора 11, вторыми входами элементов 4, 6 и 10, третий вход элемента 6 через линию 15 задержки соединен с выходом элемента 9 второй вход которого соединен с входом инвертора 12, сигнальным входом

5 и информационнйм входом D-триггера 13, прямой выход которого соединен с четвертым входом элемента 6, а инверсный - с вторым входом элемента 1, третий вход которого соединен с выходом элемента 10, первый вход которого соединен с первым входом кВ-триггера 8, второй вход

1070684 которого соединен с выходом ннвертора 11 и вторым входом RS -триггера 3.

Устройство работает следующим образом.

На информационный вход Э -триггера 13 поступает сигнал с сигнального входа 5, на тактовый вход — с

° опорного входа 14 (частота опорного сигнала ниже частоты входного). Если передний фронт сигнала на инфор- 10 мационном входе Ь-триггера 13 опережает передний фронт сигнала на его тактовом входе, то на его прямом выходе установится единичный уровень, который поступаст на вход элемента 6 и разрешает формирование сигнала на его выходе, Напротив, нулевой уровень с инверсного выхода D-триггера

13 поступает на вход элемента 1 и запрещает формирование каких-либо сигналов на его выходе. Если же передний фронт сигнала на информационном входе Ь-триггера 13 отстает от переднего фронта сигнала на его тактовом входе, то разрешается Формирование сигналов на выходе элемента 1 и запрещается на выходе элемента 6.

Таким образом, состояние D-триггера 13 определяет знак отклонения. фазй входного сигнала от фазы опорного сигнала. Для формирования сигнала на выходе 7 на входы элемента 9 подается проинвертированный инвертором 11 сигнал с входа 14 и сигнал с входа 5. Сигнал с выхода элемента

9 поступает через линию 15 на вход 35 элемента 6.

Линия задержки в предлагаемом устройстве необходима для выделения участка полезного сигнала (в преде-. лах полупериода входного сигнала), 40 поступающего с входа 5, и величина времени задержки может составлять

0,75-1,5 периода этого сигнала. Стро-. бирование полезного сигнала после линии 15 осуществляется RS-триггером 8 подачей соответствующего уровня на вход элемента 6.

Для формирования сигнала на выходе 2 используется стробирование полезного сигнала при помощи $-триггера 3 подачей соответствующего уровня на вход элемента 1.

Сигнал Опережение формируется следующим образом. Сигнал единичного уровня с выхода инвертора 11 поступает на второй (нулевой) вход

QS-триггера 8 и создает на его выходе (прямом) нулевой уровень, кото-. рый запрещает формирование сигналов на выходе элемента. 6. К моменту же появлейия полезного сигнала на вы-60 ходе линии 15 на втором входе %8— триггера 8 единичный уровень сменится нулевым, а на первый (единичный) вход этого триггера с выхода инвертора 12 поступит единичный уровень, который переключит ($ -триггер 8 в единичное состояние, разрешающее формирование сигнала на выходе элемента 6. После формирования на выходе 7 сигнала нулевой уровень на выходе инвертора 11 сменится на единичный, который переключит Й8 -триггер 8 в нулевое состояние.

Сигнал Отставание формируется следующим образом, При отсутствии полезнога сигнала на третьем входе элемента l на первый его вход с выхода (прямого) $ -триггера 3 посту ает нулевой уровень, запрещая формирование сигнала на выходе 2. Разрешающий сигнал с выхода 8 «триггера 3 поступает в момент, когда на его втором (единичном) входе с выхода инвертора ll появится единичный уровень. Полезный сигнал с выхода элемента 10, образованный из сигнала на опорном входе 14 и проинвертированный инвертором 12 сигнала ка сигнальном входе 5, поступает на третий вход элемента 1, при этом на выходе этого элемента Формируется импульс. После этого единичный уровень на выходе инвертора 11 сменяется нулевым, а единичный уровень с выхода элемента 10 переключит RSтриггер 3 в нулевое состояние.

Таким образом, если передний фронт импульса на сигнальном входе опережает передний фронт импульса на опорном входе, то формируется сигнал на выходе 7, в противном случае — на выходе 2, при этом частота входных сигналов может изменяться в широком диапазоне.

Введение дополнительного элемента D -триггера и новых связей между элементами приводит к тому, что сравнение входных сигналов по фазе осуществляется непосредственно, а не после задержки одного из них в линии задержки как в прототипе, что позволяет в широких пределах менять задержку сигнала в линии по сравнению с периодом импульсов на сигнальном входе, т.е. расширяет полосу пропускания фазового дискриминатора.

Кроме того, повышается надежность работы фазового дискриминатора, так как и при изменении s широких пределах интервала запаздывания сигнала в линии-задержки, и при отклонении частоты сигнала на сигнальном входе от номинальной, качество работы уст- . ройства не ухудшается.

Таким образом, при ойтимальном выборе интервала запаздывания сигнала в линии задержки сяя в предла гаемом фазовом дискриминаторе, равном шд 4/37 где 1 — средняя частота диапазона, в которой может перестраиваться частота входного сигнала, фазовый дискриминатор обладает относительным диапазоном рабочих частот, равным 66%.

107 0б84

Заказ 11702/53

: Тираж 8б2 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4

Составитель А. Соколов

Редактор Н. Ковалева Техред М.Тепер Корректор A- Тяско