Тиристорный ключ

Иллюстрации

Показать всеРеферат

ТИРИСТОРНЬт КЛЮЧ, содержа щий две параллельные цепи, одна из которых состоит из последовательно включенных тиристоров, а другая из последовательно включенных выравнивающих резисторов, отлич ющийся тем, что, с целью повышения КПД, между анодом и катодом каждого тиристора за исключением крайнего подключены цепочка, в которой соединены последовательно транзистор п-р-п проводимости коллекторно-эмиттерным переходом и диод в прямом направлении в цепи эмиттера транзистора, причем база каждого транзистора подключена к точке соединения выравнивающих резисторов, а параллельно крайнему тиристору подключен транзистор провод| ости коллекторно-эмиттерным переходом , база которого соединена с базой следующего транзистора, при этом переход база-эмиттер каждого транзистора шунтирован резистором.

COOS СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ Г

К ABTOPCHOMY СВИДЕТЕЛЬСТВ .Ф

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3498510/18-21 (22) 11.10.82 (46) 30.01.84. Бюл. )) 4 (72) С.И. Москаленко, В.Е. Ткачук . и И.В. Шамрина (53) 621. 374. 3 (088. 8) (56) 1. Тиристоры. Технический справочник. М., Энергия, 1971, с. 152, рис. 6-10.

2. Авторское свидетельство СССР

Р 741471, кл. Н 03 К 17/72, 1980, (54) (57) ТИРИСТОРНЫЙ КЛЮЧ, содержащий две параллельные цепи, одна из которых состоит из последовательно включенных тиристоров, а другая из последовательно включенных выравнивающих резисторов, о т л и ч а„Л0„„10 1 А

3(51) Н 03 К 17/56 H 03 К 17 72 ю шийся тем, что, с целью повышения КПД, между анодом н катодом каждого тиристора за исключением крайнего подключены цепочка, в кото.рой соединены последовательно транзистор и --р- п проводимости коллекторно-эмиттерным переходом и диод в прямом направлении в цепи эмиттера транзистора, причем база каждого транзистора подключена к точке соединения выравнивающих резисторов, а параллельно крайнему тиристору подключен транзистор р -n-р проводи @ости коллекторно-эмиттерным переходом, база которого соединена с базой следующего транзистора, при этом переход база-эмиттер каждого .транзистора шунтирован резистором.

1070691

Изобретение относится к устройствам для запуска группы последовательно соединенных тиристоров и может быть использовано, например, в импульсной технике при формировании мощных высоковольтных импульсов. 5

Известен тиристорный ключ, содержащий группу последовательно соединенных тиристоров, каждый из которых шунтирован диодом с лавинной вольт-амперной характеристикой Г11. 10

Недостатком данного тиристорного ключа является низкий КПД, так как выравнивание напряжений на тиристорах обеспечивается за счет значительных потерь энергии в дели- )5 теле напряжения, выполненном на диодах с лавинной вольт-амперной характеристикой.

Наиболее близким к предлагаемому является тиристорный ключю содержа» 2О щий две параллельные цепи, одна иэ которых состоит из последовательно включенных тиристоров, а другая из последовательно включенных выравнивающих резисторов 121.

Недостатком известного устройства является также низкий КПД, так как в резистивном делителе напряжения воз никают потери энергии, которые в, несколько раз превышают потери энергии в тиристорах за счет токов 30 утечки.

Цель изобретения — повышение КПД тиристорного ключа.

Поставленная цель достигается тем, что в тиристорном ключе, содержащем 35 две параллельные цепи, одна из которых состоит из последовательно включенных тиристоров, а другая из последовательно включенных выравнивающих резнсторов, между анодом и 4П катодом каждого тиристора эа исключением крайнего подключены цепочка, в которой соединены последовательно транзистор и -р- проводимости коллекторно-эмиттерным переходом и диод

45 в прямом направлении в цепи эмиттера транзистора, причем база каждого транзистора подключена к точке соединения выравнивающих резисторов, а параллельно крайнему тиристору подключен транзистор р-и-р проводимости коллекторно-эмиттерным переходом, база которого соединена с базой следующего транзистора, при этом переход база-эмиттер каждого транзистора шунтирован резистором. 55

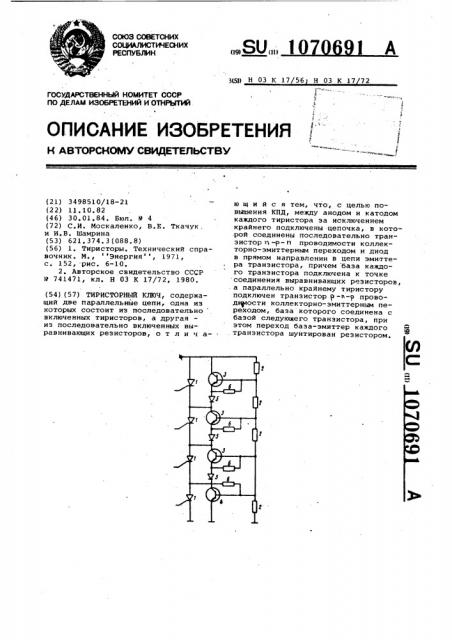

На чертеже приведена принципиальная электрическая схема тиристорного ключа.

Тиристорный ключ содержит цепоч ку последовательно соединенных ти- 60 ристоров 1 и параллельно ей включенный реэистивный делитель напряжения, состоящий из последовательно соединенных выравнивающих резисторов 2.

Параллельно каждомУ тиристору 1 кро 65 ме одного крайнего, подключенногп к общей шине, включены цепочки, с держащие соединенные последовательно транзисторы Эи -р-и проводимости и согласно с ним включенный в эмиттерную цепь диод 4. Базы транзисторов 3 подключены к соответствующим точкам соединения резисторов 2. Параллельно крайнему тиристору 1 подключен транзистор 5 ф-с -Р проводимости, база которого соединена с базой соседнего с ним транзистора 3. Переход база-змиттер каждого транзистора 3 и 5 шунтирован резистором fi.

Все транзисторы 3 и 5 включены по схеме эмиттерного повторителя. Следовательно, потенциалы на эмиттерах транзисторов 3 и 5 равны потенциалам на их базах и определяются резис тивным делителем напряжения, который служит источником опорного напряжения. Пусть статические сопротивления всех тиристоров, а соответствен«о и их токи утечки одинаковой величины. Тогда падение напряжения на всех тиристорах одинаково и в схеме протекают лишь токи утечки тиристоров 1, транзисторов 3 и 5 и ток делителя напряжения на резисторах 2.

Так как делитель напряжения используется в качестве опорного, то потребление его от источника будет незначительным, в результате чего КПД коммутатора будет высоким.

Рассмотрим четыре случая, когда сойротивление утечки одного из тиристоров отличается от сопротивлений утечки равной величины всех остальных тиристоров.

Первый случай. Пусть нижний тиристор обладает наибольшим сопротивлением утечки, Тогда потенциал эмиттера транзистора 5 будет выше потенциала его базы, и транзистор 5 приоткроется, шунтируя этот тиристор, уменьшая тем самым суммарное сопротивление утечки тиристора 1 и параллельно с ним включенного транзистора 5. Напряжение на тирйсторе 1 уменьшится,до величины. задаваемой резистивным делителем напряжения на резисторах 2. Дальнейшего уменьшения напряжения на тиристоре не произойдет, так как при уменьшении потенциала эмиттера до потеициала его базы транзистор 5 начнет закрываться.

Второй случай. Пусть наибольшим сопротивлением утечки обладает тиристор 1. Тогда на нем будет наибольшее падение напряжения, в результате чего потенциал эмиттера параллельного ему транзистора 3 б,дет ниже потенциала его базы. Транзистор 3 приоткроется.

Происходит уменьшение падения напряжения на параллельно ему включенном тиристоре 1, как и в предыдущем случае. Аналогичный процесс

1070691

Составитель А. Бомко

Редактор Н. Ковалева Техред A.Áàáèíåö Корректор О. Билак

Тираж 862 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, X- 35, Раушская наб., д. 4/5

Заказ 11702/53

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4 происходит, ссли наибольшим сопротивлением утечки обладает тиристор 1, находящийся в середине цепочки тиристоров.

Третий случай. Пусть нижний тиристар 1 обладает наименьшим сопротивлением. Тогда падение напряжения на нем ниже, чем на остальных тиристорах, и потенциал эмиттера транзистора 3, параллельного тиристору 1, расположенному над рассматриваемым, 10 ниже потенциала его базы. Транзистор

3 приоткрывается, шунтируя свой тиристор 1 и понижая потенциал эмиттера следующего, находящегося над ним транзистора 3. Этот транзистор тоже приоткрывается до тех пор, пока суммарные сопротивления всех тиристоров 1 с параллельными им транзисторами 3 не уменьшатся до сопро- тивления утечки нижнего тиристора 1.

Четвертый случай. Пусть верхний тиристор 1 имеет наименьшее сопротивление утечки. Тогда падение напряжения на нем будет меньше, чем напряжение, задаваемое реэистивным делителем напряжения, а, следователь но, на всех остальных тиристорах 1 выше этого напряжения ° Поэтому, как показано выше, транзисторы 3 и 5, начиная с нижнего, будет последовательно приоткрываться, пока сопротивле- 30 ние утечки каждого из тиристоров 1 с включенным параллельно ему транзистором 3 или 5 не достигнет величины утечки верхнего тиристора 1, имеющего наименьшее сопротивление утечки. 35

Если тиристор с наименьшим сопротивлением утечки находится в середине цепочки последовательно включенных тиристоров 1, то процесс выравнивания напряжений представляет собой комбинацию третьего и четвертого случая.

Процесс выравнивания напряжений на цепочке последовательно включенных тиристоров 1 с различными сопротивлениями утечки представляет собой комбинацию четырех случаев.

Диоды 4, включенные последовательно и согласно в эмиттврную цепь транзисторов 3, не влияют на процесс выравнивания напряжений на тиристорах 1, так как прямое падение напряжения на них незначительно, и служат для развязки взаимного шунтирования тиристоров 1 с наибольшими сопротивлениями утечки и резисторов

2 реэистивного делителя напряжения.

-Резисторы б являются сопротивлениями утечки транзисторов 3 и 5.

Таким образом, в схеме осуществляется автоматическое выравнивание величины тока утечки каждого иэ последовательно соединенных тиристоров l совместно с транзисторами 3 и 5 до величины тока утечки тиристора 1 с наименьшим сопротивлением утечки (наибольшим током утечки), что не требует предварительного подбора элементов схемы. Так как в каждой паре тиристор 1 — транзистор 3 (5). протекает ток, по величине, не превышающий максимальный ток утечки тиристора 1 с наименьшим сопротивлением утечки, а резистивный делитель напряжения на резисторах 2 потребляет ток минимальной величины, то потери энергии в тиристорном ключе IIpH мерно в 10 раз меньше, чем в схеме с шунтирующими резисторами.