Устройство для цифрового формирования сигналов с амплитудно- фазовой модуляцией

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ЦИФРОВОГО ФОРМИРОВАНИЯ СИГНАЛОВ С АМПЛИТУДНОФАЗОВОЙ МОДУЛЯЦИЕЙ, содержащее источник данных, выход которого соединен с входами первой и второй линий задержки, первый и второй Ллоки памяти, выходы которых подключены к первым входамсоответственно первого и второго перемножителей , выходы которых соединены с входами сумматора, выход которого через цифроаналоговый преобразователь подкршчен квходу фильтра нижних частот, отличающееся тем, что,, с целью повышения точности формирования, введены два дополнительных блока памяти и первый и второй деижфраторы, выходы которых подключены к первым входам соответственно первого и второго дополнительных блоков памяти, выходы которых соединены с вторыми входами соответственно первого и второго перемножителей, причем выходы первой и второй линий задержки под- § ключены к входам соответственно первого и второго дешифраторов, а /Л вторые входы первого и второго дополнительных блоков памяти и входы первого и второго блоков памяти являются модуляционными входами устройства . 1 О о со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН 3(59 Н 04 Ь 27 18

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3374750/18-09 (22) 25.12.81 (46) 30.01.84. Бюл. 9 4 (72) В.В.Малеженков, В.А.Свириденко, Л.С.Татарский и M.Ñ.Äàâëèêàíoâà (71) Московский институт инженеров гражданской авиации (53) 621. 394. 14 (088. 8) (56) 1. Данилов Б. С. и др. Однополосная передача цифровых сигналов., М., Связь, 1974, с.59.

2. Выполнение высокоскоростных модемов на микро-ЭВМ. Экспресс-информация. Сер. Передача информа" ции, M. BHHHTH.1978 9 5 с.5-21 (прототип). (54.)(57) УСТРОЙСТВО ДЛЯ ЦИФРОВОГО

ФОРМИРОВАНИЯ СИГНАЛОВ С АМПЛИТУДНОФАЗОВОИ МОДУЛЯЦИЕя, содержащее источник данных, выход которого соединен с входами первой и второй линий задержки, первый и второй блоки памяти, выходы которых подключены к первым входам соответст„„gu„„ 1070703 А венно первого и второго перемножителей, выходы которых соединены с входами сумматора, выход которого через цифроаналоговый преобразователь подключен к входу фильтра нижних частот, о .т л и ч а ю щ е е с я тем, что, с целью повышения точности формирования,. введены два дополнительных блока памяти и первый и второй дешифраторы, выходы которых подключены к первым входам соответственно первого и второго дополнительных блоков памяти, выходы которых соединены с вторыми входами соответственно-первего и второго перемножителей, причем выходы пер-вой и второй линий задержки под- ф ключены к входам соответственно первого и второго дешнфраторов, а вторые входы первого и второго дополнительных блоков памяти и входы первого и второго блоков памяти являются модуляционными входами уст- Я ройства.

1070703

Изобретение относится к -технике связи и может быть, использовано в системах передачи данных и телемет» рии.

Известно устройство для формирования сигналов. с амплитудно-фаэовой модулидией, содержащее кодер, выход которого подключен к входу цифрового трансверсильного фильтра, выходы которого через соответствующие Фильтры нижних частот соединены с входами модуляторов, выходы которых подключены к входам сумматора, выход которого соединен с входом выходного Фильтра нижних частот f1 3.

Недостатком данного устройства является низкая точность формирования.

Наиболее близким техническим решением к изобретению является устройство, содержащее источник данных, выход которого соединен с входами первой и второй линий задержки, первый и второй блоки па" мяти, выходы которых подключены к первым входам соответственно первого и второго перемножителей, выходы которых соединены с входами сумматора, выход которого через цифроаналоговый преобразователь подключен к входам фильтра нижних частот. Е23.

Однако известное устройство обладает низкой точностью формирования сигналов.

Цель изобретения — повышение точности формирования.

Для достижения указанной цели в устройство для цифрового фгкрмирования сигналов с амплитудно-фаэовой модуляцией, содержащее источник данных, выход которого соединен с входами первой и второй линий задержки, первый и второй блоки памяти,. выходы которых подключены к первым входам соответственно первого и второго перемножителей, выходы которых соединены с входами

:сумматора, выход которого через цйфроаналоговый преобразователь подключен к входам фильтра нижних частот, введены два дополнительных блока. памяти и первый и второй дешифраторы, выходы которых подключены к первым входам соответствен-: но первого и второго дополнительных блоков памяти, выходы которых соединены с вторыми входами соответственно первого и второго перемножителей,. причем выходы первой и второй линий. задержки подключены

- к входам соответственно первого и !

1 второго дешифраторов, а вторые входы первого и второго дополнительных

63 оков памяти и входы первого и второго блоков памяти являются модуляционными входами устройства.

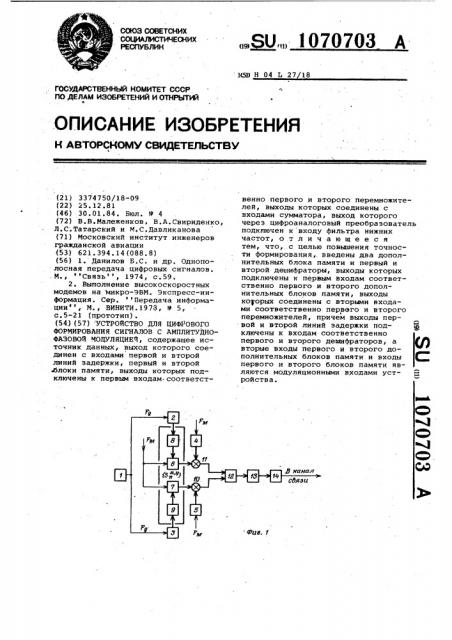

На фиг.1 - изображена структурная. электрическая схема предлагаемого устройства;,на фиг.2 — диаграмма формирования сигнала.

Предлагаемое устройство для

5 цифрового формирования сигнала с амплитудно-фаэовой модуляцией содержит источник 1 данных, линии 2 и 3 задержки, блоки 4 и 5 памяти, дополнительные блоки 6 и 7 памяти, дешифраторы 8 и 9, перемножители

10 и 11, сумматор 12, цифроаналоговый преобразователь 13, фильтр 14 нижних частот.

Устройство работает следующим образом °

Для требуемой формы спектра частот передаваемого сигнала предварительно рассчитываются дискретные параметры частотной характеристики е формирующего фильтра (не показан)

f h„ %, 1 = О,N-1 (N - число рассчитываемых коэйфициенРов) из выражения

Я, 51 Я 171 сО5Я 171

1Э где Я„половина ширины полосы . пропускания формирующего фильтра по уровню 0,5 для двухполосных систем модуляции; частота дискретизации импульсной характеристики, формирующего фильтра (во временной области);

Т

П коэффициент округления спектра формируемого сигнала (в частотной области); половина ширины области скругления спектра сигнала;

1 = 0,1,2 ° .....

45 N — число рассчитываемых коэффициентов.

Полученный набор двоичных чисел

)h; ), i =0,N-1, представляет собой квантованные отсчеты импульсной

50 реакции формирующего фильтра, -посредством математической операции . дискретной свертки. й"1

М-4

И, .. - ) 1 р..1

55 " - п1 =0

i=o с элементами расщепленной послед .вательности входных данных fX„), gY 3 пересчитываются в набор результатов S, S„ идентичных операций х г

60 цифровой фильтрации, которые записываются соответственно в блоки 6 и 7.памяти.

В блоки 4 и 5 памяти также предварительно записываются числа, Представляющие собой квантованные

1070703

Жив. 2

BHHMIH . Заказ 11704/54 Тираж 635 ПОдписное

Филиал ППП "Патент", г, Ужгород, ул. Проектная, 4 отсчеты ортогональных составляющих несущей частоты ы„ используемой модуляционной системы: (созш„пТ и в1пш„пТ ), где Т - период модуляции, и = 1,2,3...... йнформация о йсточника 1 данных 5 в последовательном коде поступает с частотой F данных на входы линий

2 и 3 задержки. Линии 2 и 3 задержки имеют (m -N); выходов, где Nчисло отводов линии задержки, равное числу предварительно рассчитанных коэффициентов, идентичных коэффициентам при цифровой фильтрации, а m = F>/F (Г„ - частота модуляции) представляет собой число объединяемых(5 в группы битов входных данных для согласования скорости передачи от источника 1 данных и скорости модуляции.

Двоичные числа с выходов линий ъО

2 и 3 задержки, представляющие собой задержанные íà N тактов частоты модуляции Г„ случайную комбинацию с выхода источника 1 данных, поступают соответственно на (m-N) входов дешифратора 8 и (mN) входов дешифратора 9, которые преобразуют (дешифрируют) эти случайные комбинации в адресную инФормацию одного иэ 2 адресов соответственно блока 6 памяти и блока 7 памяти,,где хранятся 2 предварительно рассчитанных и записанных результатов, аналогичных цифровой фильтрации входной последовательности данных (т,е. дискретной свертки координат (Х,YJ используемого модуляционного формата с N отсчетами импульсной реакции (h;) i=G,N-l, Формирующего фильтра).

Наличие адресной информации на входе блока 6 памяти и входе блока 7 памяти приводит к появлению на их выходах результатов S, Я .

Считанные иэ блоков памяти 6 и 7 памяти с частотой модуляции F сигналы (многоразрядные двоичные числа) S u S поступают, на перемнбжителй 10 и 11 соответственно, где осуществляется их модуляция ортогональню и отсчетами (совщнпТм и в1п см„пТ„) несущей частоты w> соответственно, которые хранятся в . блоках 4 и 5 памяти соответственно и считываются из них также с частотой модуляции Fl,.

Модулированные ортогональные сигналы суммируются в сумматоре 12,.Й после преобразования в цифроаналоговод преобразователе 13 и фильтрации в Фильтре 14 нижних частот сформированный модулированный сигнал

К-1

5(пт )к x(T -4т )%(ат (саби„лт,+ з=О н-

++ Y(T -i7 )Ъ (iT )в!л ю пТ (=О поступает в канал связи.

Таким образом, введение новых блоков позволило повысить точность формирования сигналов с амплитуднофазовой модуляцией.