Устройство для диагностики цифровых узлов

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО ДЛИ даАГНОСТИКИ ЦИФРОВЫХ УЗЛОВ, содержащее первыЯ блок.индикации, зонд, соединенный входом с клеммой для подключения вывода диагностируемого ци(й ового узла, блок контроля, соединенный Первыми киходами и перилми входами соответственно с клеммами для подт ключения входов и выходов диагности руемого ци45 ового узла, блок управтения и блок сравнения, о т л и чающееся тем, что, с целью повышения достоверности результатов jдиагностики и быстродействия устройства , в него введены элемент задержки , счетчик, деши 1ратор, мультиплексор , вторые блоки индикации, каждый из блоков индикации содержит переключатели , элементы индикации и первый элемент ИЛИ, причем пед)вый выход блока управления соединен с вторым входом блока контроля и со счетным входом счетчика, соединенного выходами с входами дешифратора, установочным входом с вторым выходом блока управления и с третьим -ходом блока контроля, соединенного вторым выходом с входом блока управления, вторый вход которого соединен с пер ,вым клходом блока сравнения, соединенного первым входом с выходом зонда, вторым выходом непосредственно с третьим входом блока управления , а элемент задержки с четвертым входом блока управления, соединенного третьими выходами сjg первыми входами мультиплексора, сое (Л диненного выходом с вторым входом блока сравнения, вторыми входами с выходами соответствующих первых элементов ИЛИ, выходы дешифратора соединены с входами одноименных переключателей каждого из блоков индикации, выходы переключателей соединены с входами соответствующих элементов индикации и с соответствующими входами первого элемента ИЛИ данного блока индикации. со 1 со

союз советсних социАлистичесних

РЕСПУБЛИН (19) (И) 31 28

ОПИСАНИЕ. ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР по делАм изОБРетений и ОтнРытий (21) 35 13510/18-21 (22) 19.11.82 (46) 07.02.84. Вюл. 9 5 (72) Е.И..Николаев и Е.З.Храпко

i (53) 684. 326 (088.8) (56) 1. Авторское свидетельство СССР

9 441532, кл. G 01 R 31/28, 1974.

2. Авторское свидетельство СССР

9 708269, кл. G 01 R 31/28, 1978 (прототип) . (54) (57) 1. УСТРОЙСТВО ДЛИ ДИАГНОСТИКИ ЦИФРОИ4Х УЗЛОВ, содеРжащее пеРвый блок индикации, зонд, соединенный входом с клеммой для подключения вывода диагносюируемого цифрового узла, блок контроля, соединенный первыми выходами и первыми входами соответственно с клеммами для под-, ключения входов и выходов диагностируемого цифрового узла, блок управчения и блок сравнения, о т л и ч а ю щ е е с я тем, что, с целью повиаения достоверности результатов

I диагностики и быстродействия устройства, в него введены элемент задержки, счетчик, дешифратор, мультиплексор вторые блоки индикации, каждый из блоков индикации содержит переключатели, элементы индикации и первый элемент ИЛИ, причем первый выход блока управления соединен с вторым входом блока контроля и со счетным входом счетчика, соединенного выходами с входами дешифратора, установочным входом с вторым mxogoM блока управления и с третьим ."ходом блока контроля, соединенного вторым выходом с первым входом блока управления, вторый вход которого соединен с пер" .вым выходом блока сравнения, соединенного первым входом с выходом зонда, вторым выходом непосредственно с третьим входом блока управления, а через элемент задержки с четвертым входом блока управления, .соединенного третьими выходами с первыми входами мультиплексора, соединенного выходом с вторым входом блока сравнения, вторыми входами с выходами соответствующих первых элементов ИЛИ, выходЫ дешифратора соединены с входами одноименных переключателей каждого из блоков индикации, находы переключателей со динены с входами соответствующих элементов индикации и с соответствующими входами первого элемента ИЛИ данного блока индикации, 1071979

2 ° Устройство по п. 1, о т л и ч а ю щ е е с я тем, что блок управления содержит элемент И, соединенный первым и вторым входами с одноименными входами блока, первый генератор одиночных импульсов, соединенный выходом с первым входом второго элемента ИЛИ, соединенного соответственно вторым входом и выходом с третьим входом и первым выходом блока, четвертый вход которого соеI

Изобретение относится к контрольно-измерительной технике и может быть использовано для диагностики неисправйостей цифровых узлов.

Известно устройство для обнаружения неисправностей в логических схемах, содержащее счетчик, выход которого соединены с блоком регистрации, эталонным блоком и RQHTpoJIHpyeMMM блоком, соединяемым своими выходами о с соответствующими входами блока .регистрации и блока сравнения, вторые входы которого подключены к выходам эталонного блока,- а выходы к блока индикации и регистрации (1 3.

Однако устройство имеет ограниченную область применения, так как не может быть использовано при диагностике неисправностей цифровых узлов.

Наиболее близким техническим решением к изобретению является устройство для контроля интегральных микросхем, входящих в состав диагностируемого цифрового узла, содержащее зонд, соединенный входом с клеммой для подключения вывода контролируемой микросхемм, блок контроля, соединенный первыми выходами и первыми входами с клеммами для подключения входов и выходов диагностируемого цифрового узла, блок управления и блок сравнения (2 ).

Недостатками известного устройства являются недостаточная достоверность результатов диагностики и низкое быстродействие. Недостаточная 35 достоверность результатов диагнос-. тики обусловлена тем, что при контроле микросхем, находящихся на пути от неправильно функционирующего выхода цифрового узла до места неисправности используются эталонные микроcxew, полная гарантия работоспособности которых отсутствует.

Низкое быстродействие определяется необходимостью замены эталонных микросхем при смене типов контролируемых микросхем, находящихся на пудинен с первым входом третьего зле . мента ИЛИ, соединенного вторым входом с выходом элемента И, третьим входом с выходом второго генератора одиночных импульсов, выходом с вторым выходом блока, соединенного третьими выходами с выходами дополнительного счетчика, первый и второй входы которого соединены с выходами третьего и четвертого генераторов одиночных импульсов,соответственно.

2 ти поиска неисправности, а также существенными затратами времени на прием и запись информации по каждому выводу каждой микросхемы на всех словах текста в процессе записи диагностической информации.

Цель изобретения — повышение достоверности результатов диагностики и быстродействия устройства.

Поставленная цель достигается тем, что в устройство для диагностики цифровых узлов, содержащее первый блок индикации, зонд, соединенныи входом с клеммой для подключения вывода диагностируемого цифрового узла, блок контроля, соединенный первыми выходами и первыми входамн соответственно с клеммами для подключения входов и выходов диагностируемого цифрового узла, блок управления и блок сравнения, введены элемент задержки, счетчик, дешифратор, мультиплексор и вторые блоки индикации, каждый из блоков индикации содержит переключатели, элементы индикации и первый элемент ИЛИ, причем первый выход блока управления соединен с вторым входом блока контроля и со счетным входом счетчика, соединенного выходами с входами дешифратора, установочным входом с вторым выходом блока управления и с третьим входом блока контроля, соединенного вторым выходом с первым входом блока управления, второй вход которого соединен с первым выходом блока сравнения, соединенного первым входом с выходом зонда, вторым выходом непосредственно с третьим входом блока управления, а через элемент задержки с четвертым входом блока управления, соединенного третьими жгходами с первыми входами мультиплексора, соединенного выходом с вторым входом блока сравнения, вторыми входами с выходами соответствующих первых элементов ИЛИ, выходы дешифратора соединены с вхо1071979 дами одноименных переключателей, каждого из блоков индикации, выходы переключателей соединены с входами соответствующих элеменТов индикации и с соответствующими входами первого элемента ИЛИ данного блока индикации.

Цуоме того, блок управления содержит элемент И, соединенный первым и вторым входами с одноименными входами блока, первый генератор одиночных импульсов, соединенный выходом с первым входом второго элемента ИЛИ, соединенного соответственно вторым входом и выходом с третьим входом и первым выходом блока, чет- 15 вертый вход которого соединен с первым входом третьего элемента ИЛИ, соединенного вторым входом с выходом элемента И, третьим входом с выходом второго генератора одиноч- 20 ных импульсов, находом с вторым выходом блока, соединенного третьими выходами с выходами дополнительного счетчика., первый и второй входы ко-. торого соединены с выходами третье- 25 го и четвертого генераторов одиночных импульсов соответственно.

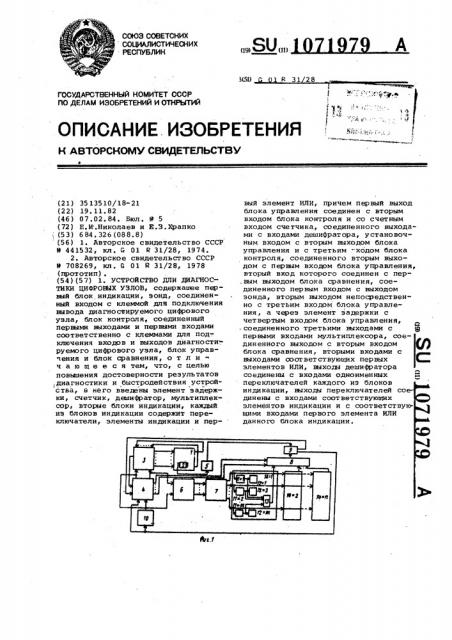

На фиг. 1 приведена блок-схема устройства; на фиг. 2 — функциональная схема блока упраняения. 30

Устройство для диагностики цифрового узла 1, выполненного на микросхемах 2, содержит блок 3 контроля, блок 4 управления, зонд 5, счетчик 6, дешифратор 7, мультиплек. сор 8, блок 9 сравнения, элемент задержки 10, и переключатели ll=l - 11=от, элементы 12=1 — 12=m индикации, элементы ИЛИ 13, образующие первый 14=1 и вторые 14=2 — 14=и блоки индикации.

Блок 4 управления содержит элемент 15 И, второй 16 и третий 17 элементы ИЛИ, дополнительный счетчик 18, первый 19, второй 20, третий 21 и четвертый 22 генераторы 45 одиночных импульсов.

Выход зонда 5 соединен с клеммой дпя подключения вывода диагностируемого цифрового узла 1, блок 3 контроля соединен первыми выходами и пер-50 выми входами соответственно с клеммами для подключения входов и выходов диагностируемого цифрового узла, первый наход блока 4 управления соединен с вторым входом блока 3 контро-55 ля и со счетным входом счетчика 6, соединенного выходами с входами дешифратора 7, установочным входЬмс вторым выходом блока 4 управления и с третьим входом блока 3 контроля, 60 соединенного вторым выходом с первым входом блока 4 управления, второй вход которого соединен с первым находом блока 9 сравнения, соединенного первым входом с выходом зонда 5, вторым находом непосредственно с третьим входом блока 4 управления, а через элемент 10 задержки - с четвертым входом блока 4 управления, соединенного третьими выходами с первыми входами мультиплексора 8, соеди ненного выходом с вторым входом блока 9 сравнения, вторыми входами — с выходами .соответствующих первых элементов ИЛИ 13, выходы дешифратора 7 соединены с входами одноименных переключателей 11=-1 - 11= а каждого иэ блоков 14=1 - 14=n индикации, выходы которых соединены с входами соответствующих элемен тов 12=1 — 12=m индикации и с соответствующими входами первого элемента 13 ИЛИ данного 1-того блока индикации 14=i .

В блоке 4 управления первый и второй входы элемента И 15 соединены с одноименными входами блока °

Выход первого генератора 19 одиночных импульсов соединен с первым входом второго элемента ИЛИ 16, соединенного соответственно вторым входом и находом с третьим входом и первым выходом блока 4, четвертый вход которого соединен с первым входом тре тьего элемента ИЛИ 17, соединенного вторым входом с выходом элемента И 15, третьим входом - с выходом второго генератора 2 0 одиночных импульсов, выходом — с вторым входом блока 4, соединенного третьими выходами с выходами дополнительного счетчика 18, первый и второй входы которого соединены с выходами третьего 21 и четвертого 22 генераторов одиночных импульсов соответственно.

Устройство работает следующим образом.

На первом этапе работы зонд 5 не подключается . При этом, на вход блока 9 с зонда 5 поступает нулевой сигнал, блок 9 всегда выдает сигнал сравнения на элемент И 15 и осуществляется контроль цифрового узла 1 с помощью блока 3 контроля и блока 4 управления.

Сигналом с генератора 19 блока 4 устанавливают блок 3 контроля в исходное состояние, затем сигналом с генератора 20 блока 4 задают первый тест, поступающий на входы контролируемого узла 1. Блок контроля 3 сравнивает информацию с выходов узла 1 с эталонной информацией и в случае равенства вырабатывает сигнал Сравнение, который поступает в блок 4 на элемент H 15 для выработки команды на задание второго теста.

Реакция контролируемого цифрового узла 1 повторно сравнивается с эталонной и по сигналу Сравнение осуществляется переход к следую1071979 щему тесту и т.д, до тех пор, пока выходная информация не сравнится с эталонной. B этом случае блок 4 не вырабатывает сигнал Сравнение и происходит остановка программы контроля на тесте, в котором впервые проявилась неисправность .

По информации контрольного теста, на котором произошел останов, определяют список подозреваемых в отказе микросхем 2. Этот список может включать несколько микросхем 2, так как обычно объем контролирующей программы цифрового узла 1 рассчитан только на обнаружение неисправностей, на не на их диагностику. 15

Для точного определения места неисправности на втором этапе работы устройства с помощью однотактного зонда 5 последовательно снимают диаграммы переключений с каждого из вы- 2П водов подозреваемых в отказе микросхем ?, запоминают их на переключателях 11 = + — 11=оп и индицируют с помощьд элементов 12. Переключатели 11=1 — 11=re каждого из блоков 14 =1 - 14 = n з апоминают со стоян и я одн ого из вы водо в ми кро схем ? на всех м словах теста. Число блоков 14=1 — 14= определяется числом выводов микросхем,, состояния кото- 30 рых необходимо запомнить.

В результате анализа сигналов на выходах подозреваемг2 микросхем 2 при соответствуюших входных воздействиях делают заключение об исправности или неиспра:ности данной микро схемы °

Запись диаграммы переключений на блоках 14=1 — 14=п индикаторов начинают с контактирования зондом 5 к первому выводу подозреваемой в отказе микросхемы 2 и подачи информации с этого вывода на первый вход блока 9 сравн ения . Блок 4 упр авлени я, з адава я с помощью ген ерато— ра 21 и счетчика 18 управляющие сигналы на мультиплексор 8 подключает второй вход блока 9 сравнения к выходу блока 14 1.В исходном состоянии переключатели 11=1 — ll=m в блоке 14=1 находятся в нулевом сос- 50 то янии, при котором соответствующие

- элементы 12 .не горят, а при приходе единичного сигнала опроса от дешифратора он на вход элемента ИЛИ 13 не проходит. Сигнал с блока 4 управле- 55 ния устанавливает блок 3 контроля и счетчик б в исходное состояние.

Сигнал с генератора 22 сбрасывает счетчик 18 в исходное состояние по сигналу запуска с блока 4 блок 3 бО задает первый тест на цифровой узел l при .этом счетчик б с помощью дешифратора 7 выбирает переключатели 11=1 всех блоков 14"-1

14 а . Блок 3 контроля вырабатывает сигнал Сравнение и задает его на первый вход элемента И 15, но разрешение на вывод следующего теста формируется в блоке 4 только в том случае, если на второй вход элемента И 15 блока 4 управления приходит сигнал Сравнение с блока 9 сравнения. Сигнал сравнения на выходе блока 9 образуется в том случае, если информация на контролируемом выводе микросхемы 2 совпадения с информацией на выбранном в данный момент переключателе 11=1 блока 14:=1 . Если логический уровень информации на выводе микросхемы 2 в первом тесте равен нулю, то на блоке 9 сравнения он сравнивается с нулевым уровнем, задаваемым переключателем 11-"1 блока 14=1, который поступает на второй вход блока 9 сравнения через элемент ИЛИ 13 блока 14=-1 и первый вход мультиплексора 8. По команде блока 4 управления осуществляется переход к второму тесту. С блока 3 контроля задается второй тест, счетчик б устанавливается в следующее состояние, в результате чего дешифратор 7 выбирает переключатель 11=2 блока 14 =1 .. Нулевой уровень переключателя 11=2 через элемент ИЛИ 13 и мультиплексор 8 пос. тупает на один из входов блока 9 сравнения, на другой вход которого поступает через зонд 5 информация с вывода микросхемы 2. Если логический уровень на выводе микросхемы 2 равен нулю, то блок 9 сравнения вырабатывает сигнал, по которому блок 4 управления осуществляет переход к третьему тесту ° Если логический уровень на выводе микросхемы 2 равен единице, то возникает сигнал Несравнение, который, поступая на элемент 16 ИЛИ в блок 4 управления, приводит блок 3 в исходное состояние, а пройдя элемент 10 задержки, через элемент ИЛИ 17 осуществляет перезапуск блока 3. Для того, чтобы устройство перешло к реализации третьего теста, необходимо установить переключатель 11=2 блока 14=1 в единичное положение, в результате чего при повтором приходе сигнала опроса от дешифратора 7 на переключатель 11=2, этот переключатель вы" дает через элемент ИЛИ 13 блока 14=1 и мультиплексор 8, единичный сигнал на блок 9 сравнения, который разрешает переход к кодам следующего теста.

По мере продвижения по тестпро-.грамме до последнего теста на переключателях 11=1 — 11=м записывается, а на элементах 12=1 - 12 m бло ка 14=1 индицируется диаграмма переключений на первом выводе микросхемы 2.

1071979

Составитель В. Дворкин

Редактор A.Øàíäîð Техред О. Неце КорректоР Г. Решетник."

Заказ 118/38 Тираж 711 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г.ужгород, ул .Проектная, 4

После этого зонд 5 переставляют на второй вывод микросхем 2, со счетчика 18 блока 4 управления включением генератора 31 задают.следую щий код для управления мультиплексором 8, который подключает один из входов блока 9 сравнения блоку 14=2, в котором осуществляется запись диаграмьн переключений второго вывода микросхем и т.д., в каждом блоке 14=1 - 14=n на переключателях 10

ll-"1 - 11=в оказывается записанной информация о состояниях каждого ив выводов микросхемы 2, которая индицируется элементами 12=1 - 12=а., 15

Оператор, занимающийся поиском неисправности по индикаторам 42=1

12=е судит о логических состояниях на выводах scex микросхем на всех словах теста и сравнения их с эталон- О ными заданными, например, таблично, определяет с использованием электрической схемы цифрового узла 1 путь поиска неисправности и отказавшую микросхему.

Таким обра.эом введение счетчика б, дешифратора 7, мультиплексора 8, элемента 10 задержки, переключателей 11=1 - 11-"tn, элементов 12= 1

12= индикации, элементов ИЛИ 13, блоков 14=1 - 14=n индикации позволяет о.существлять поиск неисправностей цифрового узла 1 без использования эталонных микросхем, что повысило достоверность диагностики и повысило быстродействие устройства из-за отсутствия необходимости замены эталонных микросхем.

В связи с тем, что в среднем половина переключателей 11=-1 — 11=ж уже перед началом работы устройства находится в состоянии соответствуюшем реальным состояниям выводов микросхем, отсутствует необходимость записи этих состояний в блоках

14=1 — 14=В, что также повышает быстродействие устройства.