Устройство для сравнения двоичных кодов

Иллюстрации

Показать всеРеферат

yctPOflCTBO ДЛЯ СРАВНЕНИЯ ДВОИЧНШ КОДОВ, содержащее блок сравнения , включанхций элемент НЕ, и блок/ формирования ре; ультатов фавнения, включаю ф(й первый элемент ИЛИ-НЕ, причем информационные входы блока сравнения соединены с шингьми первого и второго сравниваемых кодов, взюд синхронизации блока сравнения подключен к 1Ш1не синхронизащш устройства, выходы блока формирования результатов сравнения подключены к выходным ши нам Больше и Меньше устройства, входы первого элемента ИЛИ-НЕ соеда1нены.соответственно с / .первым и вторым входами блока формирования результатов сравнения, а выход - с его первым выходом, отличающееся тем, 1то, с целью повышения надежности устройства за счет обеспечения работоспособности при сравнений расфазированных кодов и их асинхронном приеме по отнсинению к сигналу синхронизации при анализе достоверности передачи информации, в блок сравнения введены элемент ИСК) ИЛИ, двоичный счетчик и дешифратор, а в блок формирования результатов сравнения - . второй элемент ИЛИ-НЕ, причем информационные входы блока сравнения соединены с входами элемента ИСК7ШЧАЩЕЕ 1ШИ, выход. которого через элемент НЕ подключен к входу установки в ноль двоичного счетчика, счетный вход которого соединен с входом синхронизации блока сравнения, выходы двоичного счетчика подключены к соЬтветствуювим входам дешифратора, § выход которого, являкяцийся выходом блока сравнения, соединен с шиной Равно устройства, .с первым входом блока сравнения, и с первыми входами первогЬ и второго элементов ИЛИ-НЕ блока фор1 гарования результатов срав- g нения, вторые входы которых подключен, ны соответственно к второму и третьему входам блока формирова1}ия результатов сравнения и к чтнам первого и второго сравниваемых кодов, а выходы - соответственно к первому И второму выходам блока формирования результатов сравнения и к шинам Меньше и Больше устройства.

СОЮЗ СОВЕТСКИХ

O9l (11}

ЗСЮ 6 06 F 7 04

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ к сстасснавм ссиаствъстст (21) 3500979/18-24 (22) 15;10.82 (.46) 07.02.84..Бюл. }} .5 .(72) В.ИсЗайцев и .В.A.Íåìêîâà (53) 681 .325.5(088.&) . (56). 1. Авторское свидетельство СССР

:9 781802, кл. 6 06 F 7/04, 1979..

2. Авторское свидетельство СССР

9 798816, кл. 6 .06 F 2/04, 1979 (прототип), (54)(57) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ

ДВОИЧНШ КОДОВ, содержащее блок сравнения, вхлючающий элемент НЕ, и блок, формирования результатов сравнения, . включающий первый элемент ИЛИ-НЕ, причем информационные входы блока сравнения соединены с шинами nepsoro и второго сравниваемых кодов, .вход синхронизации блока сравнения подключен к шине синхронизации уст- . ройства, выходы блока формирования результатов сравнения подключены к выходным шинам "Больше" и "Меньше" устройства, входы первого элемента

ИЛИ-НЕ соединены. соответственно с .первым и вторым входами блока формирования результатов сравнения, а выход †. с его первым выходом, о т— л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства эа счет обеспечения работоспо.соЪности при сравнении расфаэированных. кодов и их асинхронном приеме по отношению к сигналу синхронизации при анализе достоверности передачи информации, в блок сравнения введены элемент ИСКМЮЧИОЩЕЕ ИЛИ, двоичный счетчик и,дешифратор, а в блок формирования результатов сравнения второй элемент ИЛИ-НЕ, причем информационные входы блока сравнения соединены с. входами элемента ИСКЛЮ»

ЧМЩЕЕ ИЛИ, выход которого через элемент HE подключен к входу установки

s ноль двоичного счетчика, счетный вход которого соединен. с входом синхронизации блока сравнения, выходи двоичного счетчика подключены к соответствующим входам дешифратора, Я выход которого, являющийся выходом блока сравнения, соединен с шиной

"Равно". устройства, с первым входом блока сравнения и с первыми входами первого.и второго элементов ИЛИ-.НЕ блока формирования результатов срав- Я нения, вторые входы которых подключе йы -соответственно к второму и третьему .входам блока формирования результатов сравнения и к шинам первого и второго сравниваемых кодов, а выходы - соответственно к первому и второму выходам блока формирования результатов сравнения и к шинам

"Меньше" и "Больше" устройства.

1072038

Изобретение относится к автоматике и вычислительной технике, в частности к цифровым вычислительным машинам третьего — четвертого поколе-. ний, и предназначено для использования в устройствах ввода-вывода, мо-дулях обмена с периферийными устройствами и в контрольно-проверочной аппаратуре при анализе достоверности передачи информации с последующей ее корректировкой.

Известно устройство поразрядного сравнения кодов с выделением сигналов "Больше" и "Меньше" или "Разно", содержащее логические схемы И, ИЛИ, НЕ и др и 3 -К триггеры f1(.

Недостатком устройства янляется низкая достоверность функционирования при сравнении кодов, задержанных во времени между собой с невозможностьи синхронизации сравниваемых кодов. При наличии синхронизации на Л -К триггерах - большим количеством ложных срабатываний.

Наиболее близким к изобретению .по технической сущности является устройство для сравнения двоичных чисел, содержащее блок сравнения, включающий Э -К триггеры, элементы

ИЛИ,НЕ и блок формирования результатов сравнения на элементе ИЛИ-НЕ, причем информационные входы устройства соединены с первыми входами первого и второго 3 -К триггеров, первый информационный вход устройства через первый элемент НЕ подключен к второму входу 3 второго.З -К триггера, второй информационный вход устройства через второй элемент НЕ соединен с вторым входом 3 первого 3 -К триггера, прямой выход которого подключен к первому входу nepj вого элемента ИЛИ, выход которого соединен с входом установки в нулевое .состояние второго g -Ê триггера, прямой выход которого подключен к первому входу второго элемента ИЛИ, выход которого соединен с входом установки в нулевое состояние первого 3 -K триггера, инверсный выход которого подключен к третьему входу

3 второго 3 -К триггера, инверсный выход которого соединен с третьим 5 входом 3 первого 3;К триггера, пряьие выходы первого и второго g --K триггеров соединены с первым и вто" рым выходами устройства и с первым и вторым входами элемЕнта ИЛИ-НЕ, 5 выход которого подключен к третьей выходной шине устройства, вход синхронизации устройства соединен с входами 3 -- К триггеров,,вход начальной установки устройства подключен к вторым входам элементов ИЛИ f2) .

Однако устройство не обеспечивает непрерывную проверку всех битов кодовой информации, так как при первом же неравенстве схема блокируется и требует, для продолжения работы, обнуления. Кроме того, нарушается достоверность информации при сравнении сдвинутых между собой во времени кодов больше, чем на половину импульса битовой единицы, так как узлом сравнения вырабатываются ложные.. сигналы неравенства. Устройство неработоспособно при асинхрон. ном приеме сравниваемой расфазиро10 по отношению к импульсам синхронизации.

Целью изобретения является повышение достоверности и надежности за счет обеспечения функционирования при сдвиге кодов во времени друг относительно друга и при асинхронном приеме их по отношению к сигналу синхронизации при анализе достоверности передачи информации.

20 Поставленная цель достигается тем, что в устройстве для сравнения двоичных кодов, содержащем блок сравнення, включающий элемент НЕ, и блок формирования результатов

25 сравнения, включающий первый эле- . мент ИЛИ-НЕ, причем информационные входы блока сравнения соединены с шинами первого и второго сравниваемых кодов„ вХоЦ синхронизации блока сравнения подключен к шине синхронизации устройства, выходы блока формирования результатов сравнения подключены к выходным шинам "Больше" и "Меньше" устройства, входы первого элемента ИЛИ-НЕ соединены соответственно с первым и вторым входами ! блока формирования результатов сравнения, а выход - с его первым выхо-. дом, и блок сравнения введены элемент ИСКЛВЧЗЧЯЦЕЕ ИЛИ, двоичный счет40 чик и дешифратор, а .в блок формирования результатов сравнения - второй элемент ИЛИ-НЕ,.причем информационные входы блока сравнения соединены с входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого через элемент HE подклшчен к входу установЪи. в ноль двоичного счетчика, счетный вход которого соединен с входом синхронизации блока сравнения, выходы двоичного счетчика подключены к соответствующим входам дешифратора, выход которого, являющийся выходом блока сравнения, соединен с шиной "Равно" устройства, с первым входом блока сравнения и с первыми входами первого и второго элементов ИЛИ-НЕ блоКа формирования результатов сравнения, вторые входы которых. подключены соответственно к второму и третьему входам блока формирования результа0 тов сравнения и к шинам первого и второго сравниваемых кодов, а выходы - соответственно к первому и второМУ, выходам блока формирования результатов сравнения и к шинам

5 "Меньше" и "больше" устройства.

1072038

При поступлении на информационные входы A и В устройства кодов, сдви« нутых .между собой по фазе, т.е. с задержкой во времени, на выходе C элемента НЕ в момент несовпадения значений уровней на входах A и В присутствуют низкие уровни напряжения (вторая и третья строки на фиг. 3), а в .момент совпадениявысокие (первая и четвертая строки на фиг. 3). На выходе С элемента НЕ, соединенного с входом R счетчика 3, низкие уровни напряжений разрешают счет импульсов, поступающих на вход синхронизации устройства, а высокие обнулять счетчик, т.е. запрещать их счет. С увеличением расфазировки, т.е. задержки между собой кодов, поступающих на входы A и В, время разрешения на счет импульсов синхронизации увеличивается, а время обнуления и запрета — уменьшается (графи45

При этом оптимальный период следования импульсов синхронизации определяется длительностью импульса высокого уровня напряжения ц и временем задержки (сдвига) сравниваеР и ьнх кодов ь3 по соотношению »»„à 5 л л, í s

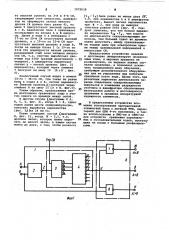

На фиг. 1 приведена блок-схема устройства для сравнения кодов; на фиг. 2 -. временная диаграмма работы устройства; на фиг. 4 - 5 таблицы истинности работы устройства.

Устройство содержит входной блок

1 сравнения с информационными входами A и В, выполненный на логиче- l5

)cKHx элемейтах ИСКЛЮЧАКЦЕЕ ИЛИ-НЕ 2, двоичном счетчике 3 и дешифраторе 4, . вход 5 синхронизации и блок 6 форми рования резулвтата сравнения, содер- жащий два элемента.ИЛИ-НЕ 7 и 8 и gQ выходные шины 9-11 °

Устройство работает следующим образом.

На вход синхронизации устройства непрерывно поступают синхронизирую- 25 щие импульсы .tCH).

При равенстве кодов при поступлении на информационные входы А и В устройства сравниваемых кодов, s фазе по отношению друг к другу, на выходе С элемента HE 2 присутствует высокий уровень напряжения, обнуляющий счетчик 3 и запрещающий счет импульсов синхронизации (на фиг.3 первая и четвертая строки, на фиг.4 последняя строка), при этом на выход 3 блока 1 и на выход 9 устрой-. ства с дешифратора 4 поступает высокий уровень напряжения, а на выхо" ды устройства 10 и 11 -,низкие. Та-. кое состояние выходов устройства 40 свидетельствует о равенстве битов кода, поступающих на информационные входы устройства. ки 1 А, В, С П А, В, Су Ш А, В С) с импульсами синхронизации 1-46.

При неравенстве бита сравниваемых кодов, на одном из входов А или В отсутствует импульс с высоким уровнем напряжения, что приводит к разрешению счета СЙ счетчиком 3 на время длительности высокого уровня

s сравниваемом бите. Период бледова ния СИ выбирается так, что за это время, разрешенного счета, на выходе

d элемента .успеет появиться низкий уровень (1 A В, С, 3 во время следования 19-22 импулЬсов CH П вЂ” 17, 24 импульсов СИ и Ш вЂ” 1 и 2 импульсов СИ на фиг. 2), при этом на выходе

9 устройства появляется импульс низкого уровня, а на одном из выходов

10 или 11 — высокий, при наличии на другом низкого.

Такое состояние выходов устройства свидетельствует о неравенстве сравниваемых битов кода. Ситуации сравнения приведены на фиг. 5. С уменьшением периода следования СИ

:увеличивается точность сравнейия .битов кода при всех времейах задержек между ними и разной длительнос- ти импульсов сравниваемых кодов; но приводит к;возрастанию оборудования.

Для конкретных времен задержек между собой и длительности импульсов сравниваемых кодов, оптимальный период следования СИ можно определить по формуле ,"LM "3 (1)

"сн -". 2 .где »ц время высокого уровня напряжения входного кода; — время задержек (сдвига) между сравниваемыми кодами.

Номер выделяемого импульса СИ дешнфратором 4 на выход с равен и (2) и -" я» |щ

При рассмотрении работы устройства в.конкретном примере, когда коды А и В поступают с длительнои стью »„ = 10 мкс .высокого уровня напряжения с задержкой кода В на 7,q

= 5 мкс (графики 1 A и В, фиг. 2) °

lIo формуле (1)» » = 2,5 мкс, а номер импульса, на который дешифра» тор выдечяет сигнал неравенств, по формупе (2) и = 4 (код равен 0100, фиг. 4) .

Сравнение значений кодов A и В происходит побитно. Для наглядности

СИ (фиг. 2) пронумерованы от 1-го до 46-го. Первые биты кодов — высокие уровни, но код В сдвинут на 3 .

Уровни во.время следования 1-го и 2-го СИ не совпадают (при A высокий, при В низкий), поэтому на выходе блока сравнения появится (фиг.2С) сигнал С с низким уровнем, за этот период счетчик отсчитает два импугьса, но на 3-й СИ уровни (оба Высокие) совпадают, поэтому сигнал С формиру-

1072038 ет высокий уровень на 3-й и 4-Й СИ, запрещающий счет импульсов, дешифратор не сформирует сигнал низкого уровня (й должно быть равно 4), на шине 9 присутствует высокий уровень

A = В. Аналогично блок 1 сравнивает последующие на входах A и В импульсы. Далее в коде A в интервале с

17-го по 20-й СИ отсутствует высокий уровень, а с 19-го по 22-й СИ присутствует высокий уровень в коде В, тогда на выходе блока 1 (c 19-го по

23-й СИ) формируется низкий уровень, разрешающий счег всех четырех импуль

cos СИ, т.е, счетчик выработает двоичный код .0100 (равный десятичному -. четырем), а дешифратор выработает сигнал d — низкий уровень (фиг. 2) неравенства, который через элемент

7 поступит на шину 10 (A с В, фиг..

5). 20

Аналогичный случай виден в момент

33-го — 36-го СИ, где также не равны биты в кодах A и В, сигнал неравенств а (низ кий, уровень Д ) поступит через элемент 8 на шину 11 (A > В. фиГ.5) .

Таккм образом, предлагаемая схема достоверно сравнивает коды C учетом сдвига во времени между собой.

В другом случае (диагравви П А, В, С, d, фиг. 2), когда И = 8, сдвиг кодов равен шести синхроимпульсам, показана выработка неравенства (фиг. 2б )на 24 Ом Си.

Также: пг>иведен случай (диаграМы

Ш, фиг. 2}, когда Н =. 2,5, т.е. дробное число, которое нужно округлить до целого числа, в нашем случае можно до двух, с тем, чтобы разность (К - 4q) была равна не менее двух СИ, т.е. при неравенстве А и В дешифратор сработает, выдаст сигнал неравенства при Ц = 2, при коде.на выходах счетчика равном 0010 (Фиг. 3) . Следует заметить., что чем больше выражено неравенство egg «7 <, чем короче по длительности синхронизирующие импульсы, тем больший сдвиг. во времени можно допустить, между, сравниваемыми кодами даже при асинхронном приеме между сравниваемой информацией и импульсами СИ.

Предлагаемое устройство надежно и достоверно синхронизкрует сравниваемые коды, в широких пределах их расфазировки., не вйдавая ложных сигналов сравнения, к йоэволяет исклю" чнть традиционную -шину. обнуления, требующую дополнительного оборудования для ее управления прк обитномсравнении всего кода. Кроме того, при различных вариантах длительности периода следования синхрокизирующих импульсов и изменении разрядности счетчика и дешифратора обеспечивает безотказную работу к достоверность сравнения в пределах аппаратурной надежности элементов.

В предлагаемом устройстве возможно использование прогрессивкой элементной базы с логикой ТТЛ, характерной для ЦВИ 4-ro поколения, а также использование в ВИС-ах и СВИС-ах для устройств:: сравнения параллельных и.последовательных кодов, поступающих иа входы с большими расфазировками °

1072038

1072038

Составитель E. Иванова

Редактор Н. Бобкова ТехредМ.Гергель Корректор и. Шароши

Заказ 127/41 Тираж 699 Подписное . ВНИИПИ Государственного комитета СССР по длеам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4