Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

АНАЛОГОВОЕ ЗАПОМИНАЩЕЕ УСТРОЙСТВО, содержащее первый и второй накопительные элементы на первом и втором конденсаторах, одни обкладки которых соединены с шиной нулевого потенциала, другие-обкладки - с неинвертирующими входами первого и второго операционных усилителей соответственно, инвертирующие входы которых подключены к выходам соответственно первого и второго ком мутаторов ,первые входы которых объединены и являются входом устройства, вторые входы объединены и являются выходом устройства, выходы первого н и второго операционных усилителей подключены соответственно к первому и второму входам третьего коммутатора , третий операционный усилитель, выход которого соединен с выходом четвертого коммутатора, первый и второй входы которого подключены к неинвертирующим входам соответственно первого и второго операционных усилителей , и резистивный делитель напряжения ,:Отличающееся тем, что, с целью повышения его. быстродействия в него введен пятый коммутатор, первый и второй входы которого подключены к выходам соответственно первого и второго операционных усилителей., а выход - к второму § входу первого коладутатора, первый (Л вход которого соединен с неинвертирующим входом третьего операционного усилителя, инвертирующий вход которого соединен со средней точкой резистивного делителя напряжения, первый S и второй входы которого подключены соответственно к выходу третьего коммутатора и выходу третьего операционного усилителя. - IND

СОЮЗ СОВЕТСНИХ, СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

3(51) ОПИСАНИЕ ИЗОБРЕТ

К А8 ГОРСКОМУ СВИДЕТЕЛЬСТ8У

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

i (21)3437775/18-24 (22 214 ° 05 -83 (46)07.02.84. Бюл. Р 5 (7 2 ) О. С. Андреев, И. Б. Мелихов, О.Л. Николайчук и P.3. Шентебань (53)681.327.66(088.8) (56)1 . Патент США Р 4066919, кл..307/353, опублик. 1978.

2 ° Авторское свидетельство СССР

Р 760191, кл. G .11 С 27/00, 1978 (прототип).

I (54)(57) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ

УСТРОЙСТВО, содержащее первый и второй накопительные элементы на первом и втором конденсаторах, одни обкладки которых соединены с шиной нулевого потенциала, другие.обкладки — с неинвертирующими входами перaoro и второго операционных усилителей соответственно, инвертирующие входы которых подключены к выходам соответственно первого и второго ком, мутаторов, первые входы которых объединены и являются входом устройства, вторые входы объединены и являются выходом устройства, выходы первого

„„SU„„1072101 A и второго операционных усилителей подключены соответственно к первому и второму входам третьего коммутатора, третий операционный усилитель, выход которого соединен с выходом четвертого коммутатора, первый и второй входы которого подключенй к неинвертирующим входам соответственно первого и второго операционных усилителей, и резистивный делитель напряжения,.о т л и ч а ю щ е е с я тем, что, с целью повышения его быстродействия в него введен пятый коммутатор, первый и второй входы которого подключены к выходам соответ- * ственно первого и второго операционных усилителей., а выход — к второму @

12 входу первого коммутатора, первый вход которого соединен с неинвертирующим входом третьего операционного усилителя, иивертирующии вход котОрого соединен со средней точкой реэистивного делителя напряжения, первый Я и второй входы которого подключены соответственно к выходу третьего коммутатора и выходу третьего операционного усилителя. 4Р

1072101 точка которого подключена к вторым входам первого и второго коммутаторов.

Напряжение смещения нуля используемых в устройстве операционных усилителей компенсируется и не влияет на точность устройства (23 .

Недостатком устройства является низкое быстродействие, вызванное тем, что при каждом переключении коммутаторов выходное напряжение первого и второго операционных усилителей изменяется от значения входного напряжения до нуля или наоборот.

При э том на установление напряжения на выходе устройства с заданной точностью затрачивается значительное время.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее первый и второй накопительные элементы на первом и втором конденсаторах, одни обкладки которых соединены с шиной нулевого потенциала, другие обкладки — с неинвертирующими входами первого и второго операционных усилителей соответственно, инвертирующие входы которых подключены к выходам соответственно первого и второго коммутаторов, первые входы которых объединены и являются входом устройства, вторые входы объединены и являются выходом устройства, выходы первого и второго операционных усилителей подключены соответственно к первому и второму входам третьего коммутатора, третий операционный усилитель, выход которого соединен с выходом четвертого коммутатора, первый и второй входы которого подключены к неинвертирующим входам соответственно первого и второго операционных усилителей, и резистивный делитель напряжения, введен пятый коммутатор, первый и второй входы которого подключены к выходам соответственно первого и второго операционных усилителей, а выход— к второму входу первого коммутатора, первый вход которого соединен с неинвертирующим входом третьего операционного усилителя, инвертирующий вход которого соединен со среднейточкой резистивного делителя напряжения, первый и второй входы которого подключены соответственно к выходу третьего коммутатора и выходу третьего операционного усилителя.

Изобретение относится к вычислительной технике и предназначено для использования в аналого-цифровых преобразователях.

Известно аналоговое запоминающее устройство, содержащее два идентич- 5 ных запоминающих элемента, подключаемых к.входу и выходу устройства поочередно. Каждый из запоминающих элементов содержит первый усилитель, выход которого соединен с одной об- 10 кладкой конденсатора, другая обкладка которого соединена с входом второго усилителя, выход которого через ключи связан с собственным входом и входом первого усилителя (1) .

Недостатком известного устройства является низкие быстродействие и точность, обусловленные тем, что при переключении каждого из запоминающих элементов в режим хранения, напряжение -на его выходе изменяется от нулевого значения до значения запомненного напряжения. В режиме хранения цепью обратной связи охватываются два последовательно включенных усилителя запоминающего элемента. Это приводит к значительному переходному процессу и затягиванию времени установления выходного напряжения, что снижает быстродействие устройства. Кроме того, наличие ключей, не охваченных цепью стабилизирующей обратной связи, между выходом устройства и выходами запоминающих элементов приводит к появлению дополнительной погрешности в вы- 35 ходном сигнале.

Наиболее близким по технической сущности к предлагаемому является аналоговое запоминающее устройство, содержащее первый и второй накопи- 4р тельные элементы на первом и втором конденсаторах, одни обкладки которых соединены с шиной нулевого потенциала, другие обкладки — с неинвертирующими входами первого и второго 45 операционных усилителей соответственно, инвертирующие входы которых подключены к выходам соответственно первого и второго коммутатора, первые входы которых объединены и являются входом устройства, вторые входы объединены и являются выходом устройства, выходы первого и второго операционных усилителей подключены соответ ственно к первому и второму входу третьего коммутатора, выход которого со. 55 единен с входом инвертирующего усилителя на третьем операционном усилителе, выход которого соединен с выходом четвертого коммутатора, первый и второй входы которого подключены к инвер- 60 тирующим входам соответственно первого и второго операционных усилителей выходы которых соединены соответственно с первым и вторым входами резистив. ного делителя напряжения, средняя

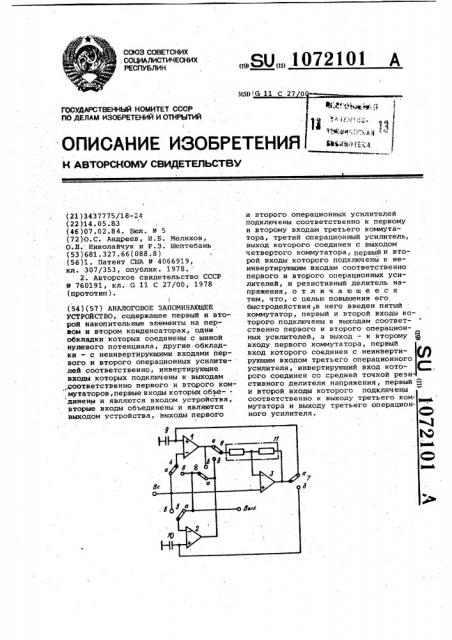

На чертеже представлена схема предлагаемого устройства.

Устройство содержит операционные усилители 1-3, коммутаторы 4-8, кондеисаторы 9 и 10, и резистивный делитель 11 напряжения.

Устройство работает следующим образом.

1072101

Составитель Н. Дикарев

Техред 0 Неце

Корректор В. Бутяга

Редактор С. Юско

Заказ 134/44 Тираж 575

ВНИИПИ Государственного комитета СССР по делаМ изобретений и открытИй

113035, Москва, K-35, Раушская наб., д; 4/5

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 коммутаторы 4-8 одновременно переключаются из положения О в положение Б и наоборот. При указанном на чертеже положении коммутаторов напряжение на входе устройства будет записано на конденсатор 9. При 5 этом на выходе первого операционного усилителя 1 установится напря- жение, равное входному, поскольку только в этом случае разность напряжений, приложенных между инвертирующим и неинвертирующим входами в каждом из операционных усилителей

1 и 3, близка к нулю. Напряжение на выходе устройства в это время равно напряжению, сохраняемому вторым конденсатором 10 и передаваемому на выход устройства вторым операционным усилителем 2, охваченным обратной связью через коммутаторы 5 и 8.

При переключении коммутаторов в положение б первый 1 и второй 2 операционные усилители по выполняемым функциям меняются местами. Напряжение на выходе устройства становится равным выходному напряжению первого операционного. усилителя 1, т.е. сохраняющему на первом конденсаторе 9 тому значению напряжения на входе устройства, которое оно имело в момент переключения ключей.

Текущее значение входного напряжения отслеживается на выходах второго 2 и третьего 3 операционных усилителей и на втором конденсаторе 10. 35

Устройство характеризуется компенсацией напряжения смещения нуля используемых операционных усилите- . лей. Однако при переключении коммутаторов напряжение на выходе усили- теля, подключенного к выходу устройства изменяется лишь на величину, обуслОвленную напряжением смещения нуля усилителя и падением напряжения на коммутаторе 8, через который протекает ток на выход устройства. Полученный перепад напряжения не превышает нескольких десятков милливольт, и время, необходимое для установления выходного напряжения, не превышает де-сятков наносекунд. В известных устройствах выходное напряжение усилителей изменяется на величину равную выходному напряжению — 5-10 В. При этом время установления напряжения иа выходе устройства составляет несколько микросекунд.

Аналоговое запоминающее устройство, выполненное на микросхемах К544УД1А и К590КН4 по предлагаемой схеме, позволяет АцП с временем преобразования 5 мкс обрабатывать сигнал с амплитудой 5 В и частотой до 100 кГц.

При этом время установления выходного напряжения устройства составляет 100 нс, а период переключения ключей — 5 мкс. Устройство, построенное по схеме прототипа на аналогичных микросхемах, имеет время установления 3 мкс, что с учетом времени, необходимого для обработки сигнала, ограничивает частоту обрабатываемых сигналов на уровне 63 кГц. Получен- ный выигрыш по быстродействию приведет к значительному экономическому эффекту.