Преобразователь напряжения в десятичный код

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPGHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ б (21)3421447/18-21 (,22)07.04.82 (46)07.02.84. Бюл. В 5 (72)A.T. Пешков и A.H. Твердохлеб (71 )Минский радиотехнический институт (53)681.325(088.8) (56)1. Гитис Э.И. Преобразователи информации для электронных цифровых; вычислительных устройств. М., "Энергия"., 1975, с. 309, рис. 2-2.

2.Авторское свидетельство СССР

Р 330538, кл. H 03 К 13/17., 1972.

3. Шляндин В.M. Цифровые измери-. тельные преобразователи и приборы.

"Высшая школа", 1973, с. 213 (прототип). (54)(.57) ПРЕОБРАЗОВАТЕЛЬ HAHPHKEHHH

В ДЕСЯТИЧНЫЙ КОД,,содержащий блок сравнения йапряже(ний, первый вход ,которого подключен к входной шине, .выход — к первому входу логического блока, второй вХод которого подключен к выходу тактового. генератора, а первые выходы каждой пары выходов соединены с входами установки единицы,. соответствующего разряда регистра .двойчно-десятичного кода, вторые вы ходы каждой пары выходов - с входами. установки нуля соответствующего разряда регистра двоично-.десятичного кода, выходы которого соединены соответственно с входами преобразователя двоично-десятичного кода в напряжение, отличающийся тем, что, с целью повышения быстродействия преобразования, в него введены генератор линейного напряжения, преобразователь кода и блок суммирования напряжений, первый вход которого подключен к выходу преобразователя двоично-десятичного кода в.напряжение, второй вход — к выходу генератора линейного напряжения, а выход — к второму входу блока сравнения напряже". pg ний, при этом первые выходы первой х(а -3) сар валоров логиеесхого Оло- (/) ка подключены соответственно к первому и второму входам генератора линейного напряжения, причем выходы регистра двоично-десятичного кода подключены к первым входам преобразователя кода, к второму входу ко.торого подключен второй выход и -й, пары выходов логического блока.

1072260

Изобретение относится к измери-" тельной и вычислительной технике и используется для ввода аналоговой информации в цифровую вычисли тельную машину.

Известен преобразователь аналоговых величин в код методом разрядного уравновешивания,,содержащий схему. сравнения, первый вход которой соединен с источником преобразуемого напряжения, а второй — с выходом преобразователя кода в напряжение, вход которого подключен через регистр к выходу логического блока, управляющий вход которого соединен с первым выходом схемы сравнения, 15 а входы — с выходами распределителя импуль сов $1(., Недостатком данного устройства является малое быстродействие преобразования. 20

Известен также преобразователь напряжения в код, содержащий тактовый генератор, логический блок„ регистр кода с цепями переноса, входами установки и сброса единиц в разрядах и входами прибавления единиц в старшие разряды, первый преобразователь кода в напряжение, схему суммирования двух напряжений, распределитель импульсов, имеющий основ-.30 ные выходы по числу разрядов определяемого двоичного кода и дополнительные выходы, второй преобразователь кода в напряжение, причем выход тактового генератора подключен к входу распределителя, основные выходы кото.рого через логический блок подключе- ны к входам установки и сброса соответствующих разрядов регистра кода, а его дополнительные выходы подключены к соответствующим входам второ- 40 го преобразователя кода в напряжение и через логический блок соединены с входами прибавления единицы соответствующих разрядов регистра кода, выходы которого подключены к соот- 45 ветствующим входам первого преобразователя кода в напряжение, выход которого присоединен к первому входу схемы суммирования двух напряжений, к второму входу которой присоединен 50 выход второго преобразователя кода в напряжение, ee выход связан с первым входом схемы сравнения, к второму входу которой подключен источник преобразуемого напряжения, 55 а выход схемы сравнения подключен к входу управления логического блока P3..

Недостаток указанного устройства обусловлен низким быстродействием 6 преобразования динамической погрешности.

Наиболее близкий к изобретению .по технической сущности преобразователь напряжения в десятичный код

/ содержит блок сравнения напряжений, первый вход которого подключен к входной шине, выход — к первому входу логического блока, второй вход которого подключен к выходу тактового генератора, а первые выходы каждой пары выходов соединены с входами установки единицы соответствующего разряда регистра двоично-десятичного кода, вторые выходы каждой пары выходов — с входами установки нуля соответствующего разряда регистра двоично-десятичного кода, выходы которого соединены соответственно с входами преобразователя двоично-десятичного кода в напряжение (3) .

Недостатком известного устройства является. низкое быстродействие преобразования.

Цель изобретенИя — повышение быстродействия преобразования.

Поставленная цель достигается тем, что в преобразователь напряжения в десятичный код, содержащий блок сравнения напряжений, первый вход которого подключен к входной шине, выход — к первому входу логического блока, второй вход которого подключен. к выходу тактового генератора, а первые выходы каждой пары выходов соединены с входами установки единицы соответствую- щего разряда регистра двоично-десятичного кода, вторые выходы каждой пары выходов — с входами установки нуля соответствующего разряда регистра двоично-десятичного кода, выходы которого соединены соответственно с входами преобразователя двоично-десятичного кода в напряжение, введены генератор линейного напряжения, преобразователь кода и блок суммирования напряжений, первый вход которого подключен к выходу.преобразователя двоично-десятичного кода в напряжение, второй вход — к выходу генератора линейного напряжения, а выход — к второму входу блока сравнения напряжений, при этом первые выходы первой и (-3) пар выходов логического блока подключены соответственно к первому и второму входам генератора линейного напряжения, причем выходы регистра двоично-десятичного кода подключены к первым входам преобразователя кода, к второму входу которого подключен второй выход и -й пары выходов логического блока.

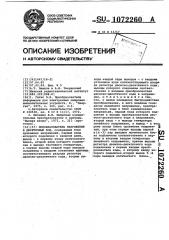

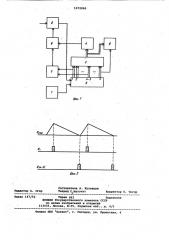

На фиг. 1 приведена структурная схема преобразователя напряжения в десятичный код, на фиг. 2 — диаграммы, поясняющие его работу.

Преобразователь содержит тактовый генератор 1, логический блок 2, регистр 3 двоично-десятичного кода, преобразователь 4 двоично-десятичного кода в напряжение, блок 5

1072260 сравнения напряжений, блок б.суммирования напряжений, генератор 7 линейндго напряжения и преобразователь

8 кода.

Первые выходы каждой пары выходов логического блока 2, к первому входу управления которого подключен логический выход блока 5 сравнения напряжения, а к второму входу присоединен выход тактового генератора 1, подключенный к входам установки единицы соответствуюцих двоичных разрядов регистра 3 двоично-десятичного кода, к входам установки нуля которого присоединены - вторые выходы этих же пар выходов логичес- 15 кого блока 2, выходы регистра.3 двоично-десятичного кода подключены соответственно к первым входам преобразователя 8 кода, к вторым входам которого подключен второй выход по следней пары выходов логического бло-. ка 2. Выход преобразователя 4 двоично-десятичного кода в напряжение присоединен к первому входу блока 6 суммирования напряжений, выход кото- 25 рого подключен к второму входу блока

5 сравнения, к первому входу которого подключены входная шина. Ко второму входу блока б суммирования присоединен выход генератора 7 линейного напряжения, к первому и второму входам которого присоединены соответственно первые выходы первой и п -33-й.пар выходов логического блока.

В исходном состоянии в регистре

3 двоично-десятичного кода зафиксированы нулевые значения во всех разрядах, компенсирующее напряжение 0» на выходе преобразователя 4двоично-десятичного кода в напряжение равно нулю.

49

Формирование. двоично-десятичного кода в предлагаемом преобразователе осуцествляется в два этапа.

На первом .этапе имеется кодовый эквивалент входного напряжения, на 45 втором осуществляется преобразование найденного кода в двоично-десятичный.

На первом этапе выполняется tl тактов по числу двоичных разрядов реги- 50

-стра 3 двоично-десятичного кода.

Каждый такт выполняется по очеред-.-. ному сигналу с тактового генератора.1.

Действия на каждом такте однотипны.

В начале каждого i --го такта появля-. 55 ется сигнал на первом выходе -й пары выходов логического блока 2, который поступает на вход установки единицы в -м разряде регистра 3 двоично-десятичного кода. Сформированное. 6р на выходе преобразователя 4 двоичнодесятичного кода в напряжение компен- . сйрующее напряжение О» через блок 6 суммирования напряжений поступает на вход блока 5 сравнения и сравнивается с текущим значением входного напряжения 0„ . Если U» > Uq, то в конце текущего такта появляется сигнал на втором выходе -й пары выходов логи, ческого блока 2 и устанавливает нуле° вое значение в g -м разряде регистра

3 двоично-десятичного кода. Кроме того, по сигналу с первого. выхода первой пары выходов логического бло-. ка 2 генератор 7 линейного напряжения начинает формировать на своем выходе линейно убывающее напряжение одного знака с компенсирующим напряжением на выходе 0 » . Напряжение с выхода генератора 7 линейного напряжения достигает нулевого значения по поступлении на второй вход генератора

7 сигнала с первого выхода (и -3j-й пары выходов логического блока. Генератор 7 линейного напряжения предназначен для формирования смещения

Ц», имеюцегося на выходе преобразователя двоично-десятичного кода, с тем, чтобы общая динамическая погрешность напряжения О», поступаюцего на сравнение в блок 5 сравнения напряжений в процессе определения всех старших разрядов регистра кеда, кроме четырех младших разрядов, была бы всегда одного знака, что обеспечивается суммированием напряжений с, выходов преобразователя 4 двоично-десятичного кода в напряжение и генератора 7 линейного напряжения и использованием суммарного напряжения общего компенсирующего напряжения, подаваемого на второй вход блока 5 сравнения напряжений.

На втором этапе по сигналу с второго выхода последней пары выходов логического блока ссуществляется .передача кода из регистра 3 в преобразователь 8 кода и преобразование его в двоично-десятичный код системы 8, 4, 2, 1.

Таким образом, по сравнению с базовым объектом, в качестве которого принят прототип, предлагаемый преобразователь обладает большим быстродействием. Кроме того, использование смещения компенсируюцего сигнала и избыточности кода 8, 4, 2, 1 позволяет в значительной степени устранить влияние динамической погрешности на точность нахождения кодового эквивалента входного преобразуемого напряжения, в результате .снижается необходимая длительность тактов уравновешивания старших разрядов, что, в свою очередь, при аналогичйой точности дает возможность более чем в два раза повысить скорость преобразования напряжения в код.

1072260

I I . I юг. 2

Составителв A. Кузнецов

Тенред Т.Маточка . °

Редактор А. Огар

Корректор О. Тигор

Тираж 862 Подписное

BHHHGH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Рауыская наб., д. 4/5

Заказ 147/52

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4