Устройство для временного компандирования

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ВРЕМЕННОГО КОМПАНДИРОВАНИЯ, содержащее последовательно соединенные блок управл яемой задержки, блок фазовой. автоподстройки частоты, передатчик, первый регистр; блок памяти, выходы которого соединены с входами второго и третьего регистров, управляющие входы которых объединены, последовательно соединенные первый делитель частоты и блок перебора адресов записи , выход которого сЬединен с первым входом первого элемента И, последовательно соединенные второй делитель частоты и блок nepedqpai адресов считывания, выход которого соединен с первым входом второго элемента . И, причем инверсный выход второго делителя частоты через третий ,элемент И соединен с вторым входом ; второго элемента И. и с входом считывания блока памяти, выходы первого и второго элементов И через элемент .ИЛИ соединены с управлякхцим входом блока памяти,синхронизирующие входы первого делителя частоты и блока перебора адресов записи соединены собой, синхронизирующие входы второго делителя частоты и блока перебора адресов счишвания соединены между собой, а также четвертый элемент И, о.тличающееся тем, что, с целью повышения пропускной способности, в него введены два элемента запрета и пятый элемент И, причем пер)Ый элемент запрета включен между тактовым выводом пе редатS чика и входом первого делителя частоты , управляюодай вход первого элемерта запрета соединен с входом Огибающая пропусков низкочастотной информации устройства, второй элемент запрета включен между выходом четвертого элемента И и управляющими входами второго и третьего регистров, которые также соединены с входом второго делителя частоты, вькод которого через пятый элемент D ч И соединен с входом запись блока .памяти , а второй вход пятого элемента И соединен с инверсным выходом riepSD 0 вого делителя частоты. ;о

COOS СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) (11)

З(51) Н 04 д 3 16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3341721/18-09 (22) 25 ° 09 ° 81 (46) 07.02.84. Бюл. 9 5 (72) А.А ° Калинцев, О.С.Тихонов, В.И.Устюжанин и В.В.Шавров (53). 621 . 396. 41 (088 ° 8). (56) 1. Патент СИИ Р 3778795, кл. 325-2, 1973 °

2. Авторское свидетельство СССР

Р 930714, кл, Н. 04 J 3/16, 1980 (прототип) . (54) (57) УСТРОЙСТВО ДЛЯ ВРЕМЕННОГО

КОМНАНДИРОВАНИЯ, содержащее последовательно соединенные блок управляемой задержки, блок фазовой ». автоподстройки частоты, передатчик, .первый регистр, блок памяти, выходы которого соединены с входами второго и третьего регистров, Управляющие входы которых объединены, последовательно соединенные первый делительчастоты и блок перебора. адресов записи, выход которого соединен с первым входом первого элемента И, последовательно соединенные второй делитель частоты и блок .пеРебора адресов считывания, выход которого соединен с первыМ входом второго элемента. И, причем инверсный выход второго делителя частоты через третий ,элемент И соединен с вторым вхс)пом. второго элемента И. и с входом считы- вания блока памяти, выходы первого и второго элементов И через элемент

- .ИЛИ соединены с управляющим входом блока памяти, синхронизирующие входы первого делителя частоты и блока перебора адресов записи соединены между собой, синхронизирующие входы второго делителя частоты и блока перебора адресов считывания соединены между собой, а также четвертый элемент И, о .т л и ч а ю щ е е с я тем, что, с целью повышения пропускной способности, в него введены два элемента запрета и пятый элемент И, причем первый элемент запрета включен между тактовым выходом передат- I чика и входом первого делителя частоты, управляющий вход первого элемента запрета соединен с входом Огибающая пропусков низкочастотной информации" устройства, второй элемент запрета включен между выхо- Я дом четвертого элемента И и управляющими входами второго и третьего регистров, которые также соединены с вхопом второго делителя частоты, выход которого через пятый элемент

И соединен с входом запись блока,памяти, а второй вход пятого элемента

И соединен с инверсным выходом depного делителя частоты.

1072279 диненные первый делитель частоты и блок перебора адресов записи, выход которого соединен с первым .входом первого элемента И, последовательно соединенные второй делитель частоты и блок перебора адресов считыва- ния, выход которого соединен с первым входом второго элемента И, причем инверсный выход второго делителя частоты через третий элемент И соеди10 нен с вторым входом второго элемента

И и с входом считывания блока памяти, выходы первого и второго элементов И через элемент ИЛИ соединены с управляющим входом блока памяти, синхрони15 зирующие входы первого делителя частоты и блока перебора адресов записи соединены между собой, синхронизирующие входы второго делителя частоты и блока перебора адресов считывания соединены между собой, а также четвертый элемент И, введены два элемента запрета и пятый элемент Й, причем первый элемент запрета включен ! между тактовым выходом передатчика я входом первого делителя частоты, управляющий вход первого элемента запрета соединен с входом Огибающая пропусков низкочастотиой информации устройства, второй элемент запрета включен между выходом четвертого элемента И и управляющими входами второго и третьего регистров, которые также соединены с входом второго делителя частоты, выход которого через пятый элемент И соеди35 нен с входом запись блока памяти, а второй вход пятого элемента И соединен с инверсным выходом первого делителя частоты.

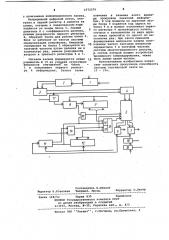

На чертеже приведена структурная

40 электрическая схема предлагаемого устройства.

Устройство содержит блок 1 управляемой задержки, блок 2 фазовой автоподстройки частоты, передатчик,З, первый регистр 4, блок 5 памяти, второй регистр 6, третий регистр 7, первый ..делитель 8 частоты, блок 9 перебора адресов записи, первый элемент И 10, второй делитель 11 частоты, блок 12. перебора адресов считывания, второй элемент И 13,,третий элемент И 14, элемент ИЛИ 15, четвертый элемент И 16, первый элемент 17 запрета, второй элемент 18 запрета, пятый элемент И 19.

Устройство работает следующим образом.

На вход блока 1 поступают импульсы с цикловой частотой передачи, на управляющий вход данйого блока посту60

Изобретение относится к радиотехнике и связи и может быть использовано в системах передачи информации с временным разделением каналов, в частности в спутниковых системах связи с многостанционным доступом в стволе ретранслятора.

Известно устройство для временного компандирования, содержащее параллельно соединенные динамические сдвигающие регистры, блрк управления записью и источник информации, выходы которого соединены с входами динамических сдвигающих регистров (1) .

Недостатком данного устройства для временного компандирования является низкая пропускная способность.

Наиболее близким к предлагаемому является устройство для временного компандирования, содержащее последовательно соединенные блок управляемой задержки, блок фазовой автоподстройки частоты, передатчик, первый регйстр, блок памяти, выходы которого соединены .с входами второго и третьего регистров, управляющие входы которых объединены, последовательно соединенные первый делитель частоты и блок перебора адресов записи, выход которого соединен с первым входом первого элемента И, последовательно соединенные второй делитель частоты и блок перебора адресов считывания,.выход которого соединен с первым входом второго элемента И, причем инверсный выход второго делителя частоты через третий элемент И соединен с вторым входом второго элемента И и с входом считывания блока памяти, выходы первого и второго элементов И через элемент ИЛИ соединены с управляющим входом блока памяти, синхронизирующие входы первого делителя частоты и блока перебора адресов записи соединены между собой, синхронизирующие входы второго делителя частоты и блока перебора адресов считывания соединены между собой, а также четвертый элемент И (2 .

Недостатком известного устройства для временного компандирования является низкая пропускная способность из-за наличия жесткой связи между сигналами считывания и записи в блоке памяти.

Цель изобретения — и вышение пропускной способности.

Поставленная цель достигается тем, что в устройство для временного компандирования, содержащее последовательно соединенные блок управляемой задержки, блок фазовой автоподстройки частоты, передатчик, первый регистр, блок памяти, выходы которого соединены с входами второго и третье го регИстров, управляющие входы кото рых объединейы, последовательно сое пает огибающая информационного пакета. С выхода блока 1 сигнал формы меандр поступает на блок 2, фаза которого совпадает с фазой цикла накопления. Таким образом, окончание цикла накопления совпадает по фазе.1072279

Составитель В.Шевцов

Вэдактор Н.Ковалева ТехредЛ. Микеш Корректор О.Тигор

Заказ 148/52 Тираж á35 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r.Óæãîðîä, ул.Проектная, 4 с окончанием информационного пакета.

Непрерывный цифровой поток, поступая в первый регистр 4 делится на слова, которые в параллельном коде подаются на входы блока 5. Первый делитель 8 с коэффициентом деления,. равным разрядности первого регистра

4, образуют такты для работы блока 9.

Блок 12 работает от тактов системы синхронизации устройства. Импульсы считывания из блока 5 образуются из гактовой частоты путем деления ее в количество раз, равное разрядности второго и третьего регистров 6. и 7. !

Сигналы записи формируются пятым элементом И 19. из условия отсутствия ймпульсов считывания иэ блока

5 и заполнения первого регистра 4 информацией. Запись также возможна в течение всего време;ни пропусков пакетной информации. В эти моменты на адресные входы блока 5 подается код адреса из блока 9 и в момент заполнения первого регистра 4 производится запись, которая в зависимости от вида адреса может произойти от одного дб нескольких ран. При таком принципе формирования импульсов записи соотношение частот тактовых импульсов передатчика 3 и тактовой, частоты системы многостанционного доступа, в состав которой входит устройство временного компандирования, может быть любым целым числом.

Использование изобретения позволяет увеличить пропускную способность .системы спутниковой связи на

10 — 15% .