Двусторонний ограничитель

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕ(МИХ

РЕСПУБЛИН (19) (ill

3(59 G 0 6 0 7 25

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTQPCH0MV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3511515/18-24 (22) 19.11.82 (.46) 15,02.84. Бюл. Р 6 (72) В.И.Анисимов и Е.A.Ëoñåâ (53) 681.335 (088. 8) (561 1. Патент CIIIA Р 3514635, кл. 307-237, опублик ° 1970

2. Корн Г., Корн Т, Электронные аналоговые и аналого-цифровые вычислительные машины.Ч.If.,М.,"Мир",.

1968, с. 9, фиг. 9-4 прототип). (54) (57) 1. )IBVCTOPOHHHA

ТЕЛЬ, содержащий операционйый усилитель, вход которого через первый масштабный резистор соединен с информационным входом и через второй масштабный резистор с выходом дву- . стороннего ограничителя, нагрузочный резистор, включенный между выходом двустороннего ограничителя и шиной нулевого потенциала, и .источники опорных напряжений, о т л ич а ю шийся тем, что, с целью расширения диапазона изменения уровня ограничения, в него введены два блока выбора минимального сигнала и инвертор, вход которого является управляющим входом двустороннего ограничителя и соединен с первым входом первого блока выбора минимального сигнала, выход инвертора подключен к первому входу второго блока выбора минимального сигнала, вторые входы блоков выбора минимального сигнала соединены с выходом операционного усилителя, выходы подключены к выходу двустороннего ограничителя, а установочные входы — к источникам опорных напряжений °

2. Двусторонний ограничитель по и. 1, отличающийся тем, что, блок выбора минимального сигнала содержит три ветви, соединенные параллельно, каждая из которых состоит из двух последовательно включенных коммутирующих дирдов, причем

Я общий вывод коммутирующих диодов первой ветви является вторым входом, общий вывод коммутирующих диодов вто С рой ветви †перв входом, а общий вывод коммутирующих диодов третьей ветви — выходом блока. выбора минимального сигнала, общие выводы ветвей соединены соответственно с первыми выводами балансных резисторов, вторые выводы которых являются установочными входами блока выбора минимального сигнала.

1073782

Изобретение относится к области вычислительной техники и может быть использовано в автоматических системах управления различного назначения в качестве управляемого прецизионного ограничителя напряжения. 5

Известен ограничитель, содержащий прецизионный диод, однополярный ограничитель напряжения, ограничительный и нагруэочный резисторы, причем прецизионный диод выполнен íà 30 одном операционном усилителе в мас штабном режиме включения и диоде, включенном в соответствующем направлении между выходом операционного усилителя и выходом устрой- 5 ства f1J .

Однако известный ограничитель не позволяет формировать ограничение входного сигнала в обеих полярностях без предварительного изменения полярности питающих напряжений и способа включения диодов; кроме того, выходная характеристика ограничителя имеет только один однополярный уровень ограничения, определяемый заранее выбранными парамет— рами устройства; уровень ограничения зависит от номинала нагрузочного ,резистора.

Наиболее близким по технической сущности к предложенному является 30 двусторонний ограничитель, содержащий операционный усилитель в масштабном режиме включения, диодный мост с двумя балансными резисторами, включенными между вершинами 35 однонаправленной диагонали диодного моста и клеммами положительной и отрицательной полярности источника питания, фиксирующие стабилитроны в цепи обратной связи операционного 40 усилителя и нагрузочный резистор, включенный между выходом устройства и нулевой шиной источника питания (2).

Недостатком данного ограничителя является то, что выходная характеристика имеет только два раэнополярных уровня ограничения, определяемых заранее выбранными параметрами устройства; уровень ограничения зависит от номинала нагрузочного резистора. 50

Цель изобретения — расширение диапазона изменения уровня ограничения.

Поставленная цель достигается тем, что в двусторонний ограничитель напряжения, содержащий операционный усилитель, вход которого через первый масштабный резистор соединен с информационным входом и через второй масштабный резистор а выходом двустороннего ограничителя, нагрузочный резистор, включенный между выходом двустороннего ограничителя и шиной нулевого потенциала„ и источники опорных напряжений, введены два блока выбора минимального сигнала и инвертор, вход которого является управляющим входом двустороннего ограничителя и соединен с первым входом первого блока выбора минимального сигнала, выход инвертора подключен к первому входу второго блока выбора минимального сигнала, вторые входы блоков выбора минимального сигнала соединень. с выходом операционного усилителя, выходы подключены к выходу двустороннего ограничителя, а установочные входы — к источникам опорных напряжений.

Блок выбора минимального сигнала содержит три ветви, соединенные параллельно„ каждая иэ которых состоит иэ двух последовательно включенных коммутирующих диодов, причем общий вывоц коммутирующих диодов первой ветви является вторы : вх,ov., общий вывод коммутирующих диодов второй ветви — первым входом, à =:бщий вывод коммутирующих диодов zpeтьей B-:". í. . — выходом блока выбора минимального сигнала, общие выводы ветвей соединены соответственно с первыми выводами балансных резисторов, вторые выводы которых являются установочными входами блока выбора мини --.льного сигнала.

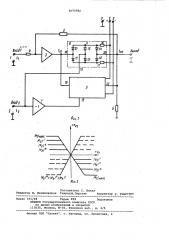

На фиг. 1 представлена схема двустороннего ограничителя напряжения; на фиг. 2 — выходная характеристика ограничителя.

Двусторонний органичитель (фиг.1) содержит информационный 1 v. Управляющий 2 входы, операционный усилитель 3 с двумя масштабными резисторами 4 и 5, нагрузочный резистор 6, инвертор 7, два блока 8 и 9 выбора минимального сигнала, каждый из которых состоит иэ коммутирующих диодов 10-15, балансных резисторов

16 и 17, входы 18 и 19 блоков 8 и 9 соответственно, выход 20.

Вход 1 через масштабный резистор

4 связан с входом операционного усилителя 3 в масштабном режиме, выход которого связан с блоками 8 и 9 выбора минимального сигнала, выходы которого объединены и являются выходом ограничителя, связанным через нагрузочный резистор 6 с шиной нулевого потенциала, и через масштабный резистор 5 подключены к входу операционного усилителя 3. Вход инвертора 7 является управляющим входом ограничителя и соединен с вторым входом первого блока 8 выбора минимального сигнала, а выход инвертора 7 связан с вторым входом второго блока 9 выбора минимального сиг.нала,.

Блоки 8 и 9 выбора минимального сигнала содержат три параллельно включенные между собой ветви с двумя

1073782

При значениях управляющего напряжения по входу 2 te

Максимально возможное значение ограниченного напряжения на выходе ограничителя определяется выражением где 1 .— последовательно включенными коммутирующими диодами 10-11 и 12-13 соответственно. Общий вывод диодов 10 и 11 подключен к первому входу блока, общий вывод диодов 12 и 13 — к второму входу, а общий вывод диодов

14 и 15 — к выходу блока, вершины ветвей через балансные резисторы

16 и 17 подключены в проводящем направлении к выводам положительной и отрицательной полярности источника опорного напряжения со средней точкой, объединенной с шиной нулевого потенциала.

Ограничитель работает следующим образам..

Передаточная функция ограничителя имеет вид, определяемый выражением

Е„=е,— п лл1е„1< е,,; (1

Rr, е,=

t e> l при 1 е ол > е 1, ; е „л = 1 нас! где е — выходное напряжение ограни о чителя;

Вол — напряжение на выходе операционного усилителя; 25 номинал масштабного резистора 4 (по входу 1)

"5 - номинал масштабного резистора 5 в обратной связи операционного усилителя 3; 30 ! ейt; - уровень управляющего напряжения (по входу 2); "нас! — максимально возможное значение выходного напряжения операционного усилителя 3 в нелинейной зоне.

Режим 1 соответствует работе операционного усилителя в линейной зоне его выходной характеристики. В этом режиме проходное сопротивление одно- 4О го из блоков 8 или 9 будет равно

0 Ом, а другого — -лю, и на вы-. ходе устройства по логике ИЛИ будет иметь место выходное напряжение, определяемое уровнем входного напряжения на входе 1 и отношением номиналов резисторов Rq и 4.. напряжение источника опорнога напряжения относительно средней точки; номинал нагрузочного резистора; номинал балансного резистора.

Выходное напряжение инвертора 7 осуществляет коммутацию проходных сопротивлений блоков 8 и 9..для фор- мирования двусторонней выходной ха- рактеристики ограничителя.

При значении 6, «leo t a c выходное напряжение ограничителя не зависит от номинала нагрузочно;го резистора R6 в отличие от аналога и прототипа поскольку значение текущего уровня не достигает гранич ных условий, определяемых выраже:нием (2j .

Применение предложенного устройства позволяет Расширить диапазон изменения уровня ограничения.

1073782

2;-ф л

le2/Ðïóêñ

/ ю/ р 4 (p /Ф у кс

Закаэ 331/48 Тираж 699

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Составитель С. Белан

Редактор Л. Веселовская Техред М. Гергель Корректор Г. Решетник