Устройство для подстройки фазы несущей частоты приемника дискретной информации

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

09) (И) ЗСЮ Н 04 Ь 27 22

1 Ф ";

А

I (; gO

t 3

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21 ) 3 501 0 75/1 8-09 (22) 11.10-.82 (46)15.02.84. Вюп. р 6 (72)В.A., Виневич, В.И. Седов и Е.A. Баскакова (53)621..394.66(088.8) (56)1. Основы техники радиосвязи. . Под ред. М.В. Верзунова. N. Воен. нэд. Мин. Обор. СССР, 1972, с. 44.

2. HespeIt V. und MeIzenbach И.

".DigitaIe Trager und, TaktabIeitung

f8r Quadraturamplitudenmodulations

)/AN)-Datenubertragungssysteme", AEU, Band 34, Heft 3, Иагй 1980, S. 133141 (прототип). .(54)(57) УСТРОЙСТВО ДЛЯ,ПОДСТРОЙКИ

ФАЗЫ НЕСЯЦЕЙ ЧАСТОТЫ НРИЕИЯИКА ДИСКРЕТНОЙ ИВФОРИАЦИИ, содержащее блок регистрации координат принятого сигнала, выход которОго соединен с первым входом блока регулирования Фазового сдвига, второй вход которого соединен с выходом блока Формирования управляющего сигнала, вход которого подключен к выходу блока определения сежбки фазы принятого сигнала, причем выход блока регулирования Фазового ! сдвйга соединен с входом декодера и с входом блока Формирования эталонного сигнала, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены блок выделения сигнала настройки, элемент задержки, сумматор, два коммутатора и блок Формирования дополнительного эталонного сигнала, выход которого соединен с первым входом первого ,коммутатора, второй вход которого соединен с выходом блока Формирования эталонного сигнала, вход которого соединен с первым входом сумматора, с первым входом второго коммутатора и с входом элемента задержки, выход которого соединен со вторым 3 входом второго сумматора, третий вход ,которого соединен с выходом блока выделения сигнала настройки и третьим вхоцом первого коммутатора, выход которого соединен с первым входом блока определения ошибки Фазы при- ф нятого сигнала, второй вход которого соединен с выходом второго коммутато ра, причем выход декодера подключен к входу блока выделения сигнала настройки.

1073897

Изобретение относится к электросвязи и может быть использовано в приемниках дискретной информации.

Известно устройство для подстрой.ки фазы, содержащее последовательно включенные опорный генератор,. фазовый детектор, фильтр нижних частот, регулирующий элемент и регулируемый генератор, второй вход которого соединен со вторым выходом фазового детектора (1 .

Недостатком этого устройства asляется низкая помехоустойчивость.Наиболее близким техническим решением к изобретению является устройство, содержащее блок регистрации ко- 5 ординат принятого сигнала, выход которого соединен с первым входом блока регулирования фазового сдвига, вто рой вход которого соединен с выходом блока формирования управляющего сиг- 20 нала, вход которого подключен к выходу блока определения ошибки фазы принятого сигнала, причем выход блока регулирования фазового сдвига соединен с входом декодера и с входом - 25 блока формирования эталонного сигнала f2) .

Однако это устройство обладает низким быстродействием.

Пель изобретения — повышение бы- 30 стродействия.

Цель достигается тем, что в устройство для подстройки фазы несущей частоты приемника дискретной информации, содержащее блок регистрации координат принятого сигнала, выход которого соединен с первым входом блока регулирования фазового сдвига, второй вход которого соединен с выходом блока формирования управляюще- 40 го сигнала, вход которого подключен к выходу блока определения ошибки фазы принятого сигнала, причем выход блока регулирования фазового сдвига соединен с входом декодера и с szoдом блока формирования эталонного сигнала, введены блок выделения сигнала настройки, элемент задержки,.сумматор, два коммутатора и блок формирования дополнительного эталонного сигнала, выход которогосоединен 50 с первым вхддом первого коммутатора, второй вход которого соединен с выходом блока формирования эталонного сигнала, вход которого соединен с первым входом сумматора, с первым 55 входом второго коммутатора и с входом элемента задержки, выход которого соединен со вторым входом сумматора, выход которого соединен со вторым входом второго коммутатора, 60 третий вход которого соединен с выходом блока выделения сигнала настройки и третьим входом первого ком мутатора, выход которого соединен с первым входом блока определения ошиб-65 ки фазы принятого сигнала, второй. вход которого соединен с выходом вто рого коммутатора, причем выход декодера подключен к входу блока выделения сигнала настройки.

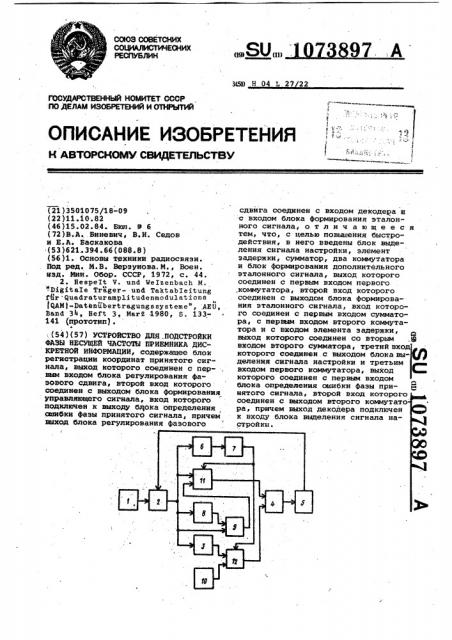

На чертеже изображена структурная электрическая схема предлагаемого устройства.

Устройство для подстройки фазы несущей частоты приемника дискретной информации содержит блок 1 регистра-, ции координат принятого сигнала, блок

2 регулирования фазового сдвига, блок

3 формирования эталонного сигнала, блок 4 определения ошибки фазы принятого сигнала, блок 5 формирования управляющего сигнала, декодер 6, блок

7 выделения сигнала настройки, элемент 8 задержки, сумматор 9, блок 10 формирования дополнительного эталонного сигнала, первый и второй коммутаторы 11 и " 2.

Устройство работает следующим образом.

Принятый сигнал поступает на вход блока 1 регистрации координат принятого сигнала, с выхода которого че- рез блок 2 регулирования фазового сдвига поступает на входы декодера

6, элемента 8, задержки, сумматора 9, блока 3 формирования эталонного сигнала и коммутатора 11. На входы сумматора 9 поступает сигнал, принятый на данном такте, и сигнал, принятый на предыдущем такте, прошедшем через элемент 8 задержки. Сумма этих двух принятых сигналов, являющаяся единcTBBHBBIM дополнительным сигналом,c выхода сумматора 9 поступает на первый вход коммутатора 11. Блок 7 выделения сигнала настройки формирует сигнал пе-, реключения коммутаторов 11 и 12 таким образом, что при приеме настроечной комбинации на первый и второй входы блока 4 определения ошибки фазы принятого сигнала поступает единственный дополнительный сигнал и единственный дополнительный эталон. Блок

4 определения ошибки фазы принятого сигнала формирует сигнал фазовой ошибки, как разность единственного дополнительного сигнала и единственного дополнительного эталона. Сигнал фазовой ошибки с выхода блока 4 определения ошибки фазы принятого сигнала поступает на вход блока 5 формирования управляющего сигнала, где преобразуется в управляющий сигнал подстройки фазы, поступающий на второй вход блока 2 регулирования фазового сдвига, который осуществляет подстройку фазы на угол, зависящий от знака и величины управляющего сигнала.

Предлагаемое .устройство позволяет ускорить вхождение в связь при пере

1073897

Составитель A. Москевич

Техред Т.Маточка Корректор О. Тигор

Редактор 34 Химчук

Заказ 379/54

Тираж 635

Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

М °

Филиал ППП "Патент", г, Ужгород, ул. Проектная, 4 даче данных за счет устранения неоднозначности подстройки фазы, воз., йикающей при приеме комбинаций настройки с повторениями двух чередующихся сигналов и приводящей к необходимости повторного вызова комбинации настройки. устранение неоднозначl ности подстройки фаз достигается тем, что в предлагаемом устройстве для формирования управляющего сигнала, используется сдвиг по фазе между единственной функцией принятых чередукицихся сигналов и единственным дополнительным. эталонным значением.