Устройство для измерения разности фаз

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (И) А

3(51) Й 01 К 25/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ(3ЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 783706 (21) 3430436/18-21 (22) 05..05.82/ (46) 23.02.84.Вюл. Ф 7 (72) В.A.ßöêåâè÷ (71) Гомельский государственный университет (53) 621.317.77(088.8) (56) 1 ° Авторское свидетельство СССР

М 783706, кл. G 01 R 25/00, 1979. (54)(57) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ

РАЗНОСТИ ФАЗ по авт.св. 9 783706, о т л и ч а ю щ е е с я тем, что, целью првышения точности измерения путем однозначного определения величины разйости фаэ, в устройство введены блок сравнения амплитуд, третйй запоминающий блок, фазовращатель и третий ключ, выход которого подключен к входу первого ключа и выходу фаэовращателя, присоединенного входом к.первой входной шине и входу третьего ключа, управляющий вход которого подсоединен к дополнительному выходу блока управления, к четвертому входу которого присоединен управляющий вход третьего запоминающего блока, гри этом информационный вход его соединен с третьим выходом коммутатора и первым входом блока сравнения амплитуд, второй вход которого присоединен к выходу третьего запоминающего блока, а выход — к дополнительной выходной Е

Q шине.

1075183

Изобретение относится к измерительной технике и может найти применение в различных фазоизмерительных системах СВЧ диапазона.

По основному авт.св. 9 783706

:известно устройство для измерения разности фаз, содержащее сумматор, выход которого соединен с входом детектора, подключенного к второму вхо,цу коммутатора, к первому входу кото рого присоединен первый выход блока управления, второй и третий выходы которого подключены соответственно к управляющим входам первого и второго ключей, присоединенных выходами к входам сумиатора, а четвертый выход 15 блока управления подключен к управляющим входам запоминающих блоков, информационные входы которых сое,цинены с первым и вторым выходами .коммутатора, третий выход которого >0

"оединен с одним входом вычитающего блока, соединенного другими выходами выходами запоминающих блоков и вхо,цами трехполюсного функционального преобразователя, выход .которого под- >5 ключен к одному входу измерителя отношений, другой вход которого присое,цинен к выходу вычитающего. блока (1) .

Работа известного устройства основана на принципе периодической поочередной подаче на детектор вход1ных сигналов и их суммы, запоминания детектированных сигналов и их обработки, в результате которой на выхо,це устройства формируется сигнал

0 „„=о сов, (<)

35 где 0 э ц — сигнал на выходной шине устройства, постоянный коэффициент, измеряемая разность фаз 40 между входными сигналами.

Достоинством известного устройства является независимость выходного сигнала от амплитуды и частоты входных сигналов, однако искомая 45 разность фаз Ц определяется численно по величине выходного сигнала неоднозначно

g = т агссо5 ° Вых

Это является недостатком устройства, так как достоверность измерения фазового сдвига в диапазоне

0-360 о снижается, становится неоднозначной.

Цель изобретения заключается в по-55 вышении точности измерения путем однозначного определения величины разности фаз.

Указанная цель достигается тем, что в устройство для измерения раз- 60 ности фаз дополнительно введены блок сравнения амплитуд, третий запомиьЬющий блок, фазовращатель и третий ключ, выход которого подключен к входу первого ключа и выходу фазовращателя, вход которого присоедийен к первой входной шине и входу третьего ключа, управляющий вход которого подключен к дополнительному выходу блока управления, к четвертому входу которого присоединен управляющий вход третьего запоминающего блока информационный вход которого подключен к третьему выходу коммутатора и первому входу блока сравнения амплитуд, второй вход которого присоединен к выходу третьего запоминающего -блока, а выход подключен к дополнительной выходной шине.

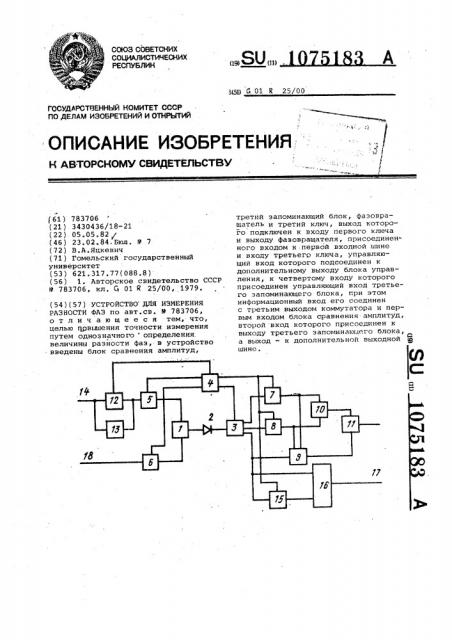

На чертеже приведена схема предлагаеМого устройства для измерения разности фаз.

Схема содержит сумматор 1, детектор 2, коммутатор 3, блок 4 управления, первый. ключ 5, второй ключ 6, первый запоминающий блок 7, второй запоминающий блок 8, вычитающий блок 9, трехполюсный функциональный преобразователь 10, измеритель 11 отношений, третий ключ 12, фазовращатель 13, первую входную шину 14, третий запоминающий блок 15, блок 16 сравнения. амплитуд, дополнительную выходную шину 17, вторую. входную шину 18.

Сумматор 1 соединен с входом детектора 2, выход которого подключен к второму входу коммутатора 3, к первому входу которого присоединен пецвый выход блока 4 управления, .второй и третий выходы которого подключены соответственно к управляющим входам первого и второго ключей

5 и 6, выходы которых присоединены к входам сумматора 1, а четвертый выход блока 4 управления подключен к управляющим входам запоминающих блоков 7 и 8, информационные входы которых соединены с первым и вторым выходами коммутатора 3, третий выход которого соединен с одним -входогл вычитающего блока 9, другие входы которого соединены с выходами запоминающих блоков 7 и 8 и входами функционального преобразователя 10, выход которого подключен к.одному входу измерителя 11 отношейний, другой вход которого присоединен к выходу вычитающего блока 9, а выход третьего ключа 12 подключен к входу первого ключа 5 и выходу фазовращателя 13, вход которого присоединен к первой входной шине 14 и входу третьего ключа 12, управляющий вход которого подключен к дополнительному выходу блока 4 управления, к четвертому входу которого присоединен управляющий вход третьего запоминающего блока 15, информацйонный вход которого подключен к третьему выходу коммутатора 3 и первому входу блока 16 сравнения амплитуд, второй вход которого присоеди1075183

I где 0 — амплитуда третьего слагае-. мого сигнала на выходе коммутатора 3", I амплитуды сигналов на выходе коммутатора 3 после первого и второго циклов, зафиксированные в запоминающих блоках 7 и 8, искомая разность фаз между входными сигналами, 10 ЬЦ вЂ” фазовый сдвиг, вносимый фазовращателем 13, некоторая постоянная измерения. (Сигнал, равный векторной сумме входных напряжений, поступает через коммутатор 3 на информационный вход третьего запоминающего блока 15 и там фиксируется.

В последнем четвертом цикле измерения устройство работает аналогично третьему циклу известного устройства..

При этом открыты все три ключа 5,6 и 12 и на выходе детектора 2 формируется сигнал, равный векторной сумме входных сигналов без дополнительного фазового сдвига, так как фазовращатель 13 закорочен нен к выходу третьего запоминающего, блока 15, выход блока 16 сравнения амплитуд подключен к дополнительной выходной шине 17, а вход .второго ключа б присоединен ко второй входной шине 18.

Работа устройства основана на последовательной подаче на детектор 2 входных сигналов, их суммы, а также их суммы при доПолнительном малом фазовом сдвиге одного из входных сигналов. Величина искомой разности фаз однозначно определяется по сигналам на выходе измерителя 11 отношений и дополнительной выходной шине 17.

Измерения производятся в четыре цикла, которые задаются блоком 4.

В первом цикле открыты третий и первый ключи 12 и 5 и первый входной сигнал с первой входной шиной 14 . через ключи.12 и 5 поступает через . сумматор 1 на вход детектора 2, с выхода которого сигнал, пропорциональныи квадрату амплитуды первого входного сигнала, поступает через коммутатор 3 на информационный вход первого запоминающего блока 7 и там фиксируется.

Во втором цикле открыт только второй ключ б и на детектор 2 с шины 18 через ключ б и сумматор 1 по= ступает второй входной сигнал, который после детектирования оказывается пропорциональным квадрату амплитуды второго входного сигнала. Этот сигнал через коммутатор 3 поступает 35 на информационный вход запоминающего блока 8 и там фиксируется.

Указанные два цикла полностью ана логичны первым двум циклам работы известного устройства, .4О

Основное отличие заключается в третьем цикле работы. В этом цикле первый и второй ключи 5 и б открыты, а третий ключ 12 закрыт. При этом первый входной сигнал с шины 14 45 проходит через фазовращатель. 13, от крытый ключ 5 и поступает на один вход сумматора 1, на другой вход которого поступает второй входной сигнал с шины 18. Сигнал с выхода сумматора 1 поступает на детектор 2 а на третьем выходе коммутатора 3 формируется сигнал, содержащий три слагаемых и равный векторной сумме входных сигналов с шин 14 и 18, с учетом дополнительного фазового сдвига первого сигнала, вносимого включенным фаэовращателем 13.

Два слагаемйх равнй соответственно. значениям сигналов U и О, зафиксированных в запоминающих блоках 7 60 и 8 во время двух предьщущих циклов; а амплитуда третьего слагаемого равна

U = lЬЙ, 0 соВ(ьq) ®

0 2Ъ Г0, 0 сову, (4)

1 где u . — амплитуда третьего слагаемого сигнала на выходе коммутатора 3 во время четвертого цикла- измерения.

Сумматорный сигнал, полученный во время четвертого цикла измерения с третьего выхода коммутатора 3 по ступает на один вход вычитающего блока 9, на два других входа которого поступают сигналы с запоминающих блоков 7 и 8, при этом в блоке 9 происходит вычитание первых двух слагаемых суммарного сигнала и на его выходе формируется сигнал, пропорциональный только coSg

Одновременно преобразователь 10 осуществляет перемножение амплитуды входных сигналов (результаты изм— рения первого и второго циклов) и извлечение квадратного корня из произведения. Этот сигнал поступает на один вход измерителя 11 отношений, на другой вход которого ,поступает сигнал с выхода вычитающего блока 9, при этом на выходе измерителя 11 отношений появляется окончательный выходной сигнал

U gb, с СОб Я, не позволяющий однозначно определить искомый фазовый сдвиг (Одновременно с этим во время четвертого цикла суммарный сигнал, равный векторной сумме входных сигналов беэ дополнительного фазового сдвига с третьего выхода коммутатора З.поступает на второй вход бло" ка 16, на первый вход которого с вы1075183

coo(% h()I} -cosy ур

7 соБ),ц q}-Созе ср. или

20 (7) Составитель A.CTàpîñòèíà

Техред Т.Маточка !(орректор О. Билак

Редактор С.Патрушева

Тираж 711 Подписное

ВНИИПИ Государственного комитета СCCP по делам изобретений и открытий

113035, Москва„ Ж-35, Раушская наб., д. 4/5

Заказ 492/38

Филиал ППП "Патент",. г. Ужгород, ул. Проектная, 4 хода блока 15 поступает суммарный сигнал, равный векторной сумме входных сигналов с дополнительным фаэоBhlM сдвигбм и зафиксированный во- время третьего цикла. 06а эти сигнала содержат два соответственно равных слагаемых, пропорциональных квадратам амплитуд входных сигналов, а отличаются только третьими слагаемыми, поэтому разность м(жду ними равна

2b (cos(,q ь(р)-cosy) u< 0< . (5}

В блоке 16 осуществляется сравнение амплитуд этих суммарных сиг- )5 налов, т.е. фактически определяется следующее

В результате сравнения на выходе блока 16 появляется сигнал, который указывает какое из соотношений (б ) или (7)выполняется. Этот сигнал поступает на дополнительную выходную шину 17.

Необходимо отметить, что величина вносимого фазовращателем. 13 фазо- вого сдвига ЬЦ является малой величиной и соответствует порогу чувствительности блока 16 сравнения амплитуд на граничной частоте. За счет введения фаэовращателем 13 малого фазового сдвига ( и первого входного сигнала обеспечи,вается некоторое приращение самой функции, причем знак приращения (выражение (6) и (,7) определяется блоком 16. 40

Искомая. величина разности фаэ оцнозначно определяется по известному знаку этого приращения (больше или меньше нуля) и известной величины модуля разности фаэ, который определяется также, как и в известном устройстве. При этом учитывается, что четная функция соэ убывает и возрастает при значении аргумента О- Я и (- I2II СООтВЕтСтвеНнс.

Так если (с— (8) где q — .(скомая разность фаз, определяемая как ВЬ(к = тагccob и на выходе блока 16 появляется сигнал, указывающий, что выполняется соотношение (7), т.е. функция убывает, то Ос ср с /д (угол лежит в 1 квадранте..

Если же на выходе блока 16 сравнения амплитуд появляется сигнал, указывающий, что выполняется соотношение (б}, -..е. функция возрас" таЕт, тО -II/ c.(g) с (I (УГОЛ ЛЕжИт в 1Ч квадранте )

Аналогичным образом, если модуль разности фаз лежит в пределах

„ )ц).-„, (9} то при выполнении соотношения (7))

«/ с g c 9 (угол лежит, во 11 квадранте), а при выполнении соот/

2 ношения (6) (с 9" — ((угол лежит в ХХУ квадранте).

Таким образом, по сигналу на выходе блока 16, указывающему знак приращения и известному значению модуля разности фаэ определяется квадрант, в котором лежит искомый угол, Предлагаемое изобретение обеспечивает работоспособность в широкой подносе частот и широком динамическом диапазоне входных сигналов, Сравнение технических характеристик предлагаемого устройства с известным устройством показывает, что техническое преимущество заявляемого устройства заключается в обеспечении однозначного определения измеряемой разности фаз в диапазоне 0-360(". B известном устройстве измеренная разность фаэ определяется неоднозначно, знак плюс или минус измеряемого фазового сдвига остается неопределенным. Этот недостаток и"-вестного устройства, снижающий достоверность всего измерения, в заявляемом устройстве устраняется,