Устройство для прямого и обратного преобразования кода системы остаточных классов в двоичный код

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

«и и е

РЕСПУБЛИН

3(59 G 06 F 5 02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОЬРЕТЕНИЙ И ОТКРЫТИЙ (21 ) 3530250/18-24 (22) 29.12.82 (46) 23.02. 84. Бюл. Р 7 (72) П.Л. Прокопьев, В.A. Иванченко и А.Д., Щечкин (53) 681.325(088.8) (56) 1. Авторское свидетельство СССР

Р 574714, кл. С 06 F 5/00, 1976.

2. Авторское свидетельство СССР

Р 756401, G F 1976, (прототип) ° (54)(57) УСТРОЙСТВО ДЛЯ ПРЯИОГО И

ОБРАТНОГО ПРЕОБРАЗОВАНИЯ КОДА СНСТЕИЫ ОСТАТОЧНЫХ КЛАССОВ В ДВОИЧНЫЙ

КОД, содержащее группу реверсивных счетчиков по модулю, группу дешифраторов нуля, двоичный реверсивный счетчик, дешифратор нуля, переключатель, триггер режима, управляю.щий триггер, элемент И-НЕ, первый вход .которого соединен с выходом управляющего триггера, нулевой вход которого соединен с выходом переключателя, первый и второй входы которого соединены соответственно с выходом дешифратора нуля и элементом И, входы которого соединены с выходами дешифраторов нуля груп+ пы, информационные входы которых соединены с выходами соответствующих реверсивных счетчиков по модулю группы, управляющие входы которых соединены с выходом триггера режима, единичный и нулевой входы которого являются соответственно пер- вым и вторым управляющими входами устройства, тактовый вход и вход,Я0.„10?5254 A пуска которого соединены .соответственно .с вторым входом элемента И-НЕ и единичным входом управляи;.его триггера; выхОд триггера режима соединен с управляющим входом двоичного реверсивного счетчика, группа выходов иэ m разрядов которого соединена с информационными входами дешифратора нуля, где m удовлетво ряет условию P« c 2 2Р«, à pK - вели чина меньшего модуля в системе остаточных классов, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия, в него введены два элемента ИЛИ-НЕ и схема сравнения, причем выход элемента И-НЕ соединен с первыми входами первого ч

Я и второго элементов ИЛИ-НЕ, выходы которых соединены соответственно с первыми и вторыми счетными входами ивоичиого реверсивиого счетчика и реверсивных счетчиков по модулю груп пы, второй вход второго элемента Я .

ИЛИ-НЕ соединен с выходом первого элемента ИЛИ-НЕ, второй вход которого соединен с выходом дешифратора нуля. меньшего модуля s системе остаточных классов группы, управляющий 4 вход которого соединен с выходом триггера режима и управляющим входом схема сравнения, информационные Ю входы которой соединены с выходами Щ двоичного реверсивного счетчика, а у выход схемы сравнения соединен с тре тьим входом второго элемента ИЛИ-НЕ" и с управляющим входом дешифратора нуля.

1075254

Изобретение относйтся к вычислительной технике и может быть использовано в цифровых вычислительных устройствах для перевода чисел из двоичной позиционной системы счис. ления в .систему остаточных классов 5 (СОК) и обратно.

Известно устройство для прямого и обратного преобразования чисел из кода системы остаточных классов в двоичный код, содержащее прием- 10 ные регистры, накапливающие счетчики, суммирующие по модулю счетчики, коммутирующие элементы Г12.

Недостаток данного устройства заключается в значительном объеме оборудования, предназначенного для преобразования чисел.

Наиболее близким по технической сущности к предлагаемому устройству является устройство для прямого и обратного преобразования кода системы остаточных классов в двоичный код, содержащее группу реверсивных счетчиков, два элемента И, первый триггер и переключатель, причем единичный выход первого триггера подключен к первому входу первого элемента И, второй .вход которого соединен с так-, товым входом устройства, а выход подключен к входам счетчиков,:.выход второго элемента И подключен к перво-З0 му входу переключателя, выход которого соединен с нулевым входом первого триггера, единичный выход которого соединен с входом пуска устройства, второй триггер и группу 35 дешифраторов нуля, входы которых соединены с выходами соответствующих реверсивных счетчиков группы, выходы дешифраторов нуля группы подключены к входам второго элемента И, à 40 выход (и+1)-ro дешифратора, нуля, где и - число оснований в системе остаточных классов, соединен с вторым входом переключателя, нулевой и единичный входы второго триггера 45 подключены к первому и второму управляющим входам устройства соответственно, нулевой выход второго триггера подключен к входу управления сложением и первых реверсивных счетчиков группы и входу управления вычитанием (n+1)-го реверсивного счетчика, единичный выход второго триггера подключен к входу управления вычитанием л первых реверсивных счетчиков группы и входу управления сложением (n+1)-го реверсивного счет.чика (2 3.

Недостатком известного устройства является сравнительно низкое быстродействие. 60

Целью изобретения является повышение быстродействия устройства при прямом и обратном преобразовании коца системы остаточных классов в двоичный код. 65

Поставленная цель достигается тем, что в устройство, содержащее группу реверсивных счетчиков по модулю, группу дешифраторов нуля, двоичный реверсивный счетчик, дешифратор нуля,, переключатель, триггер режима, управляющий триггер, элемент

И-ЙЕ, первый вход которого соединен с выходом управляющего триггера, нулевой вход которого соединен с выходом переключателя, первый и второй входы которого соединены соответственно с выходом дешифратора нуля и элементом И, входы которого соединены с выходами дешифраторов нуля группы, информационные входы которых соединены с выходами соответствующих реверсивных счетчиков по модулю группы, управляющие входы которых соединены с выходом триггера режима, единичнйй и нулевой входы которого являются соответственно первым и вторым управляющими входами устройства, тактовый вход и вход пуска которого соединены соответственно с вторым входом элемента И-НЕ и единичным входом управляющего триггера, выход триггера режима соединен с управляющим входом двоичного реверсивного счетчика, группа выходов из m разрядов которого соединена с информационными входами дешифратора нуля, где

m удовлетворяет условию Рк < 2 <2Р а P — величина меньшего модуля в системе остаточных классов, дополнительно введены два элемента ИЛИ-НЕ и схема сравнения, причем выход элемента И-НЕ соединен с первыми входами первого и второго элементов ИЛИ-НЕ выходы которых соединены соответственно с.первыми и вторыми счетными входами двоичного реверсивного счетчика и реверсивных счетчиков по модулю группы, второй вход второго элемента ИЛИ-НЕ соединен с выходом первого элемента ИЛИ-НЕ, второй вход которо-о соединен с выходом дешифратора нуля меньшего модуля в системе остаточных классов группы, управляющий вход которого соединен с выходом триггера режима и управляющим входом схемы сравнения, информационные входы которой соединены с выходами двоичного реверсивного счетчика, а выход схемы сравнения соединен с третьим входом второго элемента ИЛИ-НЕ .и с управляющим входом дешифратора нуля.

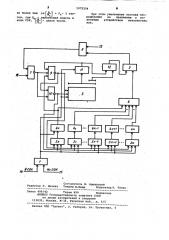

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит триггер 1 режима, двоичный реверсивный счетчик 2, группу реверсивных счетчиков 3 по модулю, группу дешифраторов 4 нуля, переключатель 5, управляющий триггер .6, элемент И-НЕ 7, элемент И 8, элементы ИЛИ-НЕ 9 и 10, схему 11

10i5254 сравнения, дешифратор 12 нуля, вход

13 пуска, первый и второй управляющие входы 14 и 15 устройства, тактовый вход 16.

Предлагаемое устройство работает следующим образом.

Первый управляющий вход 14, сигнал на который подается при преобразовании числа из двоичного кода в код СОК, подключен к единичному входу триггера 1. Сигнал, пришедший на первый управляющий вход, переключает триггер 1 в единичное состояние, и сигнал с его выхода подготавливает двоичный реверсивный счетчик 2 к работе в режиме

"Вычитание", счетчики 3 — к работе в режиме "Сложение", а дешифратор

4 устанавливает a нулевое состоя нйе. Преобразуемое число в двоичном коде записано в счетчике 2, счетчики 3 обнулены. Сигнал, приходящий на вход 13 пуска, устанавливает триггер 6 в единичное состояние, сигналом с единичного выхода которого открывается элемент И-НЕ 7 по первому входу, на второй вход которого поступают тактовые импульсы.

Нулевой сигнал с выхода дешифратора 4 нуля поступает на второй вход элемента ИЛИ-НЕ 9. Если содержимое счетчика 2 больше или равно величине наименьшего модуля кода

СОК Р К, то единичный сигнал с выхода схемы 11 сравнения, пройдя через третий вход элемента ИЛИ-НЕ 9, устанавливает на выходе элемента

ИЛИ-НЕ 9 нулевой сигнал, который подается на вход элемента ИЛИ-НЕ 10. . По тактовому сигналу, прошедшему через элемент И-НЕ 7, на входе элемента ИЛИ-НЕ 10 устанавливается нулевой сигнал. При этом по единичному сигналу с выхода элемента

ИЛИ-НЕ 10 происходит постепенное вычитание величины Рк в счетчике 2 и сложение с величиной Рк в счетчиках 3. Когда содержимое счетчика 2 станет меньше величины Р„, на выходе схемы 11 сравнения будет нулевой сигнал, что, в свою очередь, вызывает, при наличии тактового импульса, единичный сигнал на выходе элемента ИЛИ НЕ 9 и нулевой сигнал на выходе элемента ИЛИ-НЕ 10. По единичному сигналу с выхода элемента

ИЛИ-НЕ 9 происходит постепенное вычитание по единице в счетчике 2 и сложение с единицей в счетчиках

3. В момент обнуления счетчика 2 срабатывает дешифратор 12 нуля, сигнал с выхода которого, пройдя через переключатель 5, переводит триггер 6 в нулевое состояние. При этом прекращается поступление тактовых импульсов через элементы И-НЕ 7, ИЛИ-НЕ 9 и 10. В счетчиках 3 заре-

50

Предлагаемое устройство обладает большим быстродействием, чем извест1 ное, так как в нем прямое и обрат60 ное преобразование чисел из кода б5

35 гистрирован код СОК, соответствующий двоичному коду, первоначально записанному в счетчике 2.

Второй управляющий вход 15 при преобразовании числа из кода СОК в двоичный код подключен к нулевому входу триггера 1, сигнал с выхода которого устанавливает схему 11 сравнения в нулевое состояние и подготавливает счетчик 2 к работе в режиме "Сложение", а счетчик 3к работе в режиме "Вычитание,". Преобразуемое число в коде COK записано в счетчики 3, счетчик 2 обнулен. По сигналу пуска триггер б устанавливается в единичное состояние и сигналом с единичного выхода открывает элемент И- НЕ 7, на другой вход которого поступают тактовые импульсы. Нулевой сигнал с выхода схемы 11 сравнения поступает на третий вход элемента ИЛИ-НЕ 9. Если содержимое счетчика 3„ не равно нулю, то нулевой сигйал с выхода дешифратора 4 нуля поступает на второй вход элемента ИЛИ-НЕ 9. По тактовому сигналу, прошедшему через элемент И"НЕ 7, на выходе элемента

ИЛИ-НЕ 9 устанавливается единичный сигнал, по которому происходит постепенное сложение с единицей в счетчике 2 и вычитание по единице в счетчиках 3. В момент обнуления счетчика 3 на вход элемента ИЛИ-HE 9 с

К выхода дешифратора 4 „нуля подается единичный сигнал, а йа выходе ИЛИ-НЕ

9 появляется нулевой сигнал, который поступает на вход элемента ИЛИ-НЕ 10.

По тактовому сигналу, прошедшему через элемент И-НЕ 7, на выходе элемента IIJIII-НЕ 10 устанавливается единичный сигнал, по которому происходит постепенное сложение содержимого счетчика 2 с величиной Рк и вычитание величины Рк из счетчиков

3. В момент обнуления всех счетчиков

3 срабатывают дешифраторы 4, 4

4, нуля, сигналы с выходов которых, поступая на входы элемента

И 8, вырабатывают на его выходе сигнал, который, пройдя через переключатель 5 на нулевой вход триггера б, переводит его в нулевое состояние и прекращает тем самым поступление тактовых импульсов на входы счетчиков 2 и 3 через элементы

И-НЕ 7, ИЛИ-НЕ 9 и 10. В счетчике

2 при этом регистрируется двоичный код преобразованного числа.

СОК в двоичный код происходит за

N тактовых импульсов, где N — преобразуемое число в двоичном коде, а в предлагаемом устройстве аналогичное преобразование происходит

1075254

Составитель N. Аршавский

Редактор Р. Цицика Техред O,Íåöå Корректор A. Тяско.

Эаказ 499/42 Тираж б99 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 не более чем „за à — + Р - 1 тактов. где РК - наименй модуль в коде СОК,, 1 - целое число. „;"

При этом увеличение состава оборудования по сравнению с известным устройством неэначитель ное.