Запоминающее устройство с коррекцией ошибок

Иллюстрации

Показать всеРеферат

ЗАПОМИНАЮЩЕЕ -УСТРОЙСТВО С КОРРЕКЦИЕЙ ОШИБОК, содержащее первый и второй накопители, адресные входы которых подключены к выходам регистра адреса, выходы первого и второго накопителей подключены к первым входам соответственно первого и второго регистров, первые выходы которых подключены к входам соответствующих накопителей, вторые выходы первого и второго регистров подключены к первым входам соответственно первого и второго блоков сравнения, вторые входы которых подключены к выходам соответственно третьего и четвертого регистров, выходы первого и второго блоков сравнения подключены к первым входам соответственно первого и второго блоков элементов И, вторые входы которых подклюг чены к соответствующим выходам блока управ:пения, выходы первого и второго блоков элементов И подключены к вторым в содам соответственно первого и второго регистров, третьи выходы первого и второго регистров подключены к входам блока элементов ИЛИ, выход которого подключен к первому входу пятого регистра, второй вход н первый йыход пятого регистра являются соответственно информационными входом и выходом устройства, управляющие входы регистра адреса, накопителей, первого и второго блоков элементов И и регистров подключены к соответствующим выходам блока управления, отличающеес я тем, что, с целью повышения на (П дежности устройства путем обеспечения его работоспособности при возник-i новении отказов запоминающих элементов в одноименных разрядах ячеек памяти накопителей, оно содержит третий блок элементов И и элемент ИЛИ, входы которого подключены к выходам третьего блока элементов И, первый и второй входы третьего блока элементов И подключены к выходам соот .ветственно первого и второго блока сравнения, второй выход пятого регистра подключен к четвертым входам первого и второго регистров, выход элемента ИЛИ подключен к пятому входу первого регистра, входы третьего и четвертого регистров подключены к выходам соответственно первого и второго накопителей

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (И) 3(59 11 2 00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ" - . :, 13

°, c. °, ма на

К ABTOPCKOMV СВИДЕТЕЛЬСТВУ (21) 3512013/18-24 (22) 17, 11. 82 (46),23,02.84. Вюл. 9 7 (72) И.A. Дичка, А.Г. Забуранный, В;И. Корнейчук, М.Н. Орлова и В.П. Палкин. (71) Киевский ордена Ленина политехнический институт им. 50-летия Великой Октябрьской социалистической революции (53) 681,327(088 ° 8) (56) 1. Kuehn R.Е. Computer redundaucy des1ug, perfomauce and future-IEEE Trans. Rel1abi1, 1969, 18,91.

2. Гвторское свидетельство СССР

9 385319, кл. G 11 С 29/00, 1972 (прототип). (54)(57) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

С КОРРЕКЦИЕЙ ОШИБОК, содержащее первый и второй накопители, адресные

- входы которых подключены к выходам регистра адреса, выходы первого и второго накопителей подключены к первым входам соответственно первого и второго регистров, первые выходы которых подключены к входам соответствующих накопителей, вторые выходы первого и второго регистров подключены к первым входам соответственно первого и второго блоков сравнения, вторые входы которых подключены к выходам соответственно третьего и четвертого регистров, выходы первого и второго блоков сравнения подключены к первым входам соответственно первого и второго блоков элементов И, вторые входы которых подклю.чены к соответствующим выходам блока управления, выходы первого и второго блоков элементов И подключены к вторым входам соответственно первого и второго регистров, третьи выходы первого и второго регистров подключены к входам блока элементов

ИЛИ, выход которого подключен к первому входу пятого регистра, второй вход н первый выход пятого регистра являются соответственно информационными входом и выходом устройства, управляющие входы регистра адреса, накопителей, первого и второго блоков элементов И и регистров подключены к соответствующим выходам блока управления, о т л и ч а ю щ е еC с я тем, что, с целью повышения надежности устройства путем обеспечения его работоспособности при возник- новении отказов валоминаимик влемен-( тов в одноименных разрядах ячеек памяти накопителей, оно содержит тре- Я тий блок элементов И и элемент ИЛИ, входы которого подключены к выходам третьего блока элементов И, первый и второй входы третьего блока элементов И подключены к выходам соответственно первого и второго блока сравнения, второй выход пятого регистра подключен к четвертым входам первого н второго регистров, выход элемента ИЛИ подключен к пятому входу первого регистра, входы третьего и четвертого регистров подключены к выходам соответственно первого и второго накопителей.

1075312

Изобретение относится к устройствам вычислительной техники и может найти применение в цифровых вычислительных машинах четвертого поколения.

Известно запоминающее устройство, содержащее два адресных накопи3геля, соединенные с блоком декодирования, к которому подключен регистр слова, соединенный с адресными накопителями, а адресные накопители — соответственно с двумя буферными регистрами (1) .

Данное устройство обладает низкой устойчивостью к сбоям и отказам запоминающих элементов.

Наиболее близким по технической 15 сущности к изобретению является запоминающее устройство, содержащее регистр адреса, соединенный с двумя дешифраторами адреса, которые подключены к двум адресным накопителям, 20 соединенным с выходным регистром. К ,накопителям подключены два основных регистра слова, соединенные со схемой равенства кодов, которая через схему И подключена к первому основно- 25 му регистру слова, и группой схем

ИЛИ, подключенной к выходному регистру. каждый из основных регистров слова также связан с одним из двух дополнительных регистров слова и с одной из двух схем поразрядной проверки, с которыми соединены и дополни=ельные регистры слова, а схемы поразрядной проверки через группы элементов И подключены к основным регистрам слова. Блок управления связан с регистром адреса, накопителями, основными регистрами слова, схемой

И, дополнительными регистрами слова, группами схем И и выходным регистром (2J . 40 .Недостатком устройства является его неработоспособность при возникновении отказов запоминающих элемен-: тов в одноименных разрядах <<ееК 45 накопителей.

Целью изобретения является повышение надежности устройства за счет обеспечения его работоспособности при возникновении отказов запоминающих элементов в одноименных разрядах ячеек накопителя.

Указанная цель достигается тем, что запоминающее устройство с коррекцией ошибок, содержащее первый и второй накопители, адресные входы которых подключены к выходам регистра адреса, выходы первого и второго накопителей подключены к первым входам соответственно первого и второго регистров, первые выходы кото- 60 рых подключены к входам соответствующих накопителей, вторые выходы первого и второго регистров подключены к первым входам соответственно первого и второго блоков сравнения, вто-gg рые входы которых подключены к выходам соответственно третьего и четвертого регистров, выходы первого и второго блоков сравнения подключены к первым входам соответственно первого и второго блоков элементов И, . вторые входы которых подключены к соответствующим выходам блока управления, выходы первого и второго блоков элементов И подключены к вторым входам соответственно первого и второго регистров, третьи выходы первого и второго регистров подключены к входам блока элементов ИЛИ, выход которого подключен к первому входу пятого регистра, второй вход и первый выход пятого регистра являются соответственно информационнычи входом и выходом устройства, управляющие входы регистра адреса, накопителей, первого и второго блоков элементов И и регистров подключены к соответствующим выходам блока управления, содержит третий блок элементов И -и элемент ИЛИ, входы которого подключены к выходам третьего блока элементов И, первый и второй входы третьего блока элементов И подключены к выходам соответственно первого и второго блока сравнения, второй выход пятого регистра подключен к четвертым входам первого и второго регистров, выход элемента

ИЛИ подключен к пятому входу первого регистра, входы третьего и четвертого регистров подключены к выходам соответственно первого и второго накопителей.

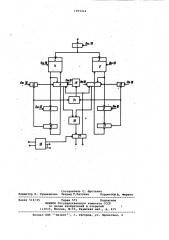

На чертеже приведена блоксхема . запоминающего устройства, содержащего регистр 1 адреса, дешифраторы 2 и 3 адреса, накопители

4 и 5, регистры 6 — 9, блоки 10 и 11 сравнения, блоки 12-14 элементов И, элемент ИЛИ 15, блок 16 элементов ИЛИ. регистр 17 и блок 18 управления.

В предлагаемом устройстве информация одновременно записывается (считывается) в оба накопителя 4 и 5.

Слово, подлежащее записи, находится в выходном регистре 17. Содержимое одноименных ячеек накопителей 4 и 5, в которые необходимо записать информацию, считывается на регистры

6-9. Обратный код содержимого регистров 6 и 7 записывается в те же ячейки накопителей 4 и 5 и считывается обратно на регистры 6 и 7.

Коды с регистров 6 и 7, а также с регистров 8 и 9 поступают на блоки

10 и ll сравнения, где определяются отказавшие разряды Отказавшими будут разряды, в которых прямой и обратный коды (т.е. содержимое регистров 6 и 8, а также регистров 7 и 9) совпадают, Блоки сравнения выдают единичные сигналы на тех выходных шинах, номера которых соответствуют

1075312 номерам отказавших разрядов. Сигналы с выходов блоков 10 и 11 поступают на входы блока 14 элементов И, одновременно информация с регистра 17 переписывается в регистры 6 и 7.

Блок 14 представляет собой совокупность двухвходовых элементов И, ко входам которых подключены одноименные выходы блоков сравнения. Срабаты ванне элементов И означает, что отказали одноименные запоминающие эле- 10 менты ячеек накопителей 4 и 5. Если сработает хотя бы один элемент И, то на выходе элемента ИЛИ 15 появится единичный сигнал, но которому содержимое регистра 6 циклически 15 сдвигается на один разряд влево.

Если имеют место отказы в разноименных разрядах ячеек (не срабатывает ни один элемент И), то сдвиг содержимого регистра 6 не осуществляется. -20

Затем по сигналу блока 18 управления информация с регистров 6 и 7 записывается в накопители 4 и 5 соответственно по заданному адресу.

На этом цикл записи оканчивается.

При чтении считанные по запрашиваемому адресу слова подаются на регистры 6-9. B те же ячейки накопителей 4 и 5 производится запись обратных кодов с регистров 6 и 7 и последукщее считывание этих кодов на эти же регистры. Коды с регистров

6 и 7, а также с регистров 8 и 9 поступают на блоки 10 и 11 сравнения, При несовпадении прямого и обратного кодов одноименных разрядов блоки M

10 и ll через блоки 12 и 13 элементов И по сигналу от блока 18 формируют разрешающие сигналы соответственно на регистры 6 и 7 на выдачу через блок 16 элементов ИЛИ содержи- 4Р мого только этих разрядов. Выдача содержимого разрядов регистров 6 к 7 происходит в обратном коде. Если имеют место отказы в одноименных разрядах (т.е. на выходе элемента

ИЛИ 15 появляется управлякщий сигнал), то выдача содержимого регистра 6 производится с циклическим сдвигом на один разряд вправо.

Пример. Допустим в некоторую ячейку накопителя.5 было записано слово 10011101, а в одноименную ячейку накопителя 4 то же слово, но с циклическим сдвигом на один разряд влево, .т.е. 00111011 поскольку при записи имели место отказы в одноименных разрядах.

При считывании информации на регистры 6 и 8 поступает gPllllll, на регистры 7 и 9 — 100Я1Я01.. Происходит запись обратных кодов содер- . жимого регистров 6 и 7 в накопители и последующее их считывание .на этн же регистры. При этом на регистр 6 поступит (}}.00010б, а на регистр 7

011(ОЯ10. Блок 10 сравнения разрешает выдачу в обратном коде - информа- ° цию 2-8 разрядов, т.е.

° 0111 ° 11 (точками отмечены. разряды слова, выдача которых блокируется), а блок сравнения 11 - 1,2,3.5 7,8 разрядов, т. е.

100.1 ° 01

В блоке 14 элементов И срабатывает шестой элемент И, поэтому выдача содержимого регистра 6 осуществляется с циклическим сдвигом вправо на один разряд, т.е.

1 ° 0111 ° 1

На выходе блока 16 элементов ИЛИ будет код 100011101, который поступает на регистр 17.

Изобретение позволяет обеспечить работоспособность запоминающего устройства при появлении ошибки в одноименных разрядах ячеек накопителей, что повышает его надежность.

1075312

Тирам 575 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Рауюская наб., д. 4/5

Закаэ 512/45

Филиал ППП Патент, r. Уигород, ул. Проектная, 4

Составитель С. ц1устенко

Редактор H. Пушненкова Техред Т.Маточка Корректор а. Ференц