Устройство для обнаружения и коррекции одиночных ошибок

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И КОРРЕКЦИИ ОДИНОЧНЫХ ОШИБОК, содержащее блок формирован-ия контрольных сигналов, одни из входов которого являются информаufiOHHbiMH входами устройства, и элементы НЕ, о т л ичающееся тем, что, с целью повышения быстродействия устройства, в него введены элемент И-НЕ и коммутаторы , адресные входы которых подключены к одним из выходов блока формирования контрольных сигналов, первые информационные входы коммутаторов соединены с информационными входами устройства, вторые информационные входы - с выходами элементов НЕ, входы которых подключены к информационным входам устройства, а выходы коммутаторов являются информа .ционными выходами устройства, контрольным входом которого является выход элемента И-НЕ, входы которого подключены к другим выходам блока формирования контрольных сигналов.

(19) 01) СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

3 ) G 11 С 29/00

Г

C.

1 - );» „ J

ОПИСАНИЕ ИЗОБРЕТЕНИЯ,,Н ABTOPCH0MV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЭОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3532143/18-24 (22) 30 ° 12.82 (46) 23.02.84. Бюл. )) 7 (72) A.Â. Абрамов, С.К. Киселев, В..В. Ляпинский и В.И. Родин (53) 681 ° 327 (088. 8) (56) 1. Авторское свидетельство СССР

9 720515, кл. G 11 С 29/00, 1980.

2. "Электроника, т. 54, )) 9, 1981, с. 36 (прототип). (54)(57) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ

И КОРРЕКЦИИ ОДИНОЧНЫХ ОШИБОК, содержащее блок формирования контрольных сигналов, одни из входов которого являются информационными входами устройства, и элементы НЕ, о т л ич а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены элемент И-НЕ и коммутаторы, адресные входы которых подключены к одним иэ выходов блока формирования контрольных сигналов, первые информационные входы коммутаторов соединены с информационными входами устройства, вторые информационные входы — с выходами элементов

НЕ, входы которых подключены к информационным входам уст(5ойства, а выходы коммутаторов являются информа,ционными выходами устройства, контрольным входом которого является выход элемента И-НЕ, входы которого подключены к другим выходам блока формирования контрольных сигналов. Я

1075313

Недостатком известного устройства является TBK)KB невысокое быстродействие, связанное с многоступенчатой схемой коррекции.

Целью изобретения является повы" шение быстродействия устройства при обнаружении и коррекции одиночной ошибки байта информации в коде Хэмминга.

45

Указанная цель достигается тем, что в устройство для обнаружения и коррекции одиночных ошибок, содержащее блок формирования контрольных сигналов, одни из входов которого являются информационными входами устройства, и элементы НЕ, введены элемент И-ЙЕ и коммутаторы, адресные входы которых подключены к одним из выходов блока формирования контрольнйх сигналов, первые информационные входы коммутаторов соединены с информационными, входами устройства, вторые информационные входы - c выходами элементов НЕ, входы которых подключены к информационным входам 60 устройства, а выходы коммутаторов являются информационными выходами устройства, контрольным выходом которого является выход элемента И-НЕ, входы котоРого подключены к другим

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам.

Известны устройства для обнаружения и коррекции одиночных ошибок, содержащие входной регистр, селектор, блок коррекции входной информации, генератор кода Хэмминга, регистр контрольного кода, регистр кода Хэмминга, блок коррекции контрольного кода, блок сравнения пари- (0 тета записываемой информации, блок .сравиения кода Хэмминга, блок обнаружения неисправностей, дешифратор ошибок, Yîíòðîëüíèé .блок. сравнения, выходной perAr.òð (1) (2g . 15

Недостатками этого устройства являются низкое быстродействие, вызванное многоуровневой схемой коррек.ции, и большие аппаратурные затраты.

Йаиболее близким техническим реше-20 нием K изобретению является устройство для обнаружения и коррекции ошибок в памяти, содержащее логический блок для формирования контрольных битов кода Хэмминга и битов синдрома, дешифраторы, входы которых подключены к выходам логического блока, а выходы — к первым входам логических элементов, реализующих функцию

ИСКЛРЧ 10(НЕЕ ИЛИ, на вторые входы которых поступает информация.из памяти, а с выходов элементов ИСКЛЮЧАКМЦЕЕ ИЛИ информация через инверторы передается на выходную магистраль данных (2) .

I выходам блока формирования контрольных сигналов.

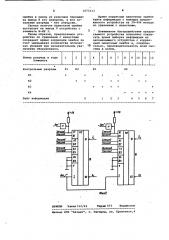

На фиг. 1 изображена структурная схема устройства для обнаружения и коррекции одиночных ошибок; на фиг. 2 — возможный вариант выполнения формирователя контрольных сигналов для двух разрядов.

Устройство (фиг. 1) содержит блок

1 формирования контрольных сигналов, служащий для формирования разрядов синдрома и контрольных разрядов кода

Хэмминга, элементы НЕ 2, элемент

И-HE 3 и коммутаторы 4. Устройство имеет входы 5 и 6 и выходы 7-9.

Блок 1,(фиг. 2) представляет собой четыре схемы 10 четности, формирующие контрольные разряды по .принципу построения кода Хэмминга, а также четыре элемента НЕ 11. При записи в память для формирования, например контрольного разряда Kl схема 10 четности (фиг. 2) должна проверять разряды 3,5,7,9 и 11; для

-формирования контрольного разряда

К2 - разряды 3, 6,7,10 и 11 и т.д. в соответствии с таблицей.

Элементы НЕ 11 при записи информации в память обнуляют входы схем

10 четности., на которые в режиме чтения поступают контрольные разряды код Хэмминга.

При чтении для формирования разряда Kl синдрома схема 10 четности дол:жна проверять разряды 1,3,5,7,9 и 11; для формирования разряда К2 — разряды 2,3,6,7,10 и 11 и т.д. в соответствии с таблицей.

Блок 1 может быть выполнен на микросхемах типа Кl 55 (133) ИП2 и

К155 (133) ЛНЗ. Коммутаторы 4 могут быть выполнены на микросхемах К 155 (133) КП1.

Устройство работает следующим образом.

Перед записью в память (не показана) со входа 5 устройства в блок

1 параллельно поступает байт информации. 8 блоке 1 происхоцит формирование четырех контрольных разрядов

Kl-Ê4 кода Хэмминга для байта информации.

Сформированные разряды поступают на выход 7 устройства для записи в память. При чтении на входы .5 и 6 параллельно нз памяти поступает информация в контрольные разряды кода

Хэмминга. При этом блок 1 формирует разряды Кl - K4 синдрома, которые поступают на адресные входы коммутаторов 4. Информация со входа 5 поступает также на входы элементов

НЕ 2 и первые информационные входы коммутаторов 4. На вторые информационные входы коммутаторов 4 поступает информация с выходов элементов

НЕ 2. Коммутаторы 4 при наличии

Ф

1 07. 531 3 ошибки в одном иэ разрядов передают на выход 8 его инверсию, а все остальные разряды — без инверсии.

Сигнал наличия одиночной ошибки поступает на выход 9 устройства с элемента И-НЕ 3.

Таким образом, предлагаемое уст,ройство по сравнению с известным сокращает время коррекции ошибки за счет уменьшения количества логических уровней при незначительном увеличении оборудования.

2 3 4 5 6 7 8 9 10 11 12

Контрольные разряды

КЗ

Кl К2

К4

К1, + +

+ +

+ + + +

К2

КЗ

К4

+ + + + +

4 5 6 7

l 2 . 3

Байт информации фаад

ВНИИПИ Заказ 512/45 Тираж 575 Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4

Номер разряда в коде 1

Хэмминга

Время коррекции одиночных ошибок байта информации с помощью предложенного устройства на 30-40% меньше по сравнению с известныи.

Повышенное быстродействие предлагаемого устройства позволяет сократить время выборки информации иэ запоминающего устройства с коррекцией одиночных ошибок и, следова-!

О тельно, производительность,всей системы в целом.