Широтно-импульсный частотно-фазовый детектор

Иллюстрации

Показать всеРеферат

WHPOTHO-ИМПУЛЬСНЫЙ ЧАСТОТНОФАЗОВГЛЙДЕТЕ1СТОР , содержащий два D-трйггера, входы синхронизации которых соед11нены с клеммами входных импульсных сигналов, информационные входы и входы установки в нуль - с общей шиноП, а тйкже первой и второй логические элементы 2И-НЕ, причем входы первого логического элемента 2И-НЕ соединеньл с инверсными выходами триггеров, из входов второго логического элемента 2W-HE соединен с выходом первого логического элемента 2И-НЕ, отличаюЧцийся тем, что, с целью уменьшения ошибки детектирования , в него введены датчик равенства частот, элемент задержки и логический элемент ЗИ-НЕ, два входы которого соединены соответственно с входами синхронизации обоих триггеров, входы датчика равенства частот соединены с прямылш выходами триггеров, а его выход - с третьим входом логичед кого элемента ЗИ-НЕ, выход которого соединен с вторым входом второго логического элемента 2И-НЕ, вход элемента задержки соединен с выходом щ второго логического элемента 2И-НЕ, (Л а выход - с входами установки в единицу триггеров.

СОНИ COBEFCHHX

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК 09) 411) всю н оз в 1з оо

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ГЮ ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ . ". Б

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ..(21) 3388021/18-21 (22) 29 ° 01 ° 82 (46) 23.02.84. Бюл. ?? 7 (72) A.Н. Гороховатский, Н.Н. Калаянов и С.К. Романов (53) 621.374 ° 5(088.8) (56). 1.Авторское свидетельство СССР

9 985929, кл. Н 03 D 13/00, 1980.

2. Electronic Design, vol.21, 9 18, 1973, с. 113, рис. 2 (прототип). (54)(57) ?11ИРОТНО-ИМПУЛЬСНЫЙ ЧАСТОТНОФАЗОВ?1Й ДЕТЕКТОР, содержащий два

D-триггера, входы синхронизации которых соединены с клеммами входных импульсных- сигналов, информационные входы и входы установки в нуль — с общей шиной, а также первой и второй логические элементы 2И-НЕ, причем входы первого логического элемента

2И-НЕ соединены с инверсными выходами триггеров,а один из входов второго логического элемента 2?I-НЕ соединен с выходом первого логического элемента

2И-НЕ, о т л и ч а ю Ъц и и с я тем, что, с целью уменьшения ошибки детектирования, в него введены датчик равенства частот, элемент задержки и логический элемент 3И-НЕ, два входы которого соединены соответственно с входа я синхронйзации обоих триггеров, входы датчика равенства частот соединены с прямыми выходами триггеров, а его выход — с третьим входом логического элемента ЗИ-НЕ, выход которо го соединен с вторым входом второго логического элемента 2И-НЕ, вход элемента задержки соединен с выходом второго логического элемента 2И-НЕ, а выход — с входами установки в единицу триггеров.

1075368

Изобретение относится к радиотехнике и предназначено для работы в радиотехнической аппаратуре в цепи фазовой автоподстройки частоты (ФАПЧ), Известен импульсный частотно-фазовый детектор, содер>кащий два D-триг- 5 гера и интегратор, входы которого сое-. динены соответственно с прямым выходом первого и инверсным выходом второго триггеров, вход синхронизации каждого из которых соединен с одной 10 из клемм входного сигнала и входом установки в нуль другого триггера, а.информационный вход каждого триггера соединен с инверсным выходом другого триггера (1)..

Недостатком данного устройства является наличие общего сброса триггера, что приводит к неучтенной начальной фазовой ошибкр.

Наиболее близким к предложенному изобретению по технической сущности является широтно-импульсный частотнофазовый детектор, содержащий два триггера, .входи синхронизации кото; .рых соединены с входными клеммами импульсных сигналов, а инверсные выходы — с входами первого логического элемента 2И-НЕ, выход которого соединен с входом второго логического элемента 2И-НЕ, выходом соединенного с входами установки в единицу триггеров, информационные входы и входы установки в нуль которых соедине>ы с общей шиной (2) .

Недостатком известного устройст-. ва является наличие начальной ошиб- 35 ки детектирования, величина которой изменяется от разброса параметров элементов схемы по быстродействию.

Ошибка детектирования приводит к фазовой ошибке в системе ФЛПЧ, для 40 компенсации которой вырабатывается компенсирующий импульс на противополо>кном выходе регулирования. Вследствие этого увеличивается уровень пульсации в управляющем напряжении системы ОЛПЧ и, таким образом, увеличивается уровень побочных составляющих в спектре выходного сигнала.

Целью изобретения является уменьшение фазовой ошибки детектирования.

С этой целью в широтно-импульс.ный частотно-фазовый детектор, со-. держащий два D-триггера, входы синхронизации которых соединены с клеммами входных импульсных сигналов, информационные входы и входы установки в нуль — с общей шиной, а также первый и второй логические 60 элементы 2И-НЕ, причем входы первсц.о логического элемента 2И-НЕ соединены с инверсными выходами триггеров, а один из входов второго логического элемента 2И-HE соединен с 65 выходом первого логического элемента

2И-НЕ, введены датчик равенства частот, элемент задержки и логический элемент ЗИ-НЕ, два входа которого соединены соответственно с входами синхронизации обоих триггеров, входы датчика равенства частот соединены с прямыми выходами триггеров, а его выход .- с третьим входом логического элемента ЗИ-НЕ, выход которого соединен с вторым входом втброго логического элемента 2И-НЕ, вход элемента задержки соединен с выходом второго логического элемента 2И-НЕ, а выход — c входами установки в единицу триггеров.

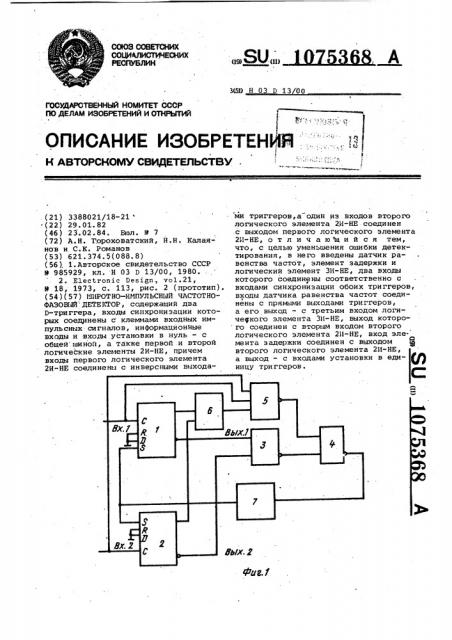

На фиг. 1 представлена блок-схема . детектора; на фиг. 2 - временные диаграммы работы широтно-импульсного частотно-фазового детектора.

Ыиротно-импульсный частотно-фазовый детектор (ЫИЧФД) содержит

D-триггеры 1 и 2, первый и второй логические элементы 2И-НЕ 3 и 4, логический элемент ЗИ-НЕ 5, датчик

6 равенства частот и элемент 7 задержки.

I3 широтно-импульсном частотнофазовом детекторе входы синхронизации D-триггеров 1 и 2 соединены с клеммами входных сигналов. Входы установки в нуль и информационные входы D-триггеров 1 и 2 соединены с общей шиной, а входы установки в единицу D-триггеров 1 и 2 соединены с выходом элемента 7 задержки.

Прямые выходы D-триггеров 1 и 2 соединены с входами датчика б равенства частот, выход которого соединен с одним из входов логического элемента ЗИ-НЕ 5, другие входы которого соединены с входами синхронизации

D-триггеров 1 и 2. Инверсные выходы

D-триггеров 1 и 2 соединены с входами логического элемента 2И-HE 3, выход которого соединен с одним из входов логического элемента 2И-HE 4, второй вход котброго соединен с выходом логического элемента ЗИ-НЕ 5, а выход — с входом элемента 7 задерк:ки.

Устройство работает следующим образом.

При поступлении последовательности входных импульсов на клеммы входных сигналов на инверсных выходах

D-триггеров 1 и 2 формируется импульс ная последовательность, ширина импульсов в которой зависит от величины разности фаз сигналов, поступающих на входы синхронизации триггеров 1 и 2.

В случае болыщой разности частот сигналов, поступающих на вход синхронизации, датчик б равенства частот имеет на выходе уровень логического нуля.

1075368 адержюоа

ВНИИПИ Заказ 514/48 Тираж 86? Подписное

ФФ ° Ю

Филиал ППП "Патент", г. Ужгород, ул.Проектная, 4

Датчик б равенства частот может быть выполнен, например, иэ элементов 2И-НЕ, входы которого являются входами датчика 6, а выход соединен с положительным выводом диода, отрицательный вывод которого соединен с резистором, конденсатором и элементом НЕ, при этом другие выводы резистора и конденсатора соединены. с общей шиной, а выход элемента НЕ является выходом датчика б.

Датчик б фиксирует грубое .равенство частот в зоне синхронизации, когда импульсы на входе ШИЧФД периодически совпадают во времени. С этого момента изменяется структура

ШИЧФД и он становится уже фазовым детектором с меньшей ошибкой, величину которой можно выбирать в прак.тически нужных пределах. Необходи-. мость изменения структуры состоит в том, что фазовый детектор обладает ограниченной полосой захвата и не может использоваться непосредственно в системах, где возможны начальные отстройки по частоте. (при включении питания, при переходе с одной рабочей частоты на другую).

В случае равенства частот входных импульсов датчик 6 равенства частот подает команду уровнем логической единицы на вход логического элемента 5. С,этого момента сигнал сброса формируется от двух совпадающих импульсов параллельно с рабочей установкой D-триггеров 1 и 2.

Фронтом импульса, поступающим на вход синхронизации, триггер 1 устанавливается в состояние уровня логического нуля. Установка триггера 1 происходит с- задержкой на

5 время г, обусловленной .срабатыванием триггера 1 (фиг. 2). От фронта импульса, поступающего на вход ,синхронизации триггера 2, формируется импульс сброса, по длительгО ности равный длительности совпадения входных импульсов. Если величину задержки t выбрать такой, чтобы суммарная задержка сброса триггера в начальное. состояние оставалась меньше величины задержки срабатывания триггера 2 по входу синхрони эации, то триггер 3 остается в исходном состоянии.

На инверсном выходе триггера 1, О присутствует импульс, по длительности пропорциональный разности фаэ (6 ), а на инверсном выходе три ггера 2 импульс отсутствует . Таким образом, ошибку детектирования

1 „,„ всегда можно учесть и путем регулировки величины задержки эле-мента 7 уменьшить или устранить полностью.

Положительный эффект от применения предлагаемого широтно-импульсного частотно-фазового детектора выражается в уменьшении фазовой ошибки детектирования в. системе

ФАПЧ и как следствие — в уменьшении уровня побочных составляющих s спектре выходного сигнала системы ФАПЧ.