Псевдолинейное корректирующее устройство для систем управления

Иллюстрации

Показать всеРеферат

1. ПСЕВДОЛИНЕЙНОЕ КОРРЕКТИРУЮЩЕЕ УСТРОЙСТВО ДЛЯ СИСТЕМ УПРАВЛЕНИЯ , содержащее последовательно соединенные блок сигнатуры, интегратор с конденсатором в обратной связи, блок выделения модуля и блок умножения, отличающееся тем, что, с целью уменьшения фазового запаздывания и повышения точности воспроизведения входного сигнала, в него введены логический блок, а также последователь но, соединенные сумматор и усилитель , выход которого соединен с вторым входом блока умножения,причем вход устройства является одновременно входом для блока сигнатуры, сумматора и логического блока, выход которого соединен параллельно с конденсатором интегратора и является его вторым входом, выход блока умножения соединен с вторым входом сумматора и является выходом устройства 2. Устройство по П.1, отличающееся тем, что логический блок выполнен в виде последовательно соединенных дискриминатора и управляющего транзистора, причем вход дискриминатора соединен с входом логического блока, а его выход является выходом управляющего транзистора .

(}Ю (И) СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

3(59 С 05 В 5/01

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОЧНРЬГИЗ (21) 3513085/18-24 (22) 15.11.82 (46) 28.02.84. Бюл. Р 8 (72) Л.Г. Агейков, В.Б. Житков, А.Н. Кропотов, В.В. Малютин и В.A. Челышев (71) МВТУ им. Н.Э. Баумана (53) 62-50 (088.8)

I (56) 1. Иващенко Н.Н. Автоматическое регулирование. М., "Машиностроение", 1978, с. 228., 303-306.

2. Нелинейные корректирующие устройства в системах автоматического управления. Под ред. Ю.И. Топчеева. М., "Машиностроение", 1977, с. 202-207 (прототип). (54) (57) 1. ПСЕВДОЛИНЕЙНОЕ КОРРЕКТИРУЮЩЕЕ УСТРОЙСТВО ДЛЯ СИСТЕМ УПРАВЛЕНИЯ, содержащее последовательно соединенные блок сигнатуры, интегратор с конденсатором в обратной связи, блок выделения модуля и блок умножения, о т л и ч а ющ е е с я тем, что, с целью уменьшения фазового запаздывания и повышения точности воспроизведения входного сигнала, в него введены логический блок, а также последовательно. соединенные сумматор и усилитель, выход которого соединен с вторым входом блока умножения, причем вход устройства является одновременно входом для блока сигнатуры, сумматора и логического блока, выход которого соединен параллельно с конденсатором интегратора и является

его вторым входом, выход блока умножения соединен с вторым входом сумматора и является выходом устройства.

2. Устройство по п.1, о т л иФ ч а ю щ е е с я тем, что логический блок выполнен в виде последовательно соединенных дискриминатора и управляющего транзистора, причем вход дискриминатора соединен с входом логического блока, а его выход является выходом управляющего транзистора.

1076870

Изобретение относится к элементам . автоматики и может быть использовано в качестве корректирующего, устройства в линейных и нелинейных системах автоматического регулирования и управления. 5

Известно линейное корректирующее устройство, содержащее сопротивление, вход которого является входом устройства, а выход через параллельно соединенные операционный усилитель, сопротивление и конденсатор подключен к выходу устройства 1g.

Такое устройство обеспечивает амплитудное подавление с наклоном

20 дБ/дек, начиная от частоты

1 и>д= вЂ, где Т вЂ” постоянная времени . устройства.

Наиболее близким к предлагаемому по технической сущности является псевдолинейное корректирующее уСтройство, содержащее последовательно соединенные блок сигнатуры, интегратор, выполненный на операционном усилителе с конденсатором в обратной связи, блок выделения модуля, блок умножения, выход которого является выходом устройства, а его второй вход соединен с входами устройства и блока сигнатурыХЦ

Известное устройство позволяет 30 получить ослабление амплитуды с ростом частоты без существенного изменения фазы выходного сигнала. Однако оно искажает форму входного сигнала, а фаэовая характеристика выходного 35 сигнала отстает от фазы входного сигнаЛа в области частоты среды приблизительно на 20-30 град. При применении такого устройства в высокоточных системах автоматического 40 управления (например, при использовании в роботах-манипуляторах) перечисленные недостатки сужают область его применения, снижают точность устройства и быстродействие системы в целом.

Цель изобретения — уменьшение величины фазового запаздывания и повышение точности воспроизведения формы входного сигнала.

Поставленная цель достигается тем, что в устройство введены логический блок, а также последовательно соединенные сумматор и усилитель, выход которого соединен с вторым входом блока умножения, причем вход устройства является одновременно входом для блока сигнатуры, сумматора и логического блока, выход которого соединен параллельно с конденсатором интегратора и является его вторым 60 входом, выход блока умножения соединен с вторым входом сумматора и является выходом устройства.

Логический блок выполнеН в виде последовательно соединенных дискри- 65 минатора и управляющего транзистора, причем вход дискриминатора соединен. с входом логического блока, а его выход является выходом управляющего транзистора.

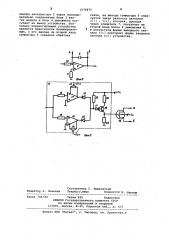

На фиг.1 представлена блок-схема псевдолинейного корректирующего устройства; на фиг.2 — принципиальная схема интегратора, на фиг.3 схема логического блока.

Устройство содержит блок 1 сигнатуры, интегратор 2, блок 3 взятия модуля, блок 4 умножения, логический блок 5, сумматор 6 и усилитель 7

Интегратор 2 состоит иэ первого операционного усилителя 8, конденсатора 9 и первого и второго резисторов 10 и 11.

Логический блок 5 состоит иэ дискриминатора 12, содержащего первый и второй переменные резисторы

13 и 14, третьего и четвертого резисторов 15 и 16, второго и третьего операционных усилителей 17 и 18, диодов 19-?1, пятого, шестого и седьмого резисторов 22-24, транзистора 25 и управляющего транзистора 26.

На фиг. 1-3 обозначены входной

Х(1) и выходной У() сигналы устройства, второй вход а и 6 интегратора напряжения смещения Б „, и

U соответственно на операционных усилителях и транзисторах 25 и 26.

Устройство работает следующим образом.

Вхоцной (корректируемый) сигнал X(t;) одновременно поступает на вход блока 1 сигнатуры, на один иэ входов сумматора 6 и на вход логического блока 5. Выходной сигнал с блока 1 сигнатуры поступает на интегратор 2, выполненный на операционном усилителе с конденсатором в обратной связи, который вносит запаздывание по фазе.

Для того, чтобы фаза сигнала r(t) совпала с фазой входного сигнала

X(), логический блок 5 реагирует на нулевой входной сигнал таким образом, что при переходе сигнала

X(t) через нуль на выходе дискриминатора логического блока 5 (фиг.3) появляется нулевой сигнал, который отпирает транзистор 25, вследствие чего открывается транзистор 26, который замыкает контакты и и 5 . .При замыкании этих контактов (фиг.2) происходит разряд конденсатора 9, после чего на входе логического блока появляется ненулевой сигнал, запирающий транзисторы 25 и 26 и размыкающий контакты а и Ь . Сразу же начинается заряд конденсатора. В результате фаза входного сигнала Х() и фаза сигнала на выходе интегратора 2 практически совпадут. Сигнал с

1076870

Составитель Г. Вышковский

Техред О.неце Корректор М. шароши

Редактор А. Лежнина

Заказ 746/44 Тираж 842 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4 выхода интегратора 2 через последовательно соединенные блок 3 взятия модуля и блок 4 умножения поступает на выход устройства. Поскольку корректирующее устройство является практически безынерцион- з ным, с его выхода на второй вход сумматора 6 заведена обратная связь, на выходе сумматора 6 образуется такая разность сигналов

Х(с) - Y(t), которая, проходя через усилитель 7, поступает на второй вход блока 4 умножения 4, в результате форма выходного сигнала Y(t) повторяет форму входного сигнала X(t) устройства.