Устройство для вычисления функции ( @ - @ )/ @

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ (х-у)/у, содержащее два регистра, два сумматора-вычитателя , блок анализа знака разности и блок управления, содержащий генератор импульсов, элемент И, элемент ИЛИ, вычитающий счетчик, дешифратор нуля, триггер, элемент НЕ и элемент задержки, причем выход генератора импульсов соединен с первым входом элемента И, второй вход и выход которого соединены соответственно с выходом триггера и входом элемента задержки, выход которого соединен с входом вычитающего счетчика, выход которого через дешифратор нуля соединен с первым входом элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом элемента НЕ и входом установки в нуль триггера. вход установки в единицу которого соединен с входом элемента НЕ и выхо дом равенства величин блока анализа знака разности, выход элемента И блока управления соединен с тактовыми входами первого и второго регистров, выход элемента задержки соединен с тактовыми входами первого и второго сумматоров-вычитателей, управляющие входы которых соединены с выходом знака разности блока анализа знака разности, первый и второй входы которого соединены соответственно с выходами первого и второго сумматоров-вычитателей, входы начальной установки которых соединены соответственно с входами первого и второго аргументов устройства , выход второго регистра соединен с входом первого сумматоравычитателя , вход начальной установки второго регистра соединен с входом второго аргумента устройства, отличающееся тем, что, с целью расширения области применения за счет возможности вычисления относительной погрешности (-у)/ ij, выход знака разности блока анализа знака разности соединен с информационньм входом первого регистра,выход которого соединен с выходом устройства, выход второго регистра соединен с информационным входом второго сумматора-вычитателя.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (111

3(59 G 06 F 15/31

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3404884/18-24 (22) 11 ° 03.82 (46) 28.02.84. Бюл. 9 8 (72) Н.С. Анишин и A.Ñ. Анишин (71) Кубанский государственный университет (53) 681.325 (088.8) (56) 1. Авторское свидетельство СССР

Р 922760, кл. G 06 F 15/31, 1980.

2. Авторское свидетельство СССР

9 744595, кл. G 06 F 15/31, 1976 (прототип). (54) (57) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕHEI фУИКЦИИ (x-y)/y, содержащее два регистра, два сумматора-вычитателя, блок анализа знака разности и блок управления, содержащий генератор импульсов, элемент И, элемент ИЛИ, вычитающий счетчик, дешифратор нуля, триггер, элемент НЕ и элемент задержки, причем выход генератора импульсов соединен с первым входом элемента И, второй вход и выход которого соединены соответственно с выходом триггера и входом элемента задержки, выход которого соединен с входом вычитающего счетчика, выход которого через дешифратор нуля соединен с первым входом элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом элемента НЕ и входом установки в нуль триггера, вход установки в единицу которого соединен с входом элемента НЕ и выхо дом равенства величин блока анализа знака разности, выход элемента И блока управления соединен с тактовыми входами первого и второго регистров, выход элемента задержки соединен с тактовыми входами первого и второго сумматоров-вычитателей, управляющие входы которых соединены с выходом знака разности блока анализа знака разности, первый и второй входы которого соединены соответственно с выходами первого и второго сумматоров-вычитателей, входы начальной установки которых соединены соответственно с входами первого и второго аргументов устройства, выход второго регистра соединен с входом первого сумматоравычитателя, вход начальной установки второго регистра соединен с входом второго аргумента устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения за счет возможности вычисления относительной погрешности((-ч)/(1, выход знака разности блока анализа знака разности соединен с информационным входом первого регистра,выход которого соединен с выходом устройства, выход второго регистра соединен с информационным входом второго сумматора-вычитателя.

1076912

Изобретение относится к цифровой вычислительной технике и может быть использовано в цифровых изме рительных приборах и системах обработки информации.

Известен цифровой функциональ ный преобразователь, содержащий сумматоры-вычитатели, регистры, блок хранения констант, блок анализа и блок управления (1) .

Недостатком данного устройства является невозможность вычисления значения относительной погрешности.

Наиболее близким к предлагаемому является цифровой функциональный преобразователь, содержащий блок ана-t5 лиза, по два сумматора-вычитателя и регистра сдвига, блок управления, причем первый и второй выходы блока управления соединены с управляющими входами каждого из регистров сдвига 2П и с тактовыми входами каждого из сумматоров-вычитателей соответственно, выходы которых поданы на входы блока анализа, а его два выхода соединены с сумматорами-вычитателями и блоком управления. Каждый из двух входов (переменные х и ) связан с входами занесения сумматоров и регистров сдвига. Этот преобразователь позволяет находить частное от . деления суммы квадратов входных переменных на их сумму

z у )/(x q )

Недостатком известного устройства 35 является ограниченность области применения из-за невозможности вычисления частного от деления разности двух чисел на одно из них (относительной погрешности). 40

Цель изобретения — расширение области применения устройства за счет воэможности вычисления относительной погрешности (Х- g ) / Ч

Поставленная цель достигается тем, что в устройстве для вычисления функции (x- g) / у, содержащем два регистра, два сумматора-вычитате ля, блок анализа знака разности и блок управления, содержащий генератор импульсов, элемент И, элемент

ИЛИ, вычитающий счетчик, дешифратор нуля, триггер, элемент HE и элемент задержки, причем выход генератора импульсов соединен с первым входом элемента И, второй вход и выход которого соединены соответственно с выходом триггера и входом элемента задержки, выход которого соединен с входом вычитающего счетчика, выход которого через дешифратор нуля сое- 60 динен с первым входом элемента ИЛИ, второй вход и выход которого соединен соответственно с выходом элемента НЕ и входом установки в нуль триггера, вход установки в единицу 65 которого соединен с входом элемента HE и выходом равенства величин блока анализа знака разности, выход элемента И блока управления соединен с тактовыми входами первого и второго регистров, выход элемента задержки соединен с тактовыми входами первого и второго сумматоров-вычитателей, управляющие входы которых соединены с выходом знака разности блока анализа знака разности, первый и второй входы которого соединены с выходами первого и второго сумматоров-вычитателей, входы начальной установки которых соединены с входами соответственно первого и второго аргументов устройства, выход второго регистра соединен с информационным входом первого сумматора-вычитателя, вход начальной установки второго регистра соединен с входом второго аргумента устройства, выход знака разности блока анализа знака разности соединен с информационным входом первого регистра, выход которого соединен с выходом устройства, выход второго регистра соединен с информационным входом второго сумматора-вычитателя.

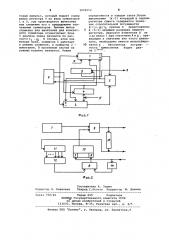

На фиг.1 представлена блок-схема предлагаемого устройства, на фиг.2— блок-схема блока управления.

Устройство содержит сумматорывычитатели 1 и 2, регистры 3 и 4, блок 5 анализа знака разности и блок

6 управления, который включает генератор 7 импульсов, элемент И 8, элемент ИЛИ 9, элемент 10 задержки,вычитающий счетчик 11, дешифратор 12 нуля, триггер 13 и элемент HE 14.

К работе устройства имеют отношение следующие итеративные формулы: где = 1,2,..., (И-1} — номер итерации, и — число разрядов величин

Х иЦ.

Предлагаемое устройство работает следующим образом.

Перед началом работы во второй регистр 4 и во второй сумматор-вычитатель 2 заносится операнд а в первый сумматор 1 — Х . Включается генератор тактовых импульсов в блоке

6 управления. С выхода элемента И 8 блока 6 тактовый импульс поступает на тактовые входы регистров 3 и 4 и сдвигает их содержимое на один разряд вправо (регистр 4) и влево (регистр 3). Затем с выхода элемента 10 задержки блока 6 поступает задержанный во времени этот же так1076912

+ ив.1

Составитель А. Зорин

Редактор H. Ковалева Техред С,Легеэа Корректор M. Демчик

Тираж 699 Подписное

BHHHITp Государственного, комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 750/46

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4 товый импульс, который подает содер жимое регистра 4 на вход сумматоров

1 и 2, где производится вычитание или сложение его с предыдущими значениями сумматоров. Причем выбор сложения или вычитания для конкретного сумматора осуществляет блок

5 анализа знака разности по разности x - . В случае, если она

3 меньше нуля, сумматор 1 работает в режиме сложения, а сумматор 2 вычитания. В противном случае их режимы взаимно меняются. Режим определяется в каждом такте. После выполнения (tl-1) итераций в первом регистре сдвига содержится значение относительной погрешности (х- ф (g, причем z представлено в (о-1) младших разрядах первого регистра. Диапазон изменения Z от

2 до минус 1.При значениях k u g. приводящих к значению вне этого диапаэона, необходимо ввести масштабирование Ч . Абсолютная погрешность вычисления будет равна 2-(> il