Мостовой инвертор

Иллюстрации

Показать всеРеферат

1. МОСТОВОЙ ИНВЕРТОР, содержащий силовые транзисторы, блок управления, выходы которого связаны с входными цепями указанных транзисторов , датчики тока, выходы которых подключены к блокирующим входам блока управления, отличающийся тем, что, с целью повышения надежности путем исключения сквозных токов, во входные цеп:: силовых транзисторов последовательно включены входы соответствующих датчиков тока. а СЛ о О 00 О5

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

3(59 2

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЪСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ГО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3528800/24-07 (22) 30.12.82 (46) 28.02.84. Бюл. в 8 (72) В.к.овдин и В.Л.Хромушнн (53 ) 621. 314. 58 (088. 8) (56) 1. Ромаш Э.М. Транзисторные преобразователи в устройствах пита-. ния радиоэлектронной аппаратуры. М., "Энергия", 1975, с. 12, 13, рис.1-8.

2. Авторское свидетельство СССР

Э 521642, кл. Н 02 М 7/537, 1974..Я0„» 77036 А (54)(57) 1. МОСТОВОЙ HHBEPTOP, содержащий силовые транзисторы, блок управления, выходы которого связаны с входными цепями указанных транзисторов, датчики тока, выходы которых подключены к блокирующим входам блока управления, о т л и ч а юшийся тем, что, с целью повышения надежности путем исключения сквозных токов, во входные цег.:: силовых транзисторов последовательно включены входы соответствующих датчиков тока.

1077036

2, Инвертор по п.1, о т л и ч аю шийся тем, что в качестве

Изобретение относится к электротехнике и может быть использовано в силовых преобразователях.

Известен мостовой инвертор, содержащий силовые транзисторы, блок управления, выходы которого связаны с входными цепями указанных транзисторов. Для исключения сквозных токов во входные цепи силовых транзисторов включены дроссели с насыщающимися " сердечниками, обеспечивающие задержку включения очередного силового транзистора (11.

Недостатком этого инвертора является отсутствие автоматического регулирования времени задержки.

Наиболее близким к предлагаемому является мостовой инвертор, содержащий силовые транзисторы, блок управления, выходы которого связаны с входными цепями указанных транзисто- 2О ров, датчики тока, выходы которых подключены к блокирующим входам блока управления 2 .

Однако в указанном инверторе полностью сквозные токи не устраняются, 25 так как автоматическая задержка включения очередной пары транзисторов действует только до момента запирания одного иэ пары ранее включенных .транзисторов, время рассасывания из- gg быточных носйтелей которого меньшее.

Это снижает надежность инвертора.

Цель изобретения - повышение надежности инвертора путем полного исключения сквозных токов, 35

Указанная цель достигается тем, что в мостовом инверторе, содержащем силовые тра нэ исторы, блок упра вл ения, выходы которого связаны с входными цепями укаэанных транзисторов, дат- 40 чики тока, выходы которых подключены к блокирующим. входам блока управления, во входные цепи силовых транзисторов последовательно включены входы соответствующих датчиков тока.

В качестве датчиков тока могут быть использованы токовые трансформаторы.

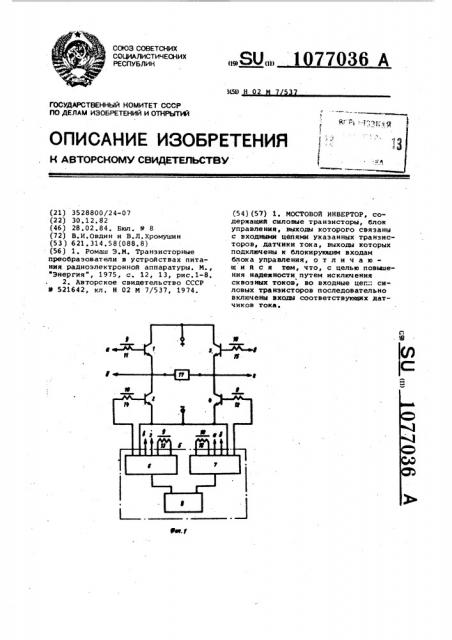

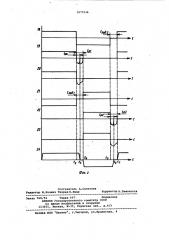

На фиг. 1 приведена электрическая схема мостового инвертора," на фиг.2- временные диаграммы.

Инвертор содержит силовые транзисторы 1-4, блок 5 управления,состоящий из узлов 6 и 7 формирователей импульсов и узла 8 управления, Трансформаторы 9 и 10 тока используются в 55 качестве датчиков тока, каждый транс/. датчиков тока используются токовые трансформаторы.

2 форматор тока имеет две первичных (входы датчиков тока )и одну вторичную обмотки (выход датчика тока l.

Первичные обмотки 11 и 12 трансформатора 9 предназначены для измерения токов баэ транзисторов 1 и 4 соответственно, а вторичная обмотка 13для передачй информации о базовых токах на один блокирующий вход формирователя 6 импульсов блока .5 управления. Первичные обмотки 14 и 15 трансформатора 10 предназначены для измерения токов баз транзисторов 2 и

3 соответственно, а вторичная обмотка 16 — для передачи информации о базовых токах на другой блокирующий вход формирователя 7 импульсов блока 5 управления. Нагрузка 17 подключена к выходным выводам.

Узлы 6 и 7 формирования импульсов имеют на входе схему совпадения и предоконечные каскады, воздействующие на силовые транзисторы. Узел 8 управления содержит задающий генератор.

На фиг.2 приведены временные диаграммы 18-24 соответственно напряжения на входах транзисторов 1 и 4, ба-. зовых токов транзисторов 1 и 4, тока через обмотку 13, йапряжения на входах транзисторов 2 и 3, базовых токов транзисторов 2 и 3, тока через обмотку 16, силового тока транзисторов 1-4.

Устройство работает следующим образом.

Предположим, что на базы транзисторов синхронной пары 1 и 4 подают- ся положительные управляющие импульсы 18 в момент времени .t Транзисторы 1 и 4 открыты и через них протекает ток 24. Транзисторы 2 и 3 второй синхронной пары закрыты. При смене полярности управляющих импульсоВ 18 с формирователя 7 импульсов в момент 11 через первичные обмотки

11 и 12 трансформатора 9 тока начинают протекать обратные токи 19 баз транзисторов 1 и 4 соответственно, что обеспечивает протекание импульса тока 20 во вторичной обмотке 13, длительность которого определяется максимальным временем рассасывания неосновных носителей tp базы одного из транзисторов 1 и 4 (например 1J

Этот импульс тока поступает в формирователь 6 импульсов, блокируя уп

„равляющий сигйал, чем и обеспечивае

1077036 задержку открывания Фз транзисторов 2 и 3. Сигнал блокировки снимается при уменьшении обратных токов 20 баэ практически до нуля в момент окончания процесса выключения транзистора 1. Ток 24 нагрузки через транзисторы 1 и 4 прерывается в мо-. мент окончания вр мени рассасывания в транзисторе 4.

Транзисторы 2 и 3 открываются при поступлении положительных управляющих импульсов 21 в момент эапирания транзистора 1. При смене полярности управляющих импульсов 21 с формирователя 6 импульсов через первичные обмотки 14 и l5 трансформатора 10 тока начинают протекать обратные токи

22 баз транзисторов 2 и 3 соответственно, что обеспечивает протекание импульса тока 23 во вторичной обмотке 16, дпительность которого определяется максимальным временем рассасывания неосновных носителей базы одного из транзисторов 2 и 3 (напри- ° мер 3 1.Этот импульс тока поступает в формирователь 7 импульсов, блокирует управляющий сигнал, чем и обеспечивает задержку открывания транзисторов 1 и 4. Сигнал блокировки снимается при окончании юепульсов токов 22 баэ транзисторов 2 и 3. Ток 24 нагрузки через транзисторы 2 и 3 прерывается в момент окончания времени рассасывания в транзисторе 2. В. результате ток 24 нагрузки имеет разрывы, t0 по времени равные разности времен рассасывания транзисторов 2,3 и 1,4 соответственно.

Таким образом, введение датчиков тока для измерения токов баэ дало 5 возможность использовать информацию о процессе рассасывания неосновных носителей в базах транзисторов для блокирования сигналов включения ранее выключенных силовых транзисторов до момента полного выключения ранее включенной пары силовых транзисторов, что и обеспечивает полное исключение сквозных токов в инверторе и повышения его надежности.

1077036

Составитель А.Селезнев ,Редактор М.Янович Техред О.Неце Корректор A. Зимокосов е е

Заказ 768/52 Тираж 667 . Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

М

Филиал ППП "Патент ", г,ужгород, ул.Проектная, 4