Цифровой анализатор спектра

Иллюстрации

Показать всеРеферат

ЦИФРОЮЙ АНАЛИЗАТОР СПЕ1СГРА , содержащий два квадратурных канала, каждый из которых содержит два фазовых детектора, подключенных по одному из входов к шине входных сигналов, по другому к генератору опорного сигнала в одном канале непосредственно , а в другом через фа .эосдвигающую на1|/2 цепь, выходы фазовых детекторов каждого канала соединены через последовательно соединенные аналого-цифровой преобразователь и входной сумматор с входом оперативного запоминающего устройства с установочным входом, выход которого подключен к первым вхоцаал двух перемножителей своего канала ,выходы первых перемножителей подключены к второму входу сумматора своего канала, а их вторые входы соединены вместе, выходы вторых перемножителей подключены к третьим входам сумматоров противоположных каналов, а их вторые выходы также соединены вместе, выходы сумматоров каждого канала соединены через блоки возведения в квадрат с входами блока суммирования, выход которого через блок извлечения квадратного корня подключен к выходу устройства, а также содержит синусное и косинусное постоянные запоминающие устройства , отличающийся тем, что, с целью повышения разрешающей способности при изменении днагаздна анализируемых частот, в него введены дополнительный сумматор, вычитатель, два дополнительных оперативных запоминающих устройства с установочными входами и четыре дополнительных перемножителя , причем выход вычитателя подключен к первому дополнительному оперативному запоминающему .устройству с .установочным входом и через первый дополнительный перемножитель соединен с первым входом вычитателя, а через второй дополнительный перемножитель соединен с входом дополнительного сумматора, выход дополнительного сумматора (Л подключен к второму дополнительному оперативному запоминающему устс ройству с установочным входом и через третий дополнительный перемножитель соединен с вторым входом вычитателя , а через четвертый дополнительный перемножитель соединен с вторым входом дополнительного сумматора , вторые входы первого и четVI вертого дополнительных перемножитетелей объединены и подключены к выэо ходу косинусного запоминающего :о устройства, вторые входы второго и третьего дополнительных перемножи4 ЭО телей объединены и подключены к 6ыхрду синусного запоминающего устройства , выход первого дополнительного оперативного запоминающего устройства с установочным входом подключен к соединенным вместе вторым входам первых перемножителей, а выход второго дополнительного оперативного запоминающего устройства с установочным входом подключен к соединенным вместе вторим входам вторых перемножителей .

(19) (11) СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

3(51) 0 01 Н 23 16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 3528730/18-21 (22) 24 ° 12.82 (46) 07.03.84. Бюл. )) 9 (72) В.И.Лнтюк и Т.A.Ëèòþê (71) Таганрогский радиотехнический институт им. В.Д.)<алмыкова (53) 621.317.757(088.8) (56) 1. Авторское свидетельство СССР

)) 653575, кл. <; 01 Н 23/16, 1979.

2. Авторское свидетельство СССР

)) 428389, кл. 0 06 Y 15/36, 1974 (прототип). (54).(57) ЦИФРОВОИ АНАЛИЗАТОР СПЕКТРА, содержащий два квадратурных канала, каждый из которых содержит два фазовых детектора, подключенных по одному иэ входов к шине входных сигналов, по другому к генератору опорного сигнала в одном канале непосредственно, а в другом через фа,эосдвигающую на и /2 цепь, выходы фал эовых детекторов каждого канала соединены через последовательно соединенные аналого-цифровой преобразователь и входной сумматор с входом оперативного запоминающего устройства с установочным входом, выход которого подключен к первым входам двух перемножителей своего канала, выходы первых перемножителей подключены к второму входу сумматора своего канала, а их вторые входы соединены вместе, выходы вторых перемножителей подключены к третьим входам сумматоров противоположных каналов, а их вторые выходы также соединены вместе, выходы сумматоров каждого канала соединены через блоки возведения в квадРат с входами блока суммирования, выход которого через блок извлечения квадратного корня подключен к выходу устройства, а также содержит синусное и косинусное постоянные запоминающие устройст. ва, отличающийся тем, что, с целью повышения разрешающей способности при изменении диагазс)на анализируемых частот, в него введены дополнительный сумматор, вычитатель, два дополнительных оперативных запоминающих устройства с установочными входами и четыре дополнительных перемножителя, причем выход вычитателя подключен к первому дополнительному оперативному запоминающему, устройству с .установочным входом и через первый дополнительный перемножитель соединен с первым входом вычитателя, а через второй дополнительный перемножитель соединен с входом дополнительного сумматора, Е выход дополнительного сумматора подключен к второму дополнительному оперативному запоминающему устройству с установочным входом и че- %sees рез третий дополнительный перемножитель соединен с вторым входом вычитателя, а через четвертый дополнительный перемножитель соединен с вторым входом дополнительного сумматора, вторые входы первого и четвертого дополнительных перемножитетелей объединены и подключены к вы. ходу косинусного запоминающего устройства, вторые входы второго и третьего дополнительных перемножителей объединены и подключены к выходу синусного запоминающего устройства, выход первого дополнительного оперативного запоминающего устройства с установочным входом подключен к соединенным вместе вторым входам,ф) первых перемножителей, а выход второго дополнительного оперативного запоминающего устройства с установочным входом подключен к соединенным вместе вторым входам вторых перемножителей.

1078348

Изобретенйе относится к цифровой радиоиэмерительной технике и может быть использовано для построения спектроаналиэаторов, перекрывающих заданные частотные диапазоны, кото- рые могут изменяться в широких пределах.

Известен цифровой анализатор спектра, состоящий иэ двух последовательно соединенных рециркуляционных каскадов со сдвигом частот в целях обратных связей P1) .

Однако увеличение диапазона анализируемых частот в цифровом анализа торе спектра приводит к изменению разрешающей способности и для поддержания ее постоянства требуется увеличивать количество цифровых ячеек.

Наиболее близким по сущности к изобретению является устройство содержащее блок образования квадратурных составляющих, содержащий два фазовых детектора, которые соединены по одним входам с шиной входных сигналов, а по другим входам подключены к генератору опорного сигнала в одном канале непосредственно, а в другом через фазосдвигающую на /2 цепь, выходы фазовых детекторов блока образования квадратурных составляющих через аналого-цифровые преобразователи (AU/I) соединены с соответствующими входами сумматоров своих каналов, выход каждого из которых соединен через оперативное запоминающее устройство {ОЗУ) с первыми входами блока перемножения комплексных чисел, к вторым входам которого подключено постоянное запоминающее устройство (ПЗУ), а выходы блока перемножения комплексных чи-. сел соединены прямыми и перекрестными связями с соответствующими входами сумматоров своего и противоположного каналов и через блоки возведения в квадрат своих каналов соединены с входами блока суммирования и через блок извлечения корня квад.ратного подключены к. выходу устройства, причем все блоки соединены с синхронизатором (2) .

Известное устройство обладает тем недостатком, что,при изменении диапазонов анализируемых частот из.меняется разрешающая способность и для ее сохранения требуется изменять затраты оборудования.

Цель изобретения - повышение разрешающей способности при изменении диапазона анализируемых частот., Поставленная цель достигается тем, что в устройство, содержащее два квадратурных канала, каждый иэ которых содержит два фазовых детектора, подключенных по одному из входов к шине входных сигналов, а по другому — к генератору опорного сигнала в одном канале непосредственно, а в другом через фаэосдвига ющую на Я /2 цепь, выходы фазовых детекторов каждого канала соединены через последовательно соединенные аналого-цифровой преобразователь и входной сумматор с входом оперативного запоминающего устройства с установочным входом, выход которого

10. подключен к первым входам двух перемножителей своего канала, выходы первых .перемножителей подключены к второму входу сумматора своего канала, а их вторые входы соединены вместе, выходы вторых перемножителей подключены к третьим входам сумматоров противоположных каналов, а их вторые входы также соединены вместе, выходы сумматоров каждого

20 канала соединены через блоки возведения в квадрат с входами блока суммирования, выход которого через блок извлечения квадратного корня подключен к выходу устройства, а также содержит синусное и .косинусное запоминающие устройства, введены дополнительный сумматор, вычитатель, два дополнительных оперативных запоминающих устройства с установочными входами и четыре дополнительных перемножителя, причем выход вычитателя подключен к первому дополнительному оперативному запоминающему устройству с установочным входом и через первый дополнительный пере35 множитель соединен с первым входом вычитателя, а через второй дополнительный перемножитель соединен с входом дополнительного сумматора, выход дополнительного сумматора

40 подключен к второму дополнительному оперативному, запоминающему устройству с установочным входом и через третий дополнительный перемножитель соединен с вторым входом вычитателя, а через четвертый дополнительный перемножитель сбединен с вторым входом дополнительного сумматора, вторые входы первого и четвертого дополнительных перемножителей объединены и подключены к выходу косинусного запоминающего устройства, вторые входы второго и третьего дополнительных перемножителей объединены и подключены к выходу дополнительных перемножителей объединены

55. и подключены к выходу синусного запоминающего устройства, выход первого дополнительного оперативного запоминающего устройства с установочным входом подключен к соединенным щ вместе вторым входам первых перемножителей, а выход второго дополнительного оперативного запоминающего устройства с установочным входом подключен к соединенным вместе вторым входам вторых перемножителей.

1078348

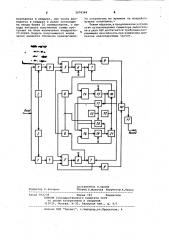

На чертеже изображена структурная схема цифрового анализатора спектра.

Цифровой анализатор спектра содержит два квадратурных канала, 5 каждый иэ которых содержит два фазовых детектора 1, подключенных по одному из входов к шине входных сигналов, а по другому к генератору 2 опорного сигнала в одном канале 10 непосредственно, а в другом через фазосдвигающую на 7 /2 цепь 3, выходы фазовых детекторов 1 каждого канала соединены через последовательно соединенные аналого-цифровой !5 преобразователь (ЛЦП ) 4 и выходной сумматор 5 с входом оперативного запоминающего устройства ОЗУ) б с установочным входом, выход которого подключен к первым входам двух первых перемножителей 7 своего канала, выходы первых перемножителей 7 подключены к второму входу сумматора 5 своего канала, а их вторые входы соединены вмЬсте, выходы вторых перемножителей 8 подключены к третьим входам сумматоров 5 противоположных каналов, а их-вторые входы также соединены вместе, выходы сумматоров 5 каждого канала соединены через блоки 9 возведения в квадрат 3О с входами блока 10 суммирования, выход которого через блок 11 извлечения квадратного корня подключен к выходу устройства, а также содержит сину иое 12 и косинусное 13 пос- 35 тоянные запоминающие устройства (ПЗУ), выход вычитателя 14 подключен к первому дополнительному оперативному запоминающему устройству 15 с установочным входом и через первый дополнительный перемножитель 16 соединен с первым входом дополнительного вычитателя 14, а через второй дополнительный перемножитель 17 соединен с Входом дополнительного сумма 45 тора 18, выход дополнительного сумматора 18 подключен к второму дополнительному оперативному запоминающему устройству 19 с установочным входом и через третий дополнительный перемножитель 20 соединен с вторым входом вычитателя 14, а через четвер- тый дополнительный перемножитель 21 соединен с вторым входом дополнительного сумматора 18, вторые входы первого 16 и четвертого 21 дополни- тельных перемножителей объединены и подключены к выходу косинусного запоминающего устройства 13, вторые входы второго 17 и третьего 20 дополнительных перемножителей объеди- 60 нены и подключены к выходу синусного запоминающего устройства 12, выход первого дополнительного оперативного запоминающего устройства 15 с установочным входом подключен к соединенным вместе вторым входам первых перемножителей 7, а выход второго дополнительного оперативного запоминающего устройства 19 с установочным входом подключен к соединенным вместе вторым входам вторых перемножителей 8.

Устройство работает следующим образом.

Анализируемое колебание подается на первые входы фазовых детекторов 1, на вторые входы которых поступает с генератора 2 опорного сигнала колебание с частотой f в одном канале непосредственно а во втором со сдвигом на фазе íà (i/2.

ПолуЧающиеся на выходах фазовых детекторов 1 колебания в виде колебаний суммарной и раэностной частот фальтруются и колебания разностной частоты, соответствующие квадратурным составляющим модулирующего колебания, поступают на входы АЦП

Иэ выходных сигналов AIJII 4 в нача-. ле каждого интервала длительности берутся выборки, амплитуда которых преобразуется в двоичный код и затем запоминается на весь интервал длительности. Каждая выборка поступает на вход сумматора 5 своего канала, на вторых и третьих входах каждого из которых находятся в первый интервал времени нули. С выхода сумматора 5 действительного канала выборка сигнала записывается в ОЗУ 6 действительного канала, а с выхода сумматора 5 мнимого канала выборка сигнала записывается в ОЗУ б мнимого канала.

Перед началом второго отсчета выборки сигнала умножаются в перемножителях 7 и 8 на коды чисел, которые поступают с выходов ОЗУ 15 и 19. Одновременно коды чисел поступают на входы перемножителей 16 и

17 с выхода ОЗУ 15, а на перемножители 20 и 21 — с выхода ОЗУ 19. На другие входы еремножителей 16 и 21 поступает постоянный код числа с выхода косинусного ПЗУ 13, а на другие входы перемножителей 17 и 20 код числа с выхода синусного ПЗУ. 12.

Кольцо, образованное обратными и перекрестными связями и содержащее сумматор 18, вычитатель 14, ОЗУ 15 и 19, перемножители 16, 17, 20 и 21 и ПЗУ 12 и 13, представляет собой генератор цифровой комплексной экспоненты с шагом дискретности Tg и амплитудой равной r. Этот генератор и позволяет осуществлять сдвиг точки синфазности во времени эа счет поступления отсчетов комплексной экспоненты на вторые входы перемножителей 8 и 7.

С выходов сумматоров 5 образующиеся коды чисел поступают на блоки 9

1078348

Составитель A.Îðëîâ Гехред T.Ìàòî÷êà Корректор A.Òÿñêî

Редактор A.Êoýoðèç

Заказ 952/39 Тираж 711 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушокая наб., д. 4/5

Филиал ППП "Патент", r.Óæãîðîä,óë.Ïðîåêòíàÿ, 4 возведения в квадрат, где числа возводятся в квадрат и далее поступают на входы блока 10 суммирования, с выхода которого полученные суммы поступают на блок извлечения квадратного корня. Модуль получающихся кодов чисел является откликом предлагаемоro устройства -во времени на воздействующее колебание. °

Таким образом, в предложенном устройстве путем введения сумматора,вычитателя .и двух ОЗУ достигает ся требуемая ра эрешающая способность при изменении диапазона анализируемых частот.