Устройство для контроля качества канала связи

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ, КАЧЕСТВА КАНАЛА СВЯЗИ, содержащее компаратор, первый вход которого соединен с выходом инт егратора, а второй вход соединен с первым выходом .синхронизатора, второй выход кото-: рого соединен с входом элемента задержки , счетчик информационных символов , первый вход которого соединен с выходом компаратора, а второй вход соединен с выходом элемента задержки , блок деления кодов и блок сравнения , отличающееся тем, что, с целью повышения точности контроля , в него введены блок вычитания, блок памяти и элемент И, причем первый вход блока вычитания соединен с выходом счетчика информационных символов, второй вход соединен с вторым выходом синхронизатора, а первый вход элемента И соединен с выходом блока вычитания и первым входом блока сравнения, выход которого подключен к второму входу элемента И, выход которого подключен к первому входу блока деления кодов, g второй вход которого, второй вход (Л блока сравнения и третий вход блока вычитания соединены с соответствующими выходами блока памяти. &

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTGPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (211 3429735/18-09 (22) 26.04.82 (46) 07.03.84, Бюл. Р 9 (72) Н.A ° Tðoøêoâ, В.В.Хворенков, И.З.Климов и И.N..Марков (71) Ижевский механический институт (531 621. 395. 64 (088. 8) (56) 1. Авторское свидетельство СССР

Р 815928, кл. Н 04 В 3/46, 1979, 2. Авторское свидетельство СССР

Р 836801, кл. Н 04 В 3/46, 1979 (прототип) (54)(57) УСТРОЙСТВО @JIB КОНТРОЛЯ, КАЧЕСТВА КАНАЛА СВЯЗИ, содержащее компаратор, первый вход которого соединен с выходом интегратора, а второй вход соединен с первым выходом ,синхронизатора, второй выход кото- рого соединен с входом элемента задержки, счетчик информационных символов, первый вход которого соединен

3(5D Н 0 4 В 3 / 4 6 ; Н 0 4 ), 1 1 /0 8 с выходом компаратора, а второй вход соединен с выходом элемента задержки, блок деления кодов и блок сравнения,отличающее cя тем, что, с целью повышения точности контроля, в него введены блок вычитания, блок памяти и элемент И, причем первый вход блока вычитания соединен с выходом счетчика информационных символов, второй вход соединен с вторым выходом синхронизатора, а первый вход элемента И соединен с выходом блока вычитания и Первым входом блока сравнения, выход которого подключен к второму входу элемента И, выход которого подключен к первому входу блока деления кодов, Я второй вход которого, второй вход блока сравнения и третий вход блока вычитания соединены с соответствующими выходами блока памяти. С:

1078641

Изобретение относится к радиотехнике и может быть исполь овано в системах передачи данных.

Известно устройство контроля качества канала связи, содержащее последовательно соединенные интегратор, компаратор, регистр сдвига, счетчик, выход которого подключен к первым входам двух элементов сравнения, выходы которых подключены к двум входам элемента ИЛИ, а также хронизатор выходы которого подключены соответственно к второму входу компаратора и вторым входам элементов сравнения, а дополнительный выход подключен к тактовому входу регистра сдвига (1) .

Однако это устройство не позволяет выявить количество ошибок на заданном интервале наблюдения, что снижает точность и эффективность контроля.

Наиболее близким по технической сущности к предлагаемому является устройство для контроля качества канала связи, содержащее компаратор, первый вход которого соединен с выходом интегратора, а второй вход соединен с первым выходом синхронизатора, второй выход которого соединен с входом элемента задержки и первый счетчик информационных символов, вход которого соединен с выходом компаратора, а второй вход соединен с выходом элемента задержки блок вселения кодов и блок сравнения, при этом второй выход синхронизатора подключен к вторым входам первого и второго элементов сравнения, выход каждого из которых подключен к соответствующим входам элемента ИЛИ, счетчик интервалов анализа и последовательно соединенные счетчик ошибок, блок деления кодов и блок регистрации, при этом выход элемента

ИЛИ соединен с входом ошибок, а второй вход синхронизатора соединен с вторым входом блока регистрации и с входом счетчика интервалов анализа выход которого соединен с вторым входом блока деления кодов (2).

Однако устройство не позволяет получить информацию об уровне помех на каждом интервале наблюдения, что снижает точность и эффективность контроля.

Цель изобретения — повышение точ ности контроля качества канала связи.

Поставленная цель достигается тем, что в устройство для контроля качества канала связи, содержащее компаратор, первый вход которого соединен с выходом интегратора, а второй вход соединен с первым выходом синхронизатора, второй выход которого соединен с входом элемента задержки, счетчик информационных символов, первый вход которого соединен с выходом компаратора, а в оой вход соединен с выходом элемента задержки, блок деления кодов и блок сравнения, введены блок вычитания, блок памяти и элемент И, причем первый вход блока вычитания соединен с выходом счетчика информационных символов, второй вход соединен с вторым выходом синхронизатора, а первый вход элемента

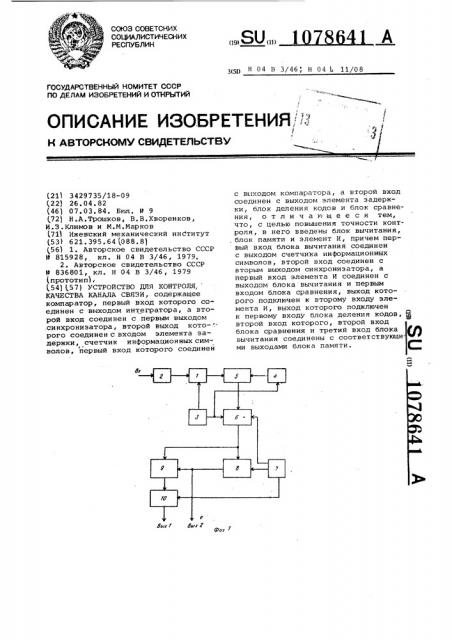

И соединен с выходом блока вычитания и первым входом блока сравнения, выход которого подключен к второму входу элемента И, выход которого подключен к первому входу блока деления кодов, второй вход которого, второй вход блока сравнения и тре$5 тий вход блока Вычитания соединены с соответствующими выходами блока памяти, На фиг. 1 приведена структурная электрическая схема устройства для контроля качества канала связи; на фиг. 2 — временные диаграммы, поясняющие работу устройства.

Устройство содержит компаратор 1, первый вход которого соединен с выходом интегратора 2, второй вход с первым выходом синхронизатора 3, .а второй выход которого соединен с входом элемента 4 задержки, счетчик

5 информационных символов, первый вход которого соединен с выходом

30 компаратора 1, а второй вход — с выходом элемента 4 задержки, блок

6 Вычитания, блок 7 памяти, блок 8 сравнения, первый вход которого соединен с выходом счетчика 5 информаЗ5 ционных символов, второй вход которого подключен к второму выходу синхронизатора 3, элемент И 9, выход которого соединен с первым входом блока 10 деления кодов.

Устройство работает следующим образом.

На вход интегратора 2 поступает аддитивная смесь бинарного сигнала с шумом (фиг. 2О). Интегрированное

45 напряжение фиг. 25)поступает на компаратор 1, который с определенной частотой опрашивается сигналом с выхода синхронизатора 3 (фиг. 2)).

Если во время опроса сигнал с интегратора 2 превышает порог, то вырабатывается сигнал (фиг. 2g), который записывает единицу в младший разряд счетчика 5 информационных символов (фиг. 2 ). Состояние счетчика М > (для примера приведено 3 разряда (фиг. 20,8,Х ), где М Х вЂ” вес принятой двоичной последовательности за N отсчетов, в течение которых производится анализ состояния канала связи, анализируется с помощью блока 6 вычитания. Число отсчетов N выбирается в зависимости от необходимого интервала наблюдения. Блок 6 вычитания опрашивается сигналом с выхода синхронизатора 1 (фиг. 2 P) определяющего временные соотношения работы

1078641

ВНИИПИ Заказ 986/53 . Тираж 635 Подписное

Филиал ППП "Патент ", r. Ужгород, ул. Проектная, 4 устройства. Этим же сигналом, задержанным на время срабатывания блока

6, производи т ся опрос счетчика 5 (фиг. 2и) . На второй вход блока 6 вычитания подается значение W — априорно известного среднестатического 5 веса информационной последовательности за Ч отсчетов (фиг. 2k,л,М), например, в приведенной временной диаграмме Ч = 4, информация представлена в двоичном коде тремя разряда- 1() ми и постоянно хранится на выходе 7 памяти после включения устройства.

Результаты вычитания поступают на блок 8 сравнения и на входы элемента И 9 (,фиг. 2 g, О). На рисунке

15 (фиг. 2 q, p) условно показано два

Рладших разряда выхода вычитания.

Пороговые значения хранятся в блоке

7 памяти. Если значение разности превышает один из порогов, то вырабатывается сигнал ошибки 8 и одновременно опрашивается элемент И 9.

Например, в блоке памяти пороговые значения (W-Wg) = 000 и (W-Wg) = 010 (В двоичном коде ), Резуль та Вычита ния, поступивший на блок 8 сравнения, в данном случае не превышает заданные пороги, поэтому сигнал ошибок вырабатываться не будет, и и нформация с выхода блока 6 вычитания не пройдет на вход блока 10 деления кодов изза отсутствия разрешаюшего сигнала для элемента И 9. В противном случае информация с выхода блока 6 вычитания поступит на вход блока 10 деления кодов, на второй вход которого подается значение числа отсчетов N, которое хранится в блоке 7 памяти в двоичном коде. В результате на выходе блока 10 получается код величины частости ошибок согласно формуле (W - W )УИ..

М

Таким образом, использование предлагаемого устройства позволяет количественно оценивать уровень помех на каждом интервале наблюдения, что повышает точность и эффективность контроля качества канала связи.