Устройство для формирования кодовых описаний изображений объектов

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ КОДОВЫХ ОПИСАНИЙ ИЗОБРАЖЕНИЙ ОБЪЕКТОВ, содержащее первую группу элементов ИЛИ, одни входы которых являютса входами первой группы устройства , а выходы соединены с одними входами сумматора, другие входы которого подключены к регистрам сдвига, блок сравнения, соединенный с регистрами сдвига, с сумматором , с первым элементом задержки, подключенным к второму элементу задержки, и с другими входами элементов ИЛИ первой группы, группу триггеров, входы которых являются другой группой входов устройства, а выходы подключены к одним входам , соответствующих элементов И первой группы, другие входы которых соединены с сумматором и с вторым элементом задержки, и элемент ИЛИ, отличающе-ес я тем, что, с целью повышения точности устройства , оно содержит вторую группу элементов И, входы которых соединены с первым элементом задержки од с сумматором, подключенным к блоку сравнения, а выходы соединены с соответствующими регистрами сдвига, третий элемент задержки, подключенный к первому элементу задержки и к другим входам элементов ИЛИ первой группы, элемент И, входы которого соединены с первым элементом задержки и с выходом сумматора , третью группу элементов И, одни входы которых подключены к ВТО- 9 рому элементу задержки и к сумматоО ) ру, а выходы подключены к элемен-. ту ИЛИ, выход которого соединен с входами соответствующих элементов И первой группы, четвертый элемент задержки, подключенный к второму элементу задержки, триггер, входы которого соединены о элементом И и с четвертым элементом задержки, а выходы подключены к соответствующим элементам И первой и третьей групп, и вторую группу элементов ИЛИ i входы которых подключены к соответствующим элементгил И первой группы , а выходы являются группой выходов устройства.

СОКИ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) 01) 3(51) 6 06 К 9 36

1"

I т,: е „

ОПИСАНИЕ ИЗОБРЕТЕНИЯ ("

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

H ABTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 3543711/18-24 (22) 20.01.83 (46) 15.03.84. Бюл. 9 10 (72) Ю.И.Тормышев (71) Минский радиотехнический институт (53) 681.327.12(088.8) (56) 1. Авторское свидетельство СССР

9 734709, кл. G 06 F 15/34, 1980.

2. Патент Японии Р 55-41466, кл. G 06 К 9/00, ОП брик. 1980 (прототип). (54)(57) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ КОДОВЫХ ОПИСАНИЙ ИЗОБРЮКЕНИЙ

ОБЪЕКТОВ, содержащее первую группу элементов ИЛИ, одни входы которых являются входами первой группы устройства, а выходы соединены с однию входами сумматора, другие входы которого подключены к регистрам сдвига, блок сравнения, соединенный с регистрами сдвига, с. сумматором, с первым элементом задержки, подключенным к второму элементу задержки, и с другими входами элементов ИЛИ первой группы, группу триггеров, входы которых являются другой группой входов устройства, а выходы подключены к одним входам .соответствующих элементов И первой группы, другие входы которых соединены с сумматором и с вторым элементом задержки, и элемент ИЛИ, о т л и ч а ю щ е е с я тем, что, с целью повьиаения точности устройства, оно содержит вторую группу элементов И, входы которых соединены с первым элементом задержки и с сумматором, подключенным к блоку сравнения, а выходы соединены с соответствующими регистрами сдвига, третий элемент задержки, подклю.ченный к первому элементу задержки и R другим входам элементов ИЛИ первой группы, элемент И, входы которого соединены с первым элементом задержки и с выходом сумматора, третью группу элементов И, одни входы которых подключены к вто- Pg рому элементу задержки и к сумматору, а выходы подключены к элемен-. ту ИЛИ, выход которого соединен с входами соответствующих влемевтов И первой группы, четвертый элемент задержки, подключенный к второму элементу задержки, триггер, входы которого соединены с элементом И и с четвертым элементом задержки, а выходы подключены к соответствующим элементам И первой и третьей .групп, и вторую группу элементов ИЛИ входы которых подключены к соответствующим элементам И первой группы, а выходы являются группой вы ходов устройства.

1080162

Изобретение относится к автоматике и вычислительной технике, связанной с обработкой сигналов, получаемых при считывании чертежно-графических иэображений в режиме следящего преобразования, и может быть использовано как для повышения информативности считываемой информации, так и для формирования кодовых описаний,изображеннй, облегчающих последующий логический анализ сиг- 10 налов, а также в системах сброса и обработки телеметрической информации с целью устранения избыточности информации или повышения ее информативности и для,пороговой обработки сигналов по угловому параметру.

Известно устройство для формирования кодовых описаний изображений объектов, содержащее счетчики, соединенные через группы элементов И 2О с входами сумматора, схему сравнения, соединенную одними своими входами с выходами счетчиков, а другими — с выходами сумматора (1) .

Однако данное устройство характеризуется недостаточно высокой точностью форьГирования кодовых описаний, затрудняющей последующий логический анализ иэображений. Действительно, устройство обеспечивает формирование точных значений коор.-. динат концов формируемых отрезков, из которых по величине наибольшей проекции и знакам проекций можно выделить лишь четыре фиксированных направления. Точность формируемого таким образом кодового описания чертежно-графического изображения с целью его последующего логического анализа оказывается недоста-. точной. 4О

Наиболее близким к предлагаемому . является устройство, содержащее сумматор, соединенный с .группой элементов ИЛИ, с регистрами сдвига„ с блоком сравнения, подключенным к лервсму элементу задержки, к одним входам элементов ИЛИ группы и к регистрам сдвига, триггеры группы, .оециненные с элементами И второй группы, второй элемент задержки, подключенный к первому элементу задержки и к другим входам элементов И второй группы, элемент ИЛИ (2) .

Однако данное устройство характеризуется недостаточно высокой точностью., Цель изобретения - повышение точности устройства.

Поставленная цель достигается тем, что в устройство, содержащее первую группу элементов ИЛИ, одни входы которых являются входами первой группы устройства, а выходи соединены с одними входами сумматЬра, другие входы которогд подключены к регистрам сдвига, блок сравнения, соединенный с регистрами сдвига, с сумматором, с первым элементом задержки, подключенным к второму элементу задержки, и с другими входами элементов ИЛИ первой группы, группу триггеров, входы которых являются другой группой входов устройства, а выходы подключены к одним входам соответствующих элементов И первой группы, другие входы которых соединены с сумматором и с вторым элементом задержки, и элемент ИЛИ, введены вторая группа элементов Й, входы которых соединены с первым элементом задержки и и сумматором, подключенным к блоку сравнения, а выходы соединены с соответствующими регистрами сдвига, третий элемент задержки, подключенный к первому элементу задержки и к другим входам элементов ИЛИ первой группы, элемент И, " входы которого соединены с первым элементом задержки,и с выходом сумматора, третья группа элементов И, одни входы которых подключены к второму элементу задержки и к сумматору, а выходы подключены к элементу ЙЛИ, выход которого соединен с входами соответствующих элементов И первой группы, четвертый элемент задержки, подключенный к второму элементу задержки, триггер, входы которого соединены с элементом И и с четвертым элементом задержки, а выходы подключены к соответствующим элементам И первой и третьей групп, а вторая группа элементов ИЛИ, входы которых подключены к соответствующим элементам И первой группы, а выходы являются группой выходов устройства.

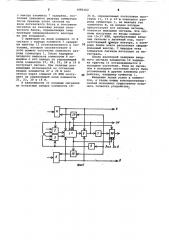

На фиг.1 представлена блок-схема устройства; на фиг.2 — конструктивное выполнение логического блока. устройство включает сумматор 1, первую группу элементов 2 и 3 ИЛИ, регистры 4 и 5 сдвига, блок 6 сравнения, первый 7, второй. 8, третий 9 и четвертый 10 элементы задержки,триггер 11, элемент 12 И, группу триггеров 13 и 14, вторую группу элементов 15, 16 и 17 ИЛИ, первую группу элементов 18-24 И, вторую группу 25 и 26 и третью группу 27 и 28 элементов И, элемент 29 ИЛИ. Элементы 8 и 10 задержки, триггеры 11, 13 и 14, элемент

12 И, вторая группа элементов

15-17 ИЛИ, первая группа элементов 18-24 И, третья группа элементов 27 и 28 и элемент 29 ИЛИ входят в состав логического блока 30. устройство работает следующим ,образом.

1080162

В исходном состоянии сумматор 1 " и регистры 4 и 5 обнулены. Текущее значение содержимого регистров 4 и 5 соответствует текущему значению координаты формируемого вектора и определяется количеством элемен- 5 тарных приращений координат, поступивших на входы элементов 2 И 3 ИЛИ. С приходом каждого импульса, соответствующего изменению текущей координаты на элементарное при- 10 ращение, на вход элемента 2 ИЛИ и связанный с ним управляющий вход сумматора 1 к содержимому сумматора добавляется содержимое регистра 4, которое, с учетом сдвига разрядов, 15 составит величину, численно равную 0,5Х.

С приходом каждого импульса, соответствующего изменению текущей .координаты Х на элементарное приращение, на вход элемента 3 ИЛИ и связанный с ним управляющий вход сумма-, тора 1 из содержимого сумматора вы" читается содержимое регистра 5,.которое, с учетож..сдвига разрядов, составит величину, численно равную

0,5У.

В результате последовательного переноса содержимого регистров в нем формируется значение функции рассогласования.

Содержимое сумматора, численно равное значению функции рассогласования, сравнивается по модулю 35 в блоке б с текущими значениями содержимого регистров 4 и 5. При выполнении логического условия, когда удвоенное значение функции рассогласования больше обоих значений gg текущих координат, на входе блока б. вырабатывается сигнал Признак конца отрезка, свидетельствующий об отклонении текущего приращения от прямолинейной траектории, и он блокируется на время дальнейшей работы. В момент появления сигнала на выходе блока б разрешается считывание и выдача в ЭВМ содержимого регистров 4 и 5, прямо пропорционального относительным координатам конца сформированного вектора..Сумматор 1 при этом обнуляется и на его управляющие входы с выхода блока б через элементы 2 и 3 ИЛИ поступают сигналы, разрешающие суммиро- Ы ванне содержимого регистра 4 и .вычитания содержимого регистра 5.

Содержимое сумматора при этом опре деляется другой величиной функции рассогласования. При этом знак со- 60 держимого сумматора характеризует, в какой половине квадранта находится сформированный вектор. Принадлежность вектора к тому или иному сектору квадранта определяется фактически состоянием знакового разряда— сумматора.

После задержки сигнала элементом 7 задержки, достаточной для выполнения операции суммирования содержимого регистров 4 и 5 в сумматоре 1, сигнал с выхода этого элемента поступает на вход блока 30, где запоминается состоявшие знакового разряда сумматора PJ .

В зависимости от состояния знакового разряда сумматора на входе одного из элементов 25 И или 26 И появится разрешающий потенциал, поэтому сигнал с выхода элемента 7 задержки через один из укаэанных элементов поступит на управляющий вход одного из регистров 4 или 5 и вызовет сдвиг содержимого регистра на два разряда в сторону старшего разряда, при этом содержимое другого регистра останется без изменения.

Задержанный дополнительно элементом 9 задержки сигнал с выхода элемента 7 задержки поступает через элементы 2 и 3 ИЛИ на управляющие входы сумматора 1, разрешая перенос. содержимого регистров 4 и 5 в сумматор.

Состояние знакового разряда сум матора после выполнения операции суммирования определяет положение сформированного вектора в пределах соответствующих секторов квадранта.

Таким образом, состояние знакового разряда сумматора в различные моменты времени после появления сигнала на выходе блока б однозначно определяет положение вектора в пределах квадранта, а значит и его кодовое описание.

В пределах плоскости положения вектора его кодовое описание дополняется знаками его проекции на оси координат, что однозначно определяет его местоположение и ко.довое описание в пределах четырех квадрантов.

После выдачи кодового описания .вектора регистры и сумматор обнуляются (связь. не показана), затем .описанный цикл обработки информации повторяется.

Блок 30 преобразует исходные кодовые описания сформированного вектора и выходные кодовые описания, в которых код вектора представлен в двоичной системе счисления порядковым номером вектора, принадлежащего к одному из восьми векторов фиксированных направлений, к которому ближе всего расположен сформированный вектор.

Исходной информацией для работы блока 30 является состояние знакового разряда сумматора 1 в момент прихода на вход блока сигнала с выхода элемента 7 задержки, состояние знакового разряда сумматора после прихода этого сигнала на вход логического блока и состояние сигналов на знаковых входах логического блока, определяющих знак проекции сформированного вектора на.оси координат.

С приходом на вход элемента 12 И сигнала с выхода элемента 7 задержки триггер 13 устанавливается в состояние, которое соответствует в этот момент состоянию знакового разряда сумматора 1. После задержки входного импульса элементом 8 задержки с его выхода на управляющий вход элементов 27, 28, 22, 24 и 19 И поступает сигнал. При наличии разрешающих потенциалов на остальных входах элементов 27 и 28 И этот сигнал через элемент 29 ИЛИ поступает на управляющий вход элементов

21 23, 20 и 18 И.

В зависимости от входных сигналов ,на остальных входах элементов 1824 И, определяемых состоянием триггеров 11, 13 и 14 и знакового разряда сумматора 1, на выходах тех элементов И, на входах которых присутствуют все входные сигналы, появятся выходные сигналы. Эти сигналы поступают на входы элементов 15-17 ИЛИ, преобразующие входные сигналы в двоичный код, соответствующий ирмеру вектора, к котеIO рому ближе всего расположен .сформированный вектор. С выходов этих элементов сигналы поступают на магистраль.

После некоторой задержки вход15 ного сигнала элементом 10 задержки триггер ll устанавливается В исходное состояние. Этим же сигналом в исходное состояние могут быть установлены и другие элементы устройства, например сумматор l.

Введение новых узлов и элементов, а также новых конструктивных связей позволяет существенно повысить точность устройства.

1080162 фиа2

Составитель Т.Ничипорович

Редактор М.Петрова ТехредМ.Гергель Корректор. :О.Тигор

Заказ 1360/50 Тираж б99 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4