Устройство для приема самосинхронизирующейся дискретной информации

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ПРИЕМА САМОа1НХРОНИЗИРУЮШЕЙСЯ ДИСКРЕТНОЙ ИНФОРМАЦИИ по авт.св. № 836814, отличающееся тем, что, с целью повшаения помехоустойчивости, введены два триггера, два сумматора Ш) модулю два и алемент И,_причем выход приемника подключен к вхсяу накопителя через первый вход элемента И, выход приемника соединен с первыми входами триггеров, выходы которых средине-* ны с первыми входами сумматоров по модулю два, вто1ше входы ксаарьа. и вторые входы соответствующих триггеров объединены и соединены с соответсх^ вующими выходами блока обработки сигналов, выходы сумматоров по модулю два . соединены с втсфым и третьим входами элемента И,(О

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН ае аи

y g Н 04 4 17/16

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТЮ

ОПИСАНИЕ ИЗОБРЕТЕНИ

К АВТОРСНОМЪ(СВИДЕТЕЛЬСТВУ (6 1) 836814 (21) 3525623/18-09 (22) 20.12.82 (46) 15.03.84. Бкж. М 10 (72) Н.А,Тхишев, И.И.Цридякин и П,Г.Тесня (71) Квбардино-Балкарский филиал Проектнсмтехнологического объединения по, внедрению автоматиэированных.систем управления Россельхоэтехсистема (53) 621.394.662(088.8) (56) 1. Авторское свидетепьство СССР М 836814, кл. Н 04. L 17/16, 1979 (прототип). (54) (57) УСТРОЙСТВО ДЛЯ ПРИЕМА

САМОСИ НХРОНИЗИРУЮЩЕЙСЯ QHCKPETНОЙ ИНФОРМАЦИИ по авт.св. М 836814, отличающееся тем, что, с целью повышения помехоустойчивснли, введены два триггера, два сумматора в модулю два и элемент И, причем выход приемника подключен к входу накопителя через первый вход элемента И, выход приемника соединен с первымн входами триггеров, выходы которых соединены с первыми входами сумматоров по модулю два, вторые входы которых и вторые входы соответствукецих триггеров объединены и соединены с соответствуимцими выходами блока обработки сагггалов, выходы сумматоров по модулю два соединенц с вторым и третьим входами элемента И. С:

1 10802

Изобретение относится к технике пе- редачи дискретной информации и может использоваться в сисгемах передачи данных, использующих асинхронный принцип приема. 5

По основному авт.св. Ж 836814 известно устройство дпя приема самосинхронизирующейся дискретной информации, содержащее блок коммутации, регистр сдвига, селектор синхросигнала, накопитель, 10 блок обработки сигналов и приемник, вход которого соединен с входом блока обработки сигналов, выход приемника подключен к входу накопителя, выходы . регистра сдвига соединены с соответ- 15 ствуккцими входами блока коммутации, элемент памяти и декодер, входы которого соединены с соответствующими вы. ходами блока коммутации, вход регистра сдвига соединен с выходом элемента 20 памяти, входы которого соединены с соот-. ветствующими выходами блока обработ-. ки сигналов, выходы накопителя соединены с соответствующими входами селектора синхроснгнала, выход которого под- 25 ключен к управляющему входу блока коммутации 1) .

Однако устройство обладает недостаточной помехоустойчивостью.

Цепь изобретения - повышение номе- з0 хоустойчивости.

Бель достигается тем, что в устройство для приема самосинхронизирующейся дискретной информации, содержащее блок коммутации, регистр сдвига, селек- З5 тор синхросигнала, накопитель, блок обработки сигналов и приемник, вход которого соединен с входом бпока обработки сигналов, выход приемника подключен к входу накопителя, выходы регистра

40 сдвига соединены с соответствующими входами блока коммутации, элемент памяти и декодер, входы которого соединены с соответствующими выходами блока коммутации, вход регистра сдвига соеди45 иен с выходом элемента памяти, входы которого соединены с соответствующими выходами блока обработки сигналов, выходы накопителя соединены с соответствующими входами селектора сннхросип нала, выход которого под;цпочен к управляющему входу блока коммутации, введены два триггера, два сумматора по модулю два и элеменг И, причем выход цриемника подключен к входу накопителя 55 через первый вход элемента И, выход приемника соединен с первыми входами триггеров, выходы которых соединены с

xI Р™н входами сумматоров по модулю два, вторые входы которых и вторые входы соответствующих триггеров объединены и соединены с соответствующими выходами блока обработки сигналов, выходы сумматоров по модулю два соединены с вторым н третьим входами элементаИ.

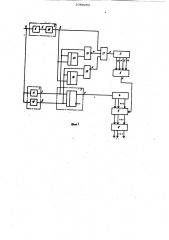

На фиг. 1 изображена структурная электрическая схема предлагаемого устройства; на фнг. 2 - временные диаграммы, поясняющие работу устро1 ства.

Устройство дпя приема сннхрониэирующейся дискретной информации содержит блок 1 обработки сигналов, приемник 2, накопитель 3, регистр 4 сдвига, блок 5,коммутации, селектор 6 сннхросигнала, элемент памяти 7, декодер 8, приемник 2 состоит нз блока 9 выделения фронтов сигнала н формирователя 10. импульсов заданной длительности,блок 1 состоит из селекторов 11,12 положительных и отрицательных посылок, триг геры 13, 14, сумматоры 15, 16 по модулю два, элемент И 17.

Устройство работает следующим образом.

Самосинхроннзйрующаяся импульсная последовательность f g<) (фнг.2), сфор- . мированная на передатчике нз двоичной последовательности fA;) по закону 2 „=

= Хк-Ук; Хк= АкХк-1; Ук=АкУк-1;

Хо= Уо=-О, где К = 1л, соответствует порядковому номеру значащего характеристического момента модуляции передаваемого сигнала, поступает на входы блока 1 обработки сигнала н приемника 2.

Прн этом действие помех в канале связи приводит, как правило, к краевым искажениям и дроблениям элементов последовательности на входе устройства (фиг.2а).

Елок 1 обработки сигнала выделяет в принимаемой последовательности положительные н отрицательные посылки. Одновременно в блоке 9 приемника 2 происходит выделение фронтов проходящего сигнала, которые поступают на вход формирователя 10 импульсов заданной длительности (фиг.2б). С помощью формнров теля 10 по фронтам сигнала формируются импульсы, длительность которых опреГ деляет интервал принятия решения о приеме самосинхронизнрующе йся последовательности. Сформированные импульсы поступают на вход накопителя 3 (фиг.2в). При окончании записи рабочей кодовой комбинации в накопитель 3 селектор 6 синхросигнала фиксирует ее н выдает на óïравляющий вход блока 5 коммутации сигз 1080 нал разрешения выдачи информации, записанной в регистре 4 сдвига. На выходе селектора 11 положительных посылок импульс (фиг.2г) проявляется прИ наличии положительной посылки, а на выходе селектора 12 отрицательных посылок (фиг.2д)-при наличии отрицательной посылки. Сигналы с выходов селекторов

11 и 12 поступают соответственно на5и R-входы элемента памяти 7, выполнен-}О ного на R5-триггере, где преобразуются в двоичную информационную последовательность (фиг.2е); которая поступает на вход регистра 4 сдвига.

Таким образом, информация может быть выдана с ошибкой в том случае, если моменты появления импульсов дроблений в канале связи попадают в зону существования сигнала на выходе селектора 6, длительность которой определя- 20 ется импульсами заданной длительности (интервалом принятия решения) с формирователя 10. В свою очередь, продол-. жительность импульса заданной длительности не может быть выбрана как угод- 25 но малой, . поскольку она определяется величиной краевых искажений в канале связи, емкостью дискретного накопителя, частотой тактового генератора и быстродействием элементной базы.

Для повышения помехоустойчивости сигналы с выходов блока 1 обработки сигнала поступают на входы первого и

;второго триггеров 13,14 и входы первого и второго сумматоров 15,16 по модулю два. Запись информации в триггеры

13,14 (фиг.2ж, .. з) производится по переднему фронту импульса заданной длительности с выхода. формирователи 10.

Сумматоры 15, 16 по модулю два выдают запрещающий сигнал (фиг.2и,. ..к) в

40 том случае,. если после записи информации в триггеры 13,14,произошло изменение положительного, отрицательного или нейтрального (нулевого) сигнала в исЪ 45 ходной троичной последовательности. Нулевому сигналу в троичной последовательности соответствует отсутствие сигна:лов на обоих выходах блока 1 обработки сигнала, При срабатывании сумматоров 15, 16 по модулю два с выхода элемента И 17 (фиг.2л) в накопитель 3 последовательно записываются импульсы заданной длительности, структура поражения которых помехами такая же, как и элементов информационной последовательности (фиг. 2е) в интервале принятия решения.

Соответствующие выходы накопителя 3 (фиг. 2 и, м, н, о, п) подключены пара илельно к входам селектора 6 синхросигнала. B результате на выходе селектора 6 появляются единичные импульсы в те моменты времени, когда элементы информационной последовательности не подвержены действию помех.

Сигнал с выхода, селектора 6 через блок 5 коммутации осуществляет считывание информационной последовательности в декодер 8, где она преобразуется в знак сообщения. Для рассматриваемого случая в интервале принятия решения о приеме самосинхрониэирующейся последоватепьности выделены две зоны, в которых сигнал не поражен помехами (фиг.2р), т.е. считывание информации, записанной в регистре 4 сдвига достаточно произвести в одной иэ этих эон.

Таким образок., предлагаемое устройство для приема самосинхрониэирующейся дискретной информации при передаче сообщения короткими блоками в, канале с импульсными помехами, длительность которых меньше длительности единичного элемента, позволяет реализовать .принцип авторегенерации, т.е. вывод регистрирующих импульсов в ту часть rAформационной посылки, которая с наименьшей вероятностью подвержена искажению при всех видах мешающих факторов. Вероятность ошибочного приема в этом случае но сравнению с прототипом уменьшается на порядок.

1080252

1080252

flic

Г Д

Составитель Н.Лазарева

Редактор А.Долиннч Техред А. Кикемезей Корректор В.Гирняк

Заказ 1374/54 Тираж 635 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 13035, Москва, Ж-25, Раун ская наб., д. 4/5

Филиал ППП "Патент", r.Óæ город, ул.Проектная, 4