Устройство умножения в дополнительных кодах

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО УМНОЖЕНИЯ ВДОПОЛНИТЕЛЬНЫХ КОДАХ, содержащее первый и второй регистры, две группы элементов И-НЕ, сумматор, первьй и второй элементы И, причем прямые выходы первого регистра соединены соответствено с первыми входами эле- . ментов И-НЕ первой группы, вторые входы которых соединены с выходами первого элемента И, инверсные выходы первого регистра соединены соответственно с первыми входами элементов И-НЕ второй группы, вторые входы koTopbix соединены с выходом второго элемента И, выходы элементов И-НЕ первой и второй групп соединены с соответствующими разрядными входами сумматора, вход младшего разряда которого соединен с выходом первого элемента И, первые входы перг вого и второго элементов И соединены с входом устройства, отличающ . е е с я тем, что, с целью повьщ1ения быстродействия устройства, в него введены полусумматор, третий элемент И, элемент ИЛИ, элемент задержки , причем вторые входы первого и второго элементов И соединены соответственно с инверсным и прямым выходами знакового разряда второго ре ( гистра, выход младшего разряда кото (Л рого соединен с первым входом полусумматора , второй вход которого соединен с выходом третьего элемента И, выход еуммы полусумматора соединен с .третьими входами первого и второго элементов И и первым входом элемента ИЛИ, выход переноса полусумматоэо ра соединен с вторым входом элемента ИЛИ, выход которого соединен с f входом элемента задержки, выход которого соединен с первым входом третьего элемента И, второй вход которого соединен с инверсным выходом знакового разярда второго регистра.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) Зд)) G 06 F 7/52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

1

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3460002/18-24 (22) 02.07.82 (46) 23.03.84. Бюл. )"- 11 (72) P.Â.Êoðoáêoâ и В.Е.Золотовский (71) Таганрогский радиотехнический институт им. В.Д.Калмыкова (53) 681.325(088.8) (56) 1. Карцев М.А. Арифметика цифровых машин. M., "Наука", 1969, с. 472-478.

2. Карцев M.À. Арифметика цифровых машин. М., "Наука", 1969, с. 481-484.

3 ° Карцев M.À. Арифметика цифровых машин. M. "Наука", 1969, с. 478-484 (прототип). (54) (57) УСТРОЙСТВО УМНОЖЕНИЯ В ДОПОЛНИТЕЛЬНЫХ КОДАХ, содержащее первый и второй регистры, две группы элементов И-НЕ, сумматор, первый и второй элементы И, причем прямые выходы первого регистра соединены соответствено с первыми входами элементов И-НЕ первой группы, вторые входы которых соединены с выходами первого элемента И, инверсные выходы первого регистра соединены соответственно с первыми входами элементов И-НЕ второй группы, вторые входы которых соединены с выходом второго элемента И, выходы элементов И-НЕ первой.и второй групп соединены с соответствующими разрядными входами сумматора, вход младшего разряда которого соединен с выходом первого элемента И, первые входы пер-. вого и второго элементов И соединены с входом устройства, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия устройства, в него введены полусумматор, третий элемент И, элемент ИЛИ, элемент задержки, причем вторые входы первого и второго элементов И соединены соответственно с инверсным и прямым выходами знакового разряда второго регистра, выход младшего разряда которого соединен с первым входом полусумматора, второй вход которого соединен с выходом третьего элемента И, выход еуммы полусумматора соединен с третьими входами первого и второго элементов И и первым входом элемента ИЛИ, выход переноса полусумматора соединен с вторым входом элемента ИЛИ, выход которого соединен с входом элемента задержки, выход кото. рого соединен с первым входом третьего элемента И, второй вход которого соединен с инверсным выходом знакового разярда второго регистра.

1081640

Изобретение относится к вычислительной технике и предназначено для использования в цифровых вычислительных машинах различного назначения.

Известно устройство умножения в дополнительных кодах с двумя коррек. тирующими шагами, содержащее два регистра, формирователь частичных произведений, схему коррекции и сумматор, причем выход первого регистра через формирователь частичных произведений соединен с входами сумматора и схемы коррекции, первый выход второго регистра соединен с входом формирователя частичных произве дений, второй выход — с входом схемы коррекции, выход которой соединен с входом сумматора j1J .

В устройстве увеличивается время операции, так как коррекция требует выполнения двух дополнительных циклов. Необходимость коррекции усложняет устройство управления множителя.

Известно устройство умножения в дополнительных кодах путем последовательного преобразования множителя, содержащее два регистра, формирователь частичных произведений, сумматор и преобразователь множителя, причем выход первого регистра через формирователь частичных произведений соединен с входом сумматора, выход второго регистра через преобразователь множителя соединен с входом формирователя частичных произведений (2) .

В таком устройстве увеличиваются время умножения и расход оборудования. Первое обусловлено необходимостью выполнения дополнительного цикла умножения, второе — необходимостью преобразования множителя.

50

Наиболее близким по технической сущности к изобретению является устройство умножения в дополнительных кодах с одним корректирующим шагом, содержащее два регистра, сумматор, схему инверсии, два элемента И, причем выход первого регистра через схему присвоения знака соединен с входом сумматора, выход второго регистра — с первыми входами элементов И, вторые и третьи входы элементов И соединены с входами устройства, выходы элементов И вЂ” с входами схемы инверсии (3) .

5 !

О

l5

\ 5

Недостаток известного устройства состоит в увеличении. времени умножения, так как необходим дополнительный цикл для выполнения коррекции произведения. Так как для управления устройством необходимы функциональные сигналы, управляющие режимом умножения, и сигналы, управляющие режимом коррекции, диаграмма управляющих сигналов усложняется, что приводит к усложнению устройства.

Цель изобретения — повышение быстродействия устройства.

Цель достигается тем, что в устройство, содержащее первый и второй регистры, две группы элементов И-НЕ, сумматор, первый и второй элементы И, причем прямые выходы первого регистра соединены соответственно с первыми входами элементов И-НЕ первой группы, вторые входы которых соединены с выходами первого элемента И, инверсные выходы первого регистра соединены соответственно с первыми входами элементов И-НЕ второй группы, вторые входы которых соединены с выходом второго элемента И, выходы элементов И-НЕ первой и второй групп соединены с соответствующими разрядными входами сумматора, вход младшего разряда которого соединен с выходом первого элемента И, первые входы первого и второго элементов И соединены с входом устройства, введены полусумматор, третий элемент И, элемент ИЛИ, элемент задержки, причем вторые входы первого и второго элементов И соединены соотвветственно с инверсным и прямым выходами знакового разряда второго регистра, выход младшего разряда которого соединен с первым входом полусумматора, второй вход которого соединен с выходом третьего элемента И, выход суммы полусумматора соединен с третьими входами первого и второго элементов И и первым входом элемента ИЛИ, выход переноса полусумматора соединен с вторым входом элемента ИЛИ, выход которого соединен с входом элемента задержки, выход которого соединен с первым входом третьего элемента И, второй вход которого соединен с инверсным выходом знакового разряда второго регистра.

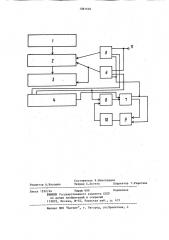

На чертеже показана схема предлагаемого устройства.

1081640

Схема содержит регистр 1 множи го, схему 2 инверсии, сумматор 3, регистр 4 множителя, элементы И 5 и 6, полусумматор 7, элемент И 8, элемент ИЛИ 9, элемент 10 задержки и вход 11 устрой тва.

Прямые и инверсные выходы регистра 1 соединены со схемой 2 инверсии, представляющей собой две группы элементов И-НЕ, причем прямые выходы 10 регистра 1 соединены с соответ"твую. щими первыми входами элементов И-НЕ первой группы, вторые входы элементов И-НЕ которой соединены с выходами элемента И 6, инверсные выходы 15 регистра 1 соединены с первыми входами элементов И-НЕ .второй группы, вторые входы элементов И-НЕ которой соединены с выходом элемента И 5. Выходы элементов И-НЕ первой и второй групп соединены с соответствующими разрядными входами сумматора 3, младший разряд которого соединен с выходом элемента И 6. Первый и второй выходы регистра 4 соединены с вторыми 25 входами элементов И 5 и 6. Третий выход регистра 4 соединены с первым входом полусумматора 7, второй вход которого соединен с выходом элемента И 8. Первый выход полусуммато- щ ра 7 соединен с третьими входами элементов И 5 и 6 и с первым входом элемента ИЛИ 9, второй выход полусумматора 7 соединен с вторым входом элемента ИЛИ 9. Выход элемен35 та ИЛИ 9 через элемент 10 задержки соединен с первым входом элемента И 8, второй вход элемента И 8 соединен с первым выходом регистра 4.

Первые входы элементов И 5 и 6 сое40 динены с входом 11 устройства.

Устройство работает следующим образом.

В регистр 1 записывается множимое в дополнительном коде в реУ 45 гистр 4 — множитель, также в дополнительном коде. Младший разряд множителя проходит через полусумматор 7 на выход суммы, поступает на входы элементов И 5 и 6 проходит через

Э 50 элемент ИЛИ 9 и запоминается в элементе 10 задержки.

Первый цикл умножения начинается с подачи синхронизирующего сигнала на вход устройства 11. Если младший разряд множителя равен "1", сигнал проходит на один из управляющих входов схемы инверсии. Если множитель положителен, сигнал проходит через элемент И 5, если отрицателен— через элемент И 6. Если множитель положителен, множимое передается из регистра 1 в сумматор 3 без изменения, если отрицателен, схема инверсии передает в сумматор 3 инверсию содержимого регистра 1. Одновременно с выхода элемента И 6 сигнал поступает на вход младшего разряда сумматора, т.е. в сумматор поступает дополнение содержимого регистра 1.

Если младший разряд множителя равен нулю, сигнал не поступает на схему инверсии и последняя посылает на вход сумматора нулевой сигнал.

><>ePmeHHa ер с рования содержимое сумматора 3 и регистра 4 сдвигается на один разряд в сторону младших разрядов. Первый разряд множителя выходит из элемен".а задержки и, если множитель отрицателен, складывается с вторым разрядом множителя в полусумматоре 7.

Если множитель положителен, элемент И 8 закрыт и выход элемента задержки не подключается к входу полусумматора. При суммировании первого и второго разрядов множителя на выходах полусумматора формируется сумма или перенос. Сумма вновь поступает на элементы И 5 и 6. Сумма или перенос, объединенные элементом ИЛИ 9, запоминаются в элементе 10 задержки. На этом выполнение цикла заканчивается.

Затем на вход 11 вновь подается сигнал и аналогично выполняется второй цикл.

Умножение заканчивается после отработки старшего значащего разряда множителя. Коррекция результата по

Ъ завершении умножения не требуется.

1081640

Составитель В.Виноградов

Техред С.Легеза Корректор Г.Решетник

Редактор А.Козориз

Филиал ППП "Патент",-г. Ужгород, ул.Проектная, 4

Заказ 1552/44 Тираж 699 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская,наб., д. 4!5