Интегратор

Иллюстрации

Показать всеРеферат

ИНТЕГРАТОР по авт.св. № 922786, отличающийся тем, что, с целью повьшения точности интегрирования, в него введен дискг ретный делитесь напряжения, вход .которого соединен с входом опорного напряжения интегратора, а выход подключен к входу третьего,ключа. S . (Л с

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19(SU ((((gyp С 06 G 7/186

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ASTOPCHOMY СВИДЕТЕЛЬСТВУ (61) 922786 (21) 3362474/18-24 (22) 11. 12. 81 (46) 23.03.84. Бюл. Ф 11 (72) А.Б..Артамонов, А.M.Ñìèðíoâ, А.Н.Жариков и А.Н.Альшевский (71) Ленинградский ордена Ленина электротехнический институт им. В.И.Ульянова (Ленина) (53) 681.335 (088.8) (56) 1. Авторское свидетельство СССР

Ф 922786, кл. G ..06 G 7/186, 1980 (прототип) . (54) (57) ИНТЕГРАТОР по авт.св.

ll(922786, отличающийся тем, что, с целью повьппения точности интегрирования, в него введен диск-, ретный делитель напряжения, вход .которого соединен с входом опорного напряжения интегратора, а выход подключен к входу третьего ключа.

1081643

Изобретение относится к аналогоцифровой вычислительной технике и предназначено для выполнения операции интегрирования при моделировании значения интеграла и подынтегральной функции напряжениями постоянного тока.

По основному авт.св. Ф 922786 известен интегратор, содержащий интегрирующий усилитель, выход которого подключен к компаратору, вторым вхо- 10 дом соединенному с входом опорного напряжения, блок управления, первый . вход которого подключен к выходу компаратора, первый ключ, включенный параллельно интегрирующему усилителю,15 второй и третий ключи, включенные пследовательно между сигнальным входом и входом опорного напряжения интегратора, реверсивный счетчик, суммирующий вход которого через первый 2О элемент И соединен с выходом генератора импульсов, а выходы разрядов подключены к управляющему входу цифровой управляемой проводимости, включенной между общим выводом второго 2g и третьего ключей и входом интегрирующего усилителя, дополнительный реверсивный счетчик и три элемен-. та И, первые входы которых подключны к выходу генератора импульсов, вторые входы — к выходам блока управления, а выходы — к соответствующим входам реверсивных счетчиков, входы приема кода которых соединен с управляющим входом интегратора, 35 причем управляющие входы ключей соединены с выходами блока управления (1) .

Известный интегратор плавно изменяет в достаточно широко д м иапазо 40 не постоянную времени интегратора и, кроме того, посредством периодической коррекции поддерживает требуемое значение постоянной времени при температурном и временном из- 45 менениях входных резистров и интег рирующей емкости, что позволяет с помощью неточных и нетермост абильных элементов устанавливать точно постоянную времени интегратора в

1пироком диапазоне температур. .l

Недостатком известного устройства является невысокая точность установки постоянной времени интегратора, 5 что происходит в результ льтате некомпеисирования ошибки, св связанной с задержкой срабатывания интегратора.

Цель изобретения — повышение точности интегрирования.

Поставленная цель достигается тем, что в интегратор введен дискретный делитель напряжения, вход которого соединен с входом опорного напряжения интегратора, а выход подключен к входу третьего ключа.

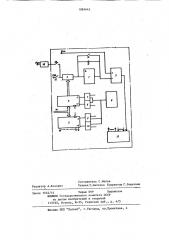

На чертеже представлена схема предлагаемого интегратора.

Интегратор содержит операционный усилитель i, компаратор 2, цифpoayto управляемую проводимость 3, основной реверсивный счетчик 4, дополнительный реверсивный счетчик 5, генератор 6 импульсов, элементы И 710, интегрирующий конденсатор 11, ключи 12-14, блок 15 управления и импульсный делитель 16 напряжения.

К входу интегрирующего усилителя 1 подключена цифроуправляемая проводимость 3, управляющий вход которой соединен с разрядными выходами реверсивного счетчика 4. Входы реверсивных счетчиков 4 и 5 через элементы И 7-10 подключены к выходу генератора 6 импульсов.

Выход интегрирующего усилителя 1 подключен к первому входу компаратора 2, второй вход которого соединен с входом опорного напряжения, а выход подключен к входу блока 15 управления. Импульсный делитель 16 напряжения через ключ 13 подключен к цифроуправляемой проводимости 3,соединенной через ключ 12 с сигнальным входом интегратора.

Устройство работает следующим образом.

Напряжение на выходе идеального интегратора в режиме интегрирования постоянного входного сигнала (режим коррекции) выражается форму-, К Ц=-0,—, (1) где Г(Ч- напряжение на выходе идея аль но го инте гр атора (U — входное опорное напряжение, 1

0 время

Т вЂ” постоянная времени идеальноН го интегратора.

Зависимость выходного напряжения реального интегратора выглядит следующим образом:

0, при О- 1- t3

Р(О при t>,t, P

1081643 где U (4) напряжение на выходе

1 реального инте гратора; — время задержки срабатыва

3 ния интегратора, Т вЂ” постоянная времени реальР ного интегратора.

Напряжение на выходе интегратора при t = T> по усиловиям работы схемы известного интегратора с цифровой коррекцией постоянной времени равно U>.

Таким образом т„-, о ="о (З)

Отсюда после коррекции

Тр = T Т „(4) Для уменьшения влияния погрешности на точность установки постоянной времени предлагается проводить коррекцию не за.время t = Т„, а за время интегрирования, равное t = nT„, где и — кратность увеличения времени интегрирования по сравнению с

Ти (целое число).

Для того, чтобы это осуществить, и для того, чтобы выходное напряжение не превысило максимально возможной величины выходной шкалы напряжений, входное напряжение в режиме коррекции следует соответственно уменьшить в д раэ.

Тогда выходное напряжение интегратора будет: ппрН 00-" - з и 0)= 11„. t-< З (З) и 1i "Р" < З

Отсюда получаем

Т = Т и (6)

Погрешность постоянной времени из-за задержки при этом уменьшится в vl раз.

С целью сохранения величины кода корректирующего счетчика частоту генератора счетных импульсов надо уменьшить в 11 раз:, — (7)

15 где Е,1 — частота генератора 6 в предложенном устройстве, частота генератора в известном устройстве.

Предлагаемый интегратор имеет

20 большую точность установки постоянной времени (во всем диапазоне изменения постоянной времени) благодаря уменьшению погрешности, связанной с задержкой срабатывания интегратора.

25 Это повышение точности особенно заметно при работе интегратора с "быстtl рыми сигналами (больше скорость изменения входного сигнала и повышение точности) .Кроме того, низкие требоваЗ0 ния к точности элементов, входящих в состав интегратора (как и в из вестном устройстве), позволяет облегчить изготовление интегратора в интегральном исполнении.

1081643

Составитель С.Белан

Техред Т.Маточка Корректор Г.Решетник

Редактор А.Козориз

Заказ 1552/44 Тираж 699 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г.ужгород, ул.Проектная, 4