Устройство переменного приоритета

Иллюстрации

Показать всеРеферат

) УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА, содержащее циклический регистр сдвига, регистр запросов, триггер направления сдвига, первую группу элементов И, элемент ИЛИ-НЕ, два элемента И, шифратор, дешифратор , причем первые входы элементов И первой группы соединены с выхода ми соответствунхцих разрядов регийтра запросов, выходы элементов И первой групйы подсоединены к входам элемЪнта ИЛИ-НЕ и шифратора, выходы которого являются выходами устройства , выход элемента ИЛИ-НЕ соединен с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с прямшл .и инверсньш выходами триггера направления сдвига, третьи входы первого и второго элементов И соединены с тактовым входом устройства, выходы первого и второго элементов подсоединены соответствейно к первому и второму зхопам управления сдвигом циклического регистрасдвига, выходы которого соединены с вторь1ми входами соответствующих элементов И первой группы, входы регистра запросов являются информационными входами устройства , входы дешифратора являются кодовыми входами устройства, входы триггера направления сдвига явля1Ьтся первым и вторым входами опроса устройства, о тличающеес я тем, что, с целью повышения быстродействия , оно содержит вторую и третью группы элементов И, буферный регистр и два элемента ИЛИ, причем первые входы элементов И второй груп пы соединены с выходами дешифратора, вторые входы элементов И второй S группы соединены с выходом первого элемента ИЛИ, первый вход которого является входом запуска устройства, Г второй вход первого элемента ИЛИ свя зан с выходом второго элемента ИЛИ, входы которого соединены с выходами элементов И третьей группы, первые входы элементов И третьей группы соединены с выходами буферного регистра , вторые входы элементов И 00 третьей группы соединены с соответствующими выходами регистра запросов оо р§ входы буферного регистра соединены с выходами циклического регистра сдвига, входами которого являются . выходы элементов И второй группы, выход второго ИЛИ соединен с входами сброса циклического реги ,стра сдвига и буферного регистра.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ . РЕСПУБЛИН (1% (11) М59 0 06 F 9 46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCKOMY СВИДЕТЕЛЬСТВ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21)3521408/18-24 (22)16.12.82 (46) 30 03 84. Вюл. 9 12, (72) О.E.Молчанов, С.JI.Ìåëåøêî, И.Н.Основенко и A.Ä.Ùå÷êèí (53) 654. 325(088.8) (56) 1. Авторское свидетельство СССР

Р 7-46520 кл. G 06 Р 9/4-6, 1980.

2. Авторское свидетельство СССР по заявке Р 3386032/18-24, кл. G 06 F 9/46, 1982 (прототип). (54)(57) УСТРОЙСТВО ПЕРЕМЕННОГО

ПРИОРИТЕТА, содержащее циклический регистр сдвига, регистр запросов, триггер направления сдвига, первую группу элементов И, элемент. ИЛИ-НЕ, два элемента И, шифратор, дешифратор, причем первые входы элементов

И первой группы соединены с выходами соответствующих разрядов регистра запросов, выходы элементов И первой групПы подсоединены к входам элемента ИЛИ-НЕ и шифратора, выходы которого являются выходами устройства, выход элемента ИЛИ-НЕ соединен с первыми входами первого и второго элементов И, вторые входи которых соединены соответственно с прямым и инверсным выходами триггера направления сдвига, третьи входы первого и второго элементов И соединены с тактовым входом устройства, выходы первого и второго элементов подсоединены соответственно к первому и второ.— му входам управления сдвигом циклиб ческого регистра- сдвига, выходы которого соединены с вторйми входами соответствующих элементов И первой группы, входы регистра запросов являются информационными входами устройства, входы дешифратора являются кодовыми входами устройства, входы триггера направления сдвига являются первым и вторым входами опроса устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит вторую и третью группы элементов И, буферный регистр и два элемента ИЛЙ, причем первые входы элементов И второй груп-. пы соединены с выходами дешифратора, вторые входы элементов И второй группы соединены с выходом первого элемента ИЛИ, первый вход которого является входом запуска устройства, второй вход первого элемента ИЛИ свя зан с выходом второго элемента ИЛИ, входы которого соединены с выходами р элементов И третьей группы, первые входы элементов И третьей группы соединены с выходами буферного регистра, вторые входы элементов И третьей группы соединены с соответствующими выходами регистра запросов входы буферного регистра соединены с выходами циклического регистра сдвига, входами которого являются выходы элементов И второй группы, выход второго элемента ИЛИ соединен с входами сброса циклического реги,стра сдвига и буферного регистра.

1083192

Из обрете ние относится к вычислительной технике и может найти применение в устройствах прерывания программа

Известно устройство, содержащее регистр приоритета, счетчик, блок анализа на нуль счетчика, циклический регистр сдвига, блок анализа на единицу старшего и соответственно младшего разрядов циклического регистра сдвига, блок управления, трйггер направления сдвигов и блок инвертирования содержимого счетчика Г13.

Недостатком данного устройства является низкое быстродействие, которое обусловлено тремя причинами. Во-первых, определение модифицированной части адреса происходит в несколько этапов . Во-в торых, содержимое циклического регистра сдвига во время определения модифицированной части адреса портится н перед началом очередного цикла его нужно восстановить

В-третьих, запросы, пришедшие во время цикла работы, не могут быть приняты на циклический регистр сдвига.

Известно также устройство, содержащее циклический сдвиговый .регистр, регистр запросов, триггер направления сдвига, группу элементов И. элемент ИЛИ-НЕ, два элемента И сдвига, шифратор н дешифратор 2 ).

Однако указанное устройство имеет низкую пропускную способность высокоприоритетных запросов.

Цель изобретения — повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство переменного приоритета, содержащее циклический регистр сдвига, регистр запросов, триггер направления сдвига, первую группу элементов И, элемент ИЛИ-НЕ, два элемента И, шифратор, дешифратор, причем первые входы элементов, И первой группы соединены с выходамн соответствующих разрядов регистра запросов, выходы элементов И первой группы подсоединены к входам элемента ИЛИ-НЕ и шифратора, выходы которого являются выходами устройства, выход элемента ИЛИ-НЕ соединен с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с прямым и инверсным выходами триггера направ ления сдвига, третьи входы первого и второго элементов И соединены с тактовым входом устройства, выходи первого и второго элементов И подсоединены соответственно к первому и второму входам управления сдвигом циклического регистра сдвига, выходы которого соединены с вторыми входами соответствующих элементов И пер вой, группы, входы регистра запросов являются информационными входами устройства, входы дешифратора являются кодовыми входами устройства, входы триггера направления сдвига являются первым н вторым входами опроса устройства, введены вторая и третья группы элементов И, буферный регистр и два элемента ИЛЙ, причем первые входы элементов И второй группы соединены с выходами дешифра-! тора, вторые входы элементов И вто1О рой группы соединены с выходом первого элемента ИЛИ, первый вход которого является входом запуска устройства, второй вход первого элемента

ИЛИ связан с выходом второго злемен15 та ИЛИ, входы которого соединены с выходами элементов И третьей группы, первые входы элементов И третьей группы соединены с выходами буферного регистра, вторые входы элемен20 тов И третьей группы соединены с со- ответствующими выходами регистра запросов, входы буферного регистра соединены с выходами циклического регистра сдвига, входами которого являg5 ются выходы элементов И второй группы, выход второго элемента ИЛИ соединен с входами сброса циклического регистра сдвига и буферного регистра.

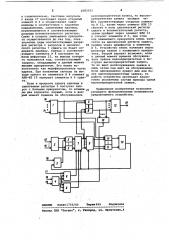

На чертеже представлена функциоЗО нальная схема предлагаемого устройства.

Устройство содержит регистр 1 запросов, дешифратор 2, элемент ИЛИ

3, триггер 4 направления сдвига, группу элементов И 5, группу элементов И 6, циклический регистр 7 сдвига, группу элементов И 8, буферный регистр 9, элемент ИЛИ-НЕ 10, группу элементов И 11, шифратор 12, элемент или 13, информационные входы 14, 40 кодовые входы 15, вход 16 запуска, тактовый вход 17, входы 18 опроса и выходы 19.

Устройство работает следующим образом.

45 В исходном состоянии разряды всех регистров обнулены, на выходе элемента ИЛИ-НЕ 10 единичный сигнал, подготавливающий к открытию элементы И 6 по третьему входу. Программно

5О из ЦВМ на входы 15 поступает код наивысшего приоритета в форме потенциального сигнала, одновременно по входам 18 программно заносится сигнал направления сдвига на триггер 4.

Сигнал занесения кода наивысшего приоритета по входу 16, пройдя элемент ИЛИ 3, открывает элементы И 5 . и код наивысшего приоритета, пройдя через дешифратор и элементы И 5, устанавливает определенный разряд

40 регистра сдвига в единицу, которая сразу же заносится в соответствующий разряд вспомогательного регист° ра 9. Если заявки с наивысшим приоритетом не оказалось, то на входе .65 элемента ИЛИ-НЕ 10 нулевые сигналы, 1083192

ВНИИПИ Эаказ1755/43 Тараж699 Подписное

ЮЮ

Филиал ППП "Патент", г. Ужгород, ул. Проеткиая,4 а следовательно, тактовые импульсы с входа 17 поступают через открытый элемент И 6 и осуществляют сдвиг единицы в соответствии с заданным направлением, сдвигаемые единицы, переписываются в соответствующие 5 разряды вспомогательного регистра .

Сдвиг в сторону уменьшения приорите-. та осуществляется до тех пор, пока значение пары соответствующих разрядов регистра 1 запросов и цикличе- 10 ского регистра 7 сдвига не будет содержать единицу. Сигнал с соответст1 вующего элемента И 8 поступает на вход шифратора 12, на выходе которого появляется код, соответствующий запросу, обладающему в данный момент высшим приоритетом. Его можно ис:пользовать как модифицированную часть адрЕса. При появлении сигнала на вы-.. ходе одного .из элементов И 8 элемент 20

ИЛИ«НЕ 10 запирает элементы И 6 сдвига.

Если в процессе сдвига единицы в. сдвигаемом регистре 3 поступил зап.рос с большим приоритетом, то возмож-ъ5

1 ны два вариантаг первый, если в данный момент времени не обслуживаласЬ низкоприоритетная заявка, то высокоприоритетная заявка пройдет через соответствующие открытые элементы И 11, затеи через элемент ИЛИ 13 сбросит в ноль циклический регистр сдвига н вспомогательный регистр, затем пройдет через элемент ИЛИ 13 и откроет элементы И 5, нри этом код наивысшего приоритета вновь занесется на циклический регистр сдвига, пройдя через дешифратор и элементы

И 5 ° Устройство вновь начинает опрос регистра заявок с наивысшего приоритета. Второй вариант возможен, если в данный момент времени обслуживалась заявка низкоприоритетная и поступил высокоприоритетный запрос, то он ждет дообслуживания заявки и лишь затем сам идет на обслуживание.

Если одновременно придут две или более высокоприоритетные заявки, то работа устройства протекает аналогично указанному случаю прихода одной высокоприоритетной заявки.

Применение изобретения позволяет расширить функциональные возможности предлагаемого устройства.