Операционный модуль

Иллюстрации

Показать всеРеферат

ОПЕРАЦИОННЫЙ МОДУЛЬ, содержащий первый и второй, триггеры, входы синхронизации которых подключены к входу синхронизации модуля, отличающийся тем, что, с целью расширения области применения за счет реализации модулем возможности адаптации к решаемой задаче , в него введены первая и вторая группы элементов 2И-ИЛИ-НЕ по четыре элемента в каждой, элемент НЕ, первый и второй блоки памяти, группы информационных входов, первые группы адресных входов и входы разрешения записи которых соединены соответственно с группой информационных входов,-с группой входов управлейия и с управляющим входом модуля,вторые группы адресных входов первого и второго блоков памяти подключены соотBeTCTBieHHo к выходам элементов. 2ИИЛИ-НЕ первой и второй групп, первые информационные выходы первого и второго блоков памяти соединены соответственно с первым входом первого элемента 2И-ИЛИ-НЕ второй группы и с выходом переноса модуля, второй информационный выход первого блока памяти соединен с информационным входом первого триггера и-с-первым асинхронным выходом данных модуля, второй информационный выход второго блока памяти соединен с информационным входом вт,орого триггера и с вторым асинхронным выходом данных модуля, первый вход первого элемента 2И-ИЛИ-НЕ первой группы соединен с входом переноса модуля, первые входы вторых элементов 2К-ИЛИ-НЕ первой и второй групп соединены соответственно с первым и вторым входами данных модуля, первый вход третьего элемента 2И-1ШИ-КЕ i О) первой группы соединен с выходом первого триггера, с выходом переноса вправо модуля и с первым синхронным входом данных модуля, первый вход третьего элемента 2И-ИЛИ-НЕ второй группы соединен с первым входом четвертого элемента 2И-ИЛИ-МЕ первой группы, с выходом второго триггера и с синхронным выходом данных модуля, первый вход четвертого элемента 2И-ИЛИ-НЕ второй 00 груйпы соединен с входом переноса вправо модуля, вторые входы первых, со вторых, третьих и четвертых элементов 2И-Ш1И-НЕ первой и второй групп соединены соответственно с первым, со вторым, третьим и четвертым входами эо настройки модуля, третьи входы всех элементов 2И-ИЛИ-НЕ соединены с выходом элемента НЕ, вход которого соединен с четвертыми входами всех элементов 2И-ИЛИ-НЕ и с входом управления режимом модуля.

СОЮЭ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ.

РЕСПУБЛИК

„.$0„„ Я}ЯД В

3(5Н 0 06 Г 15/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

М ABTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 3519482/18-24 (22) 03.12.82 (46) 30.03.&4. Бюл. 9 12 (72) М.A.Ãëàäøòåéí. В.И.Комаров и В.A.Áàñêàêîâ (71) Рыбинский авиационный технологический институт (53) 681.325(088.8) (56) 1. Авторское свидетельство СССР

9 842789, кл. G 06 F 7/00. 1980.

2. Авторское свидетельство СССР

9 894714, кл. G 06 F 15/00. 1981 (прототип). (54)(57) ОПЕРАЦИОННЫЙ МОДУЛЬ. содержащий первый и второй. триггеры, входы синхронизации которых подключены к входу синхронизации модуля, о т л и ч а ю щ н и с я тем, что, с целью расширения области применения за счет реализации модулем возможности адаптации к решаемой задаче,. в него введены первая и вторая группы элементов 2И-ИЛИ-НЕ по четыре элемента в каждой, элемент НЕ, первый и второй блоки памяти, группы информационных входов, первые груп- пы адресных входов и входы разрешения записи которых соединены соответственно с группой информационных входов, с группой входов управления и с управляющим входом модуля, вторые группы адресных входов первого и второго блоков памяти подключены соответственно к выходам элементов. 2ИИЛИ-НЕ первой и второй групп, первые информационные выходы первого и второго блоков памяти соединены соответственно с первым входом первого элемента 2И-ИЛИ-НЕ второй группы и с выходом переноса модуля, второй информационный выход первого блока памяти соединен с информационным входом первого триггера и с первым асинхронным выходом данных модуля, второй информационный выход второго блока памяти соединен с информационным входом второго триггера и с вторым асинхронным выходом данных модуля, первый вход первого элемента 2И-ИЛИ-НЕ первой группы соединен с входом переноса модуля, первые входы вторых элементов 2И-ИЛИ-НЕ первой н второй групп соединены соответственно с первым и вторым входами данных модуля, первый вход третьего элемента 2И-ИЛИ-НЕ первой группы соединен с выходом первого триггера, с выходом переноса вправо модуля и с первым синхронным входом данных модуля, первый вход третьего элемента 2Й-ИЛИ-HE второй группы соединен с первым входом четвертого элемента 2И-ИЛИ-НЕ первой группы, с выходом второго триггера и с вторым синхронным выходом данных модуля, первый вход четвертого элемента 2И-ИЛИ-НЕ второй группы соединен с входом переноса вправо модуля, вторые входы первых, вторых, третьих и четвертых элементов 2И-ИЛИ-НЕ первой и второй групп соединены соответственно с первым, вторым, третьим и четвертым входами настройки модуля, третьи входы всех элементов 2И-ИЛИ-HE соединены с выходом элемента НЕ, вход которого соединен с четвертыми входами всех элементов 2И-ИЛИ-НЕ и с входом управления режимом модуля.

1083198

Изобретение относится к вычислительной технике и может найти применение при построении специализирован ных и универсальных ЭВМ.

Известен микропроцессорный модуль, содержащий регистр-аккумулятор, четы- 5 ре группы шин управления, входные и выходные шины данных и функционального переноса направо и налево, а также шину тактовых импульсов (1 3.

Недостатком данного модуля являет 10 ся широкое поле управления микрооперацией.

Наиболее близким к предлагаемому по технической сущности является микропроцессорный модуль, содержащий 15 первый и второй триггеры, входы синхронизации которых соединены с шиной тактовых импульсов, четыре мультиплексора, первая группа шин управления соединена с информационными входами первого мультиплексора, первый управляющий вход которого соединен с первым управляющим входом второго мультиплексора, второй управляющий вход которого соединен с входной шиной переноса и вторым управляющим входом первого мультиплексора, третий управляющий вход которого соединен с первой входной шиной данных и третьим управляющим входом второго мультиплексора, четвертый управляющий вход которого соединен с выходной шиной обратной связи, первой выходной шиной данных, выходом триггера нулевого разряда и четвертым управляющим входом первого мультиплексора, выход 35 которого соединен с первой выходной шиной переноса, вторая выходная шина переноса соединена с выходом третьего мультиплексора, первый управляющий вход которого соединен с вход- 4g ной шиной обратной связи и первым управляющим входом четвертого мультиплексора, второй управляющий вход которого соединен с первой выходной шиной переноса и вторым управляющим входом третьего мультиплексора, третий управляющий вход которого соединен с второй входной шиной данных и третьим управляющим входом четвертого мультиплексора, четвертый управляющий вход которого соединен с выходом первого триггера, второй вы-. ходной шиной данных и первым управляющим входом первого мультиплексора, информационные входы которого соединены с первой группой шин управле- 55 ния, информационные выходы второго и четвертого мультиплексоров соединены соответственно с D -входами первого и второго триггеров, первая и вторая асинхронные шины данных сое- Щ динены соответственно с 5 -входами первого и второго триггеров (2 j.

Недостатком известного модуля является невозможность адаптации к решаемой задаче. 65

Цель изобретения — расширение области применения модуля за счет реализации им возможности адаптации к решаемой задаче и выполнения различных операций в разных разрядах.

Поставленная цель достигается тем, что в операционный модуль, содержащий первый и второй триггеры, входы синхронизации которых подключены к входу синхронизации модуля, введены первая и вторая группы элементов

2И-ИЛИ-НЕ по четыре элемента в каждой, элемент НЕ, первый и второй блоки памяти, группы информационных входов, первые группы адресных входов и входы разрешения записи которых соединены соответственно с группой информационных входов, с группой входов управления и с управляющим входом модуля, вторые группы адресных входов первого и второго блоков памяти подключены соответственно к

ыкодам элементов 2И-ИЛИ-НЕ первой и второй групп, первые информационные выходы первого и второго блоков амяти соединены соответственно с первым входом первого элемента

2И-ИЛИ-НЕ второй группы и с выходом . переноса модуля, второй информационный выход первого блока памяти соединен с информационным входом первого триггера и с первым асинхронным выходом данных модуля, второй информационный выход второго блока памяти соединен с информационным входом второго триггера и с вторым асинхронным выходом данных модуля, первый вход первого элемента 2И-ЙЛИ-НЕ первой группы соединен с входом переноса модуля, первые входы. вторых элементов 2И-HJIH-НЕ первой и второй групп соединены соответственно с первым и вторым входами данных модуля, первый вход третьего элемента 2ИИЛИ-НЕ первой группы соединен с выходом первоЪ"о триггера, с выходом переноса вправо модуля и с первым синхронным входом данных модуля, первый вход третьего элемента 2ЙИЛИ-НЕ второй группы соединен с пер-. вым входом четвертого элемента 2ИИЛИ-НЕ первой группы, с выходом вто,рого триггера и с вторым синхронным выходом данных модуля, первый вход четвертого элемента 2Й-ИЛИ-НЕ второй.группы соединен с входом переноса вправо модуля, вторые входы первых, вторых, третьих и четвертых элементов 2Й-ИЛИ-НЕ первой и второй групп соединены соответственно c первым, вторым, третьим и четвертым входами настройки модуля, третьи входы всех элементов 2И-ИЛИ-НЕ соединены с выходом элемента НЕ, вход которого соединен с четвертыми входами всех элементов 2И-ИЛИ-НЕ и с входом управления режимом модуля.

10831 98

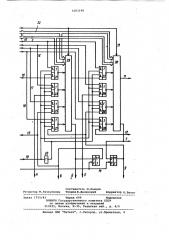

На чертеже изображена схема предлагаемого модуля.

Операционный модуль содержит первый 1 и второй 2 триггеры, группу входов 3 управления, первый 4 и второй 5 входы данных, первый 6 и вто- 5 рой 7 асинхронные выходы данных, первый 8 и второй 9 синхронные выходы данных, вход 10 и выход 11 пере-. носа, вход 12 и выход 13 переноса вправо, вход 14 синхронизации, четы- 10 ре входа 15-18 настройки, вход 19 управления режимом, элемент HE 20, восемь элементов 2Й-ИЛИ-НЕ 21-28, два блока 29 и 30 памяти, вход 31 разрешения записи и группу информа- 15 ционных входов 32..

Операционный модуль, предназначенный для реализации арифметико-логических операций, работает следующим образом. 20

Двоичный код, подаваемый по группе входов 3 управления, определяет вид микрооперации, реализуемой иад . двумя операндами, один из которых находится в триггерах 1 и 2, а дру» гой-- на входах 4 и 5 данных. Количество входов управления определяется двоичным логарифмом количества микроопераций, выбранных иэ aeего множества возможных микроопераций для решения данной задачи. Для прдготовки микропроцессорного модуля к реализации выбранного набора микро операций служит режим настройки, определяемый значением сигнала на входе 19 управления режимом. B этом режиме вторая группа адресных входов блоков 29 и 30 памяти соединяется через элементы 2И-ИЛИ-НЕ 21,23,25, 27 и 22,24,26,28 с выходами 15,16 и 17,18 настройки соответственно. 40

Для настройки операционного моду- . ля для реализации некоторой заданной микрооперации на группе входов 3 управления устанавливается код этой микрооперации, а на входах 15-18 настройки — один иэ возможных наборов значений операндов, переноса и сдвига вправо соединяется с микрооперации. При -этом на вход 15 подается сигнал, представляющий собой в режиме настройки значение переноса, на вход 16 — значение разряда вход« його операнда, на вход 17 — значение триггеров 1 и 2, а на вход 18значение переноса вправо. Одновременно на одной и другой парах разрядов группы информационных входов 32 устанавливаются значения результатов операций в соответствующих разрядах устройства и переноса в следующие разряды. После установки всех этих 60 данных на вход 31 разрешения записи поступает сигнал, производящий запись полученной информации в блоки 29 и 30 памяти. Аналогичным обра-. зом осуществляется настройка опера 65 ционного модуля при всех возможных наборах значений операндов и переносов для всего выбранного множества микроопераций.

После настройки операционный модуль изменением сигнала.на входе 19 управления режимом переводится в режим вычисления. В этом режиме вторая группа адресных входов блоков 29 и 30 памяти соединяется соответствующи1 ми выходами триггеров 1 и 2, входами 4 и 5 данных и входами 12 и 10 переносов. При этом на вторых выходах блоков 29 и 30 памяти и на асинхронных выходах 6 и 7 данных в соответ-, ствии с заданной на группе входов 3 управления микрооперацией формируется результат выполнения микрооперации в соответствующем разряде, а на первых выходах - значение сигналов переноса. Значение сигнала переноса с первого выхода блока 30 памяти поступает на выход 11 переноса. Таким образом, значение результата в данном разряде и перенос в следующий разряд при заданной микрооперации являются. произвольными педеключательными функциями четырех аргументов: сигнала на входе 4 или 5 данных соответствующего разряда, выходного сигнала соответствующего ра зряда, сигнала переноса, поступающего по входу 10 переноса или с первого выхода блока 29 памяти и сигнала переноса вправо,посту пающего с выхода второго или по входу 12 переноса вправо.

По фронту тактового импульса, поступающего по входу 14 синхронизации на вход синхронизации триггеров

1 и 2, происходит запись результата микрооперации с асинхронных выходов

6 и 7 данных в триггеры 1 и 2. Этот результат поступает на,синхронные выходы 8 и 9 данных. Одновременно сигнал с выхода первого -триггера 1 поступает на выход 13 переноса вправо. Результат, записанный в триггеры 1 и 2, остается неизменным до прихода фронта следующего тактового импульса.

Для реализации другого подмножества микроопераций должен быть повторен процесс настройки °

Таким образом, в предлагаемом модуле реализуется возможность адаптации к решаемой задаче путем прове« дения соответствующей нас=ройки определенной системы микрокоманд, а также предусмотрена возможность выполнения различных операций в разных разрядах.

Реализация таких воэможностей позволяет расширить область применения предлагаемого модуля. Так, например, на его базе можно построить многоразрядный адаптивный процессор с изменяющимся в процессе вычислений набором реализуемых микроопераций.

1083198

Составитель l0.Ëàíöîs

Редактор М. Рачкулинец Техред В.Далекорей Корректор О, Вилак

Заказ 1755/43 Тираж 699 Подлисное

BHHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, E-35, Рауыская наб., д. 4/5

Филиал ППП "Патент", r.Óæãoðîä, ул.Проектная, 4