Устройство подавления помех

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ПОДАВЛЕНИЯ ПОМЕХ, содержащее Ы линий задержки, N-1 ne- ремножителей, N-1 элементов памяти, выход каждого из которых подключен к первому входу соответствующего пе ремножителя , выходной сумматор, первый вход которого объединен с входом первой линии задержки и является входом устройства, другие входы подключены к выходам соответствуюпщх перемножителей, а выход является выходом устройства, а также ключ и обнаружитель помехи, о т л и ч аю щ е е с я тем, что., с целью повьпиения эффективности подавления помехи, в него введены N сумматоров , при этом первый вход -i -го сумматора (где 1,2,...,К-1) подключен к выходу 1 -и линии задержки, выход - к второму входу г-го перемножителя и к входу ( 1+1)-й линии задержки, первый вход N-ro сумматора соединен с выходом N-й линии задержки, а выход - с дополнительным входом выходного сумматора, вход обнаружителя объединен с информационным входом ключа и подключен к сл входу устройства, а выход - к управляющему входу ключа, выход которого соединен с вторыми входами N сумматоров .

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТ ИЧЕСНИХ

РЕСПУБЛИН

3(5ll Н 04 В 1/10

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬП И (21) 3386628/18-09 (22) 06.01.82 (46) 30.03.84. Бюл. У 12 (72) С.В. Гуськов и Д.И. Попов (71) Рязанский радиотехнический институт (53).621.396.662(088 ° 8) (56) Zverev А.I. Digita 3 MTI Radar

Filters. IEEE Trans. 1968, v. Ац-16, У 3, р. 430, fig,13 (прототип). (54)(57) УСТРОЙСТВО ПОДАВЛЕНИЯ ПОМЕХ, содержащее Й линий задержки, N 1 пе ремножителей, М -1 элементов памяти, выход каждого из которых подключен к первому входу соответствующего перемножителя, выходной сумматор, первый вход которого объединен с входом первой линии задержки и является входом устройства, другие входы подключены к выходам соответствую„„SU„„108 367 А щих перемножителей, а выход является выходом устройства, а также ключ и обнаружитель помехи, о т л и ч аю щ е е с я тем, что, с целью повышения эффективности подавления помехи, в него введены М сумматоров, при этом первый вход 1 -го сумматора (где i = 1,2,..., й-1) подключен к выходу 1 -й линии задержки, выход — к второму входу i --ro перемножителя и к входу (+1)-й линии задержки, первый вход Й-го сумматора соединен с выходом М-й линии задержки, а выход — с дополнительным входом выходного сумматора, вход обнаружителя объединен с информационным входом ключа и подключен к входу устройства, а выход - к управляющему входу ключа, выход которого соединен с вторыми входами .М сумматоров.

1083367

Изобретение относится к радиотехнике и может быть использовано в устройствах когерентной обработки сигналов на фоне коррелированных помех.

Наиболее близким по технической сущности к предлагаемому является устройство подавления помех, содержащее М линий задержки, N -1 весовых блоков, сумматор, обнаружитель по- 10 мехи, ключ и синхрогенератор и предиаэначенное для подавления узкополосных коррелированных помех, нротяженных по азимуту и дальности и сосредрточенных по спектру, в качестве которых могут выступать, например, отражения от земной поверхности, местных предметов и т.п. (1 g.

В указанном устройстве полезный сигнал от цели и помеха перекрываются по времени, т.е. расположены в од ном элементе разрешения по дальнос- ти, уровень помехи значительно превышает уровень сигнала, а отличия 25 между ними спектральные. Устройство подавления помех формирует амплитудно-частотную характеристику (АЧХ) таким образом, что спектр помеховой последовательности попадает в зону резекции АЧХ, спектр сигнала — в зону прозрачности АЧХ.

Вхождение кромки от помех на вход известного устройства является наиболее неблагоприятным моментом в про35 цессе обработки. Пока отсчеты помехи не заполнят все элементы задержки, на выходе устройства. наблюдается переходный процесс: нескомпенсированные остатки помехи на выходе сумматора создают мощный фон и маскируют полезный сигнал. Таким образом, устройство подавления помех оказывается неэффекимвным на кромке помехи.

Цель изобретения — повышение эф45 фективности подавления помех.

Для этого в устройство подавления помех, содержащее М линий задержки,, й-1 неремножителей, И -1 элементов .памяти выход каждого из которых

Э

50 подключен к первому входу соответствующего перемножителя, выходной сумматор, первый вход которого объединен с входом первой линии задержки и является входом устройства, дру 55 гие входы подключены к. выходам соответствующих перемножителей, а выход является выходом устройства, а также ключ и обнаружитель помехи, вве2 дены 1 1 сумматоров, при этом первый вход j-го сумматора (где

1,2,...,М-1) подключен к выходу

1-й линии задержки, выход — к второму входу i-ro перемножителя,и к входу (i +t)-й линии задержки, первый вход М -го сумматора соединен с выходом М -й линии задержки, а выход - с дополнительным входом выходного сумматора, вход обнаружителя объединен с информационным входом ключа и подключен к входу устройства, а выход — к управляющему входу ключа, выход которого соединен с вторыми входами М сумматоров.

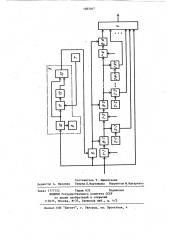

На чертеже представлена структурная электрическая схема устройства подавления помех.

Устройство подавления помех содержит линии задержки 1-1 — 1- й, элементы памяти 2-1 — 2-М-1, перемножители 3-1 — 3-N-1; выходной сумматор 4, обнаружитель 5 помехи, ключ

6, синхрогенератор 7, сумматоры

8-1 — &-N. Обнаружитель 5 помехи содержит элемент 9 памяти, компаратор 10, линию 11 задержки, инвертор 12 и логический элемент 13.

Устройство работает следующим образом.

При совпадении положения антенного луча в процессе сканирования (непрерывного или дискретного) с кромкой облака пассивных помех обнаружитель 5 помехи вырабатывает единичный потенциал и ключ б, находящиися s разомкнутом состоянии, замыкается. Отсчет первого отраженного импульса поступает на вход первой линии 1-1 задержки и одновременно через ключ 6 и сумматоры 8-1

8-N на входы последующих линий

1-2 — 1-N задержки. К моменту поступления отсчета второго отраженного импульса обнаружитель 5 помехи размыкает ключ 6 до тех пор, пока не начнут поступать отражения от другого источника коррелированных помех, при этом обработка отсчетов смеси сигналов и помех происходит обычным образом: отсчеты последовательно поступают на линии 1-1 - И- задержки и на перемножители 3-1

З-N-1.

На выходе выходного сумматора 4 в момент прихода первого отсчета отражений ст помех образуется величина, эквивалентная величине первого отсчета, помноженной на коэффициент

10833

3 передачи устройства на нулевой до— плеровской частоте в установившемся состоянии. После прихода второго . отсчета на выходе устройства образуется величина смеси сигналов и декоррелированных за один период остатков помехи, после прихода третьего отсчета — величина смеси сигналов и декоррелированных за два периода остатков помех, после прихода (11 +1)-го отсчета — величина смеси сигналов и декоррелированных за М периодов остатков помех.

К моменту прихода (М +2)-го отсчета переходный процесс на выходе фильтра закончен, а выходная величина принимает установившееся значение.

Таким образом, эффективность выделения сигналов на фоне отражений от помех в переходном режиме нарастает последовательно от импульса к импульсу до установления процессов, когда эффективность достигает максимальной величины. При этом уже в момент поступления первого отсчета отражений от помех достигается компенсация постоянной составляющей выборки помех (протяженной или точечной), а эффективность компенсации низкочастотных составляющих в целом sa время пере:ходного режима постоянно растет.

Синхронное тактирование информации по кольцам дальности в линиях

1-1 -1-N . .задержки, а также в узлах

35 .радиолокационной системы в целом

Е7 обеспечивает сннхрогенератор 7, вырабатывающий последовательность синхроимпульсов U,„ с периодом Т>.

С выхода компаратора 10 (БВ„,„ 1.

ВЫХ о единичные потенциалы, соответствующие отражениям от помех U „ в определенных кольцах дальностй, постуВх5 пают в каждом периоде зондирования на вход линии 11 задержки (задержка производится на интервал Т„) и на второй вход логического элемента

13, выполняющего функцию логического перемножения. В первый момент появления единичных потенциалов на вы- ходе компаратора 10, на выходе линии 11 задержки (УВык будут прису

1 вовать нулевые потенциалы, на выходе инвертора 12 — соответственно единичные потенциалы БВц „ . В результате

12 на выходе логического элемента 13 тоже будут присутствовать единичные потенциалы УВЬ 1в первом периоде присутствия помехи. В следующем периоде (t = Т вЂ” 2Т ) на выходе инП h вертора 12 образуются нулевые потенциалы, запирающие логический элемент 13 на все остальные время действия помех в соответствующих кольЪ цах дальности и срабатывание ключа

6 происходит только в первом периоде действия помех (t = 0 — т„).

Таким образом, в устройстве осуществляется повышение эффективности подавления помехи в переходном режиме sa счет введения сумматоров и наличия новых связей между элементами.

1083367

Составитель Т. Афанасьева редактор А. Фролова Техред Л.Иартяшова Корректор Ю.Иакаренко

l г

Заказ 1777/52 Тираж 635 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4