Устройство синхронизации двоичных сигналов в приемной аппаратуре многоканальной системы связи

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО СИНХРОНИЗАЦИИ ДВОИЧНЫХ СИГНАЛОВ В ПРИЕМНОЙ АППАРАТУРЕ МНОГОКАНАЛЬНОЙ СИСТЕМЫ СВЯЗИ, содержащее на входе последовательно соединенные линию задержки с отводами , блок определения фронтов и блок подсчета фронтов, о т л ичающееся тем, что, с целью повышения помехоустойчивости без применения специальных сигналов и в режиме частого изменения условий связи, в него введены последовательно соединенные блок вьфаботки оценок качества.синхронизации, форми:рователь сброса, блок запоминания ф&зы и формирователь синхросигнала, а также кольцевой коммутатор, выходы 1i разрядов которого подсоединены к соответствующим входам формирователя сброса, а вход первого разряда кольцевого коммутатора подсоединен к шине Начало работы, при этом первый и последний выходы блока определения фронтов подсоединены к соответствующим входам блока вьфаботки оценок качества синхронизации, к другому входу которого подключен выход блока подсчета фронтов, причем тактовые входы линии задержки @ с отводами, блока подсчета фронтов, блока выработки оценок, кольцевого коммутатора и формирователя сброса объединеныи подключены к шине тактовой частоты, опорный вход блока запоминания фазы подключен к шине опорной частоты, а установочный вход блока подсчета фронтов подклюэо чен к шине установки. : : X) ;о

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) ((ll.

SU (1ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И ABTOPCHOMV СВИДЕТЕЛЬСТВУ I

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3358363/18-09 (22) 26. 11. 81 (46) 30. 03. 84. Бюл.11912 (72) Н.Н. Дунева, М.С. Поддубный, В.А. Поставский и В.Л. Хазан (53) 621.394.662(088.8) (56),1. Авторское свидетельство СССР

119 849521., кл. Н 04 1- 7/08, 1978.

2. Мешковский К.А. Теория и техника помехоустойчивого кодирования.

Тема 7; с.54, рис.7.1 (прототип). (54)(57) УСТРОЙСТВО СИНХРОНИЗАЦИИ

ДВОИЧНЫХ СИГНАЛОВ В ПРИЕМНОЙ АППАРАТУРЕ МНОГОКАНАЛЬНОЙ СИСТЕМЫ СВЯЗИ, содержащее на входе последовательно соединенные линию задержки с отво- дами, блок определения фронтов и блок подсчета фронтов, о т л и ч а ю щ е е с я тем, что, с целью повьппения помехоустойчивости без применения специальных сигналов и в режиме частого изменения условий связи, в него введены последователь1 но соединенные блок выработки оце350 Н 04 1„7/02, Н 04 3 3/06

Н 04 L, 7/08 .(нок качества.синхронизации, форми.рователь сброса, блок запоминания фазы и формирователь синхросигнала, а также кольцевой коммутатор, выходы К разрядов которого подсоединены к соответствующим входам формиро" вателя сброса, а вход первого разряда кольцевого коммутатора подсоединен к шине "Начало работы", при этом первый и последний выходы блока определения фронтов подсоединены к соответствующим входам блока выработки оценок качества синхронизации, к другому входу которого подключен выход блока подсчета фронтов, причем тактовые входы лннии задержки с отводами, блока подсчета фронтов, блока выработки оценок, кольцевого коммутатора и формирователя сброса объединены.и подключены к шине тактовой частоты, опорный вход блока .запоминания фазы подключен к шине опорной частоты, а установочный вход. блока подсчета фронтов подключен к шине установки.

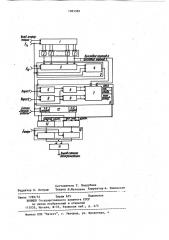

На чертеже представлена структурная электрическая схема предлагаемого устройства.

Устройство синхронизации двоичных сигналов в приемной аппаратуре многоканальной системы связи содержит линию 1 задержки с отводами, блок 2 определения фронтов, состоящий из полусумматоров, блок 3 подсчета фронтов, содержащий счетчик 4 и параллельно-последовательный регистр 5, блок 6 выработки оценок качества синхронизации, содержащий дешифратор 1, последовательный регистр 8 и пороговые элементы 9, блок 10 запоминания фазы, состоящий из к делителей частоты, формирователь 11 синхросигнала, кольцевой коммутатор 12 и формирователь

13 сброса.

Устройство работает следующим образом.

При поступлении на вход линии 1 задержки уплотненного во времени сигнала, несущего информацию о всех

К принимаемых параллельно сообщениях, в определенной части блока 2 в соответствии с видом кодовых комбинаций фиксируются фронты принятых посылок.

При этом на выходах блока 2 появляются импульсы, совпадающие во времени, только для каждого корреспондента в отдельности.

1 10833

Изобретение относится к технике телеграфной связи и.может использоваться для синхронного приема дискретной информации при работе совокупности демодуляторов в многоканальной системе связи.

Известно устройство для цикловой синхронизации, содержащее объединенные по входу регистр задержки и блок обнаружения ошибок, выход которого подключен к дешифратору, счетчик, коммутатор, k-1 счетчиков, порого-. вый блок, генератор импульсов и сумматор, причем блок обнаружения ошибок выполнен в виде двух последовательно соединенных фильтров Хаффсиена и регистра, другой выход блока обнаружения ошибок через коммутатор . подключен к входам k счетчиков, выходы которых через последовательно соединенные пороговый блок и генератор импульсов подключены к входу сумматора, другой вход которого соединен с выходом регистра задержки, а выход дешифратора подключен к дру- 25 гому входу коммутатора (1 ).

Однако для функционирования данного устройства для цикловой синхронизации необходима специальная синхропоследовательность.

Наиболее близким к предлагаемому является устройство синхронизации двоичных сигналов в приемной аппаратуре многоканальной системы связи, содержащее на входе последовательно соединенные линию задержки с отвода- З5 ми, блок определения фронтов и блок подсчета фронтов, при этом выход блока подсчета фронтов подсоединен к пороговому блоку 2 ).

В известном устройстве для осущест40 вления приема необходимо включать специальную синхропоследовательность.

Кроме того, при возможных скачках фазы радиолинии., переходе с луча на луч или перерывах связи этот принцип 45 не обеспечивает достаточно высокую помехоустойчивость, Цель изобретения — повышение помехоустойчивости без применения специальных сигналов и в режиме частого изменения условий связи.

Поставленная цель достигается тем, . что в устройство синхронизации двоичных сигналов в приемной аппаратуре многоканальной системы связи, со- 55 дерЖащее на входе последовательно соединенные линию задержки с отводами, блок определения фронтов и блок

89 2 подсчета фронтов, введены последовательно соединенные блок выработки оценок качества синхронизации, формирователь сброса, блок запоминания фазы и формирователь синхросигнала, а также кольцевой коммутатор, выходы

k-разрядов которого подсоединены к соответствующим входам формирователя сброса, а вход первого разряда кольцевого коммутатора подсоединен к шине "Начало работы", при этом первый и последний выходы блока определения фронтов подсоединены к соответствующим входам блока выработки оценок качества синхронизации, к другому входу которого подключен выход блока подсчета фронтов, причем. тактовые входы линии задержки с отводами, блока подсчета фронтов, блока выработки оценок, кольцевого коммутатора и формирователя сброса объединены и подключены к шине тактовой .частоты, опорный вход блока запоминания фазы подключен к шине опорной частоты, а установочный вход блока подсчета фронтов подключен к шине установки. з 1083389 4 работы линии зультате анализа всех поступивших

t1 вляется параллель- на его вход сигналов дешифратор 7 пульсов в параллель- на одной из выходных шин формирует и регистр 5 и затем импульсы оценок качества синхроние продвижение на зации (" Отлично", "Хорошо", "Удовлет.5 ворительно"), которые подаются на та последова- формирователь 13 сброса. По каждому

t2 ого регистра 5 опре- из выходов формируется сигнал наия Е ъ а тй т . чальной установки фазы того делиное количество фрон- щ теля частоты блока 10, номер котоовой комбинаций. рого соответствует разряду кольVnk < цевого коммутатора 12. Тактовая ть телеграфирования, частота продвижения сигналов в кольцевом коммутаторе отсчетов на длитель-1 В основу работы формирователя элементарной посылки 13 сброса заложен принцип приоритеветствии с выбранной та лучшей оценки качества синхронитью синхронизации; зации. Реализация схемы приоритета обслуживаемых ка- такова, что в момент выработки сигналов цикловой и тактовой синчетчиком 4 количест- хронизации осуществляется запомик в кодовой комби- канне оценок их качества в элементах ним из компонентов, памяти (триггерах). При этом выходы оценки достовер- запоминающих триггеров скоммутиромого в дальнейшем 25 ваны через схемы совпадения таким ифровой код количест- образом, что при поступлении сигналов ализируемой кодо- синхронизации с оценкой качества выхода счетчика 4 ниже, чем ранее запомненные, послед пороговых элемен- ние не пропускаются на выход форми- одит его сравне- З0 рователя 13 сброса, вследствие чего ед заданными чис- при ухудшении условий связи или даже

При этом величина, частичных перерывах в работе, когда ся исходя из сред- оценки качества сигналов синхронила фронтов на дли- эации имеют тенденцию к снижению, выработанные в этих .условиях сигналы теризовать ее по . сброса не имеют возможности пере35 дов. Величина по . Установить Ранее запомненные (в хо-, что позволяет . Роших условиях) фазы делителей частоты что позволяет

I свой комбинации Выходы К делителей частоты блока

10 подключены к соответствующим вхо40 в наиболее поме- дым фоРмиРователя 11, котоРый фории ней части посылок рует сигналы цикловой и тактовой синхронизации для работы оконечной

45 э аппаратуры, На каждом такте

1 задержки осущест ная запись этих им но-последовательнь их последовательно вход счетчика 4.

Тактовая часто тельно-параллельн деляется из услов где (и .- максималь тов посылок в код 1 где V — скор ос

Вод; и — число ности в соот точнос

% — число налов.

Подсчитанное с во фронтов посыло нации является од используемых для ности вырабатывае сигнала сброса. U ва переходов в ан вой комбинации с подается на входь тов 9, где происх ние с двумя напер ловыми порогами. порога 1 выбирает него значения чис не кодовой комбин возможность харак количеству перехо рога 2 равна нулю обнаружить даже о в любом месте код и за счет этого о сутствие просечек хоустойчивой сред

Сигналы с выхо ментов записывают тельные регистры 8, имеющие инфор-.. мационную емкость .пМ . С выходов последовательных регистров 8, взятых через 1с разрядов, сигналы поступают на входы дешифратора 7. Сюда же подаются сигналы с выходов тех полусумматоров блока 2, которые фиксируют наличие в кодовой комби-. нации цикловых переходов. В реТехнико-экономическая эффективность изобретения заключается в возможности повышения помехоустойчивости приема дискретных сообщений при час» тых изменениях условий связи и кратковременных перерывах в работе, а также без применения специальных синхросигналов.

1083389

8а6 инррющии

frf

Etf8HO .На в фУ УМ

Составитель Т. Поддубняк

Редактор В. Петраш Техред И.Метелева Корректор А. Зимокосов

Заказ 1789/53 Тираж 635 Подписное

ВНИИПИ Государственного комитета СССР ло делам изобретений и открытий

1 13035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4